A Unified Colorer Array Multi-warp Instruction Fetch Circuit

A dyer and array technology is applied in the field of multi-warp finger fetch circuits in a unified dyer array, which can solve the problem of idle computing components, and achieve the effects of ensuring validity, flexible initial addresses, and simple fetch circuits and methods.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

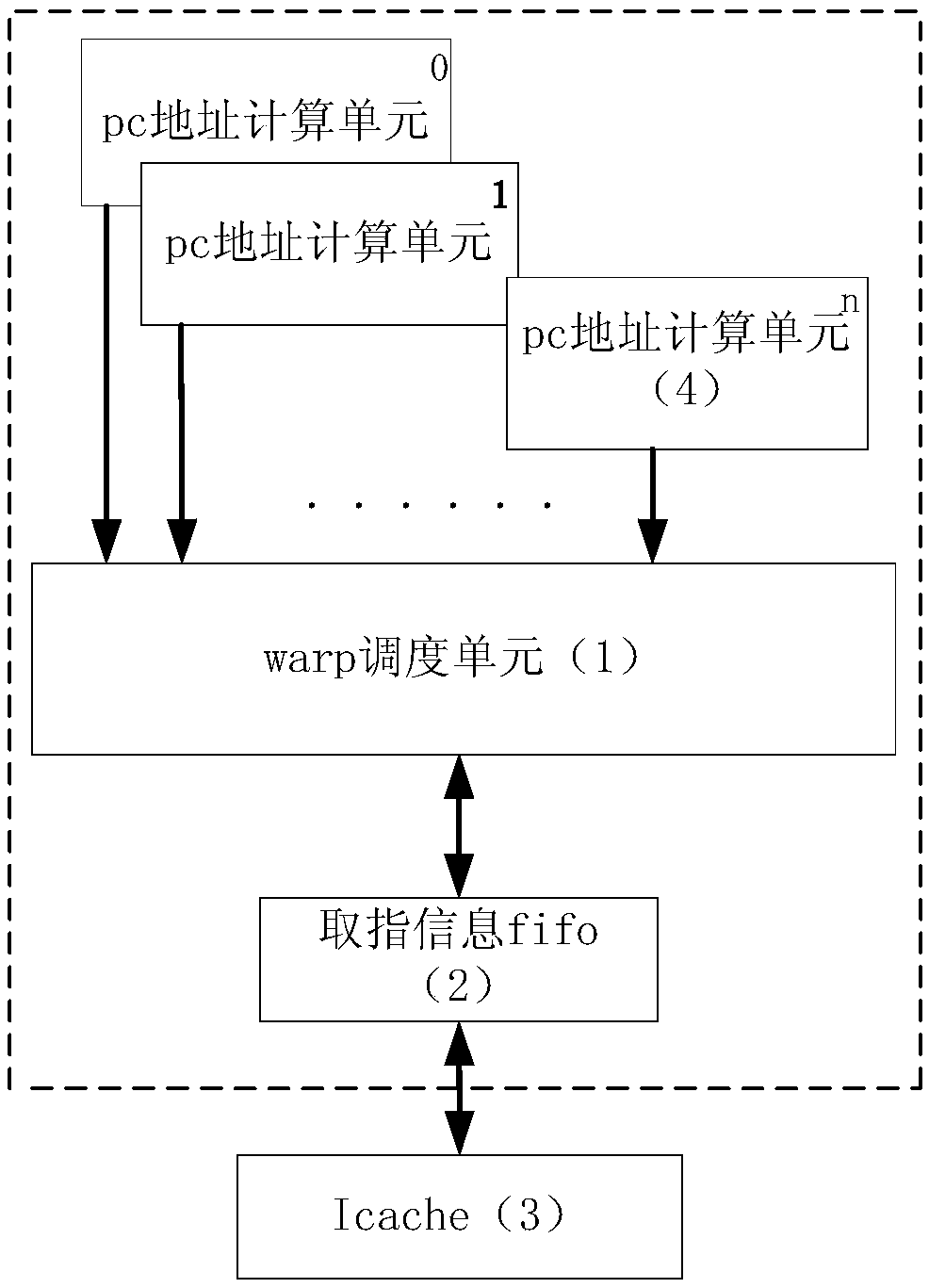

[0061] like figure 1 As shown, a unified dyer array multi-warp instruction fetch circuit and method, including 8 warp pc address calculation unit, warp scheduling unit, instruction fetch information fifo and external icache.

[0062] The specific structure and function of each module are introduced in detail below:

[0063] The instruction fetch circuit includes 8 warps, each warp corresponds to a pc address calculation unit, and each warp has an independent instruction fetch pc address and a warp pc stack (which is used to realize the pc address when function nesting Save and restore), the size of each instruction fetch is 8 instructions, and each warp has a 2-line buffer cache;

[0064] The pc address calculation unit is used for calculating the warp pc address, and generates schedulable warp requests and warp pc addresses to the warp scheduling unit;

[0065] Among them, the schedulable warp request generation conditions are as follows:

[0066] 1) The warp cache can be ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com