Method and device for generating RTL (Register Transfer Logic)-level IP (Intellectual Property) core

A nuclear method and nuclear device technology, applied in the field of RTL-level IP core method and device generation, can solve the problems of reducing area and failing to guarantee comprehensive performance, and achieve the effect of reducing area and ensuring comprehensive performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

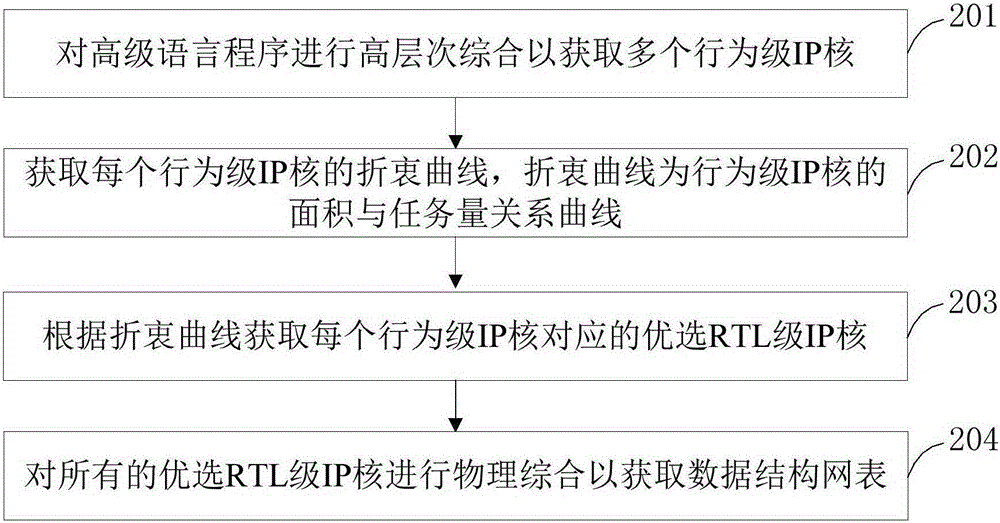

[0029] figure 2 The implementation process of the method for generating an RTL-level IP core provided by this embodiment is shown. For the convenience of description, only the parts related to this embodiment are shown, and the details are as follows:

[0030] In step 201, a high-level synthesis is performed on the high-level language program to obtain multiple behavior-level IP cores.

[0031] In step 202, a trade-off curve of each behavior-level IP core is obtained, and the trade-off curve is a relationship curve between the area of the behavior-level IP core and the amount of tasks. Among them, the task amount is the derivative of the delay.

[0032] In specific implementation, step 202 can be divided into the following three sub-steps:

[0033] A. Configure multiple restriction files. Wherein, the sub-step of configuring multiple restriction files is specifically: configuring multiple restriction files according to reducing the number of functional device restriction...

Embodiment 2

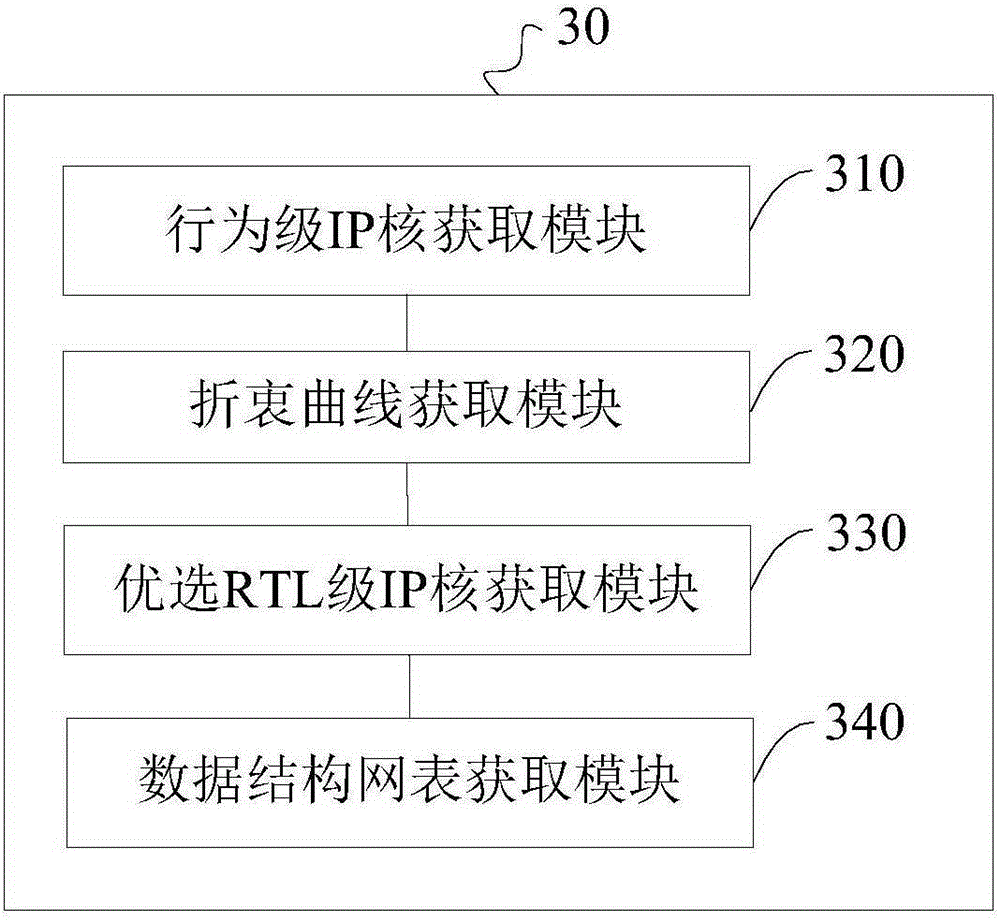

[0049] Embodiment 2 of the present invention provides a device for generating an RTL-level IP core, such as image 3 As shown, a device 30 for generating an RTL-level IP core includes a behavior-level IP core acquisition module 310 , a compromise curve acquisition module 320 , a preferred RTL-level IP core acquisition module 330 and a data structure netlist acquisition module 340 .

[0050] The behavior-level IP core acquisition module 310 is configured to conduct high-level synthesis of high-level language programs to obtain multiple behavior-level IP cores.

[0051] The trade-off curve obtaining module 320 is configured to obtain a trade-off curve of each behavior-level IP core, where the trade-off curve is a relationship curve between the area of the behavior-level IP core and the amount of tasks.

[0052] The preferred RTL-level IP core acquisition module 330 is configured to acquire the preferred RTL-level IP core corresponding to each behavioral-level IP core according...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More