A kind of fpga chip wiring method

A wiring method and wiring technology, applied in the direction of instruments, calculations, electrical digital data processing, etc., can solve the problem of not increasing the wiring speed, and achieve the effect of reducing time delay and improving wiring speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018]In order to make the objects, technical solutions, and advantages of the present invention more clearly, the technical solutions in the embodiments of the present invention will be described in contemplation in the embodiments of the present invention, and will be described, and the embodiments described in the embodiments of the present invention will be described. It is a part of the embodiments of the present invention, not all of the embodiments.

[0019]The embodiment of the present invention provides an FPGA chip wiring method, which analyzes the wiring module characteristics of the FPGA chip architecture to improve the wiring speed and reduce the delay of the time.

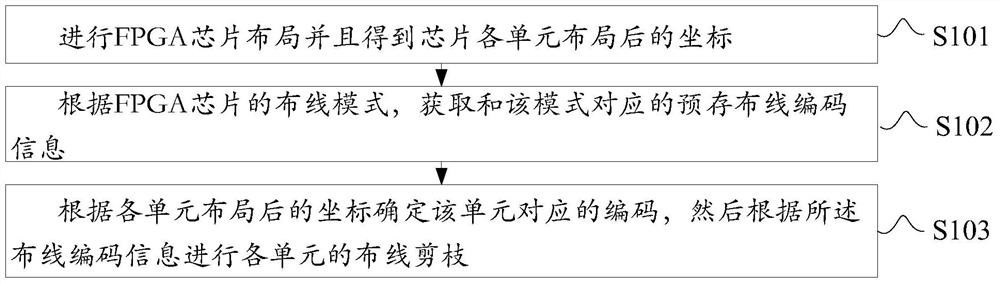

[0020]figure 1 A method of fpga chip wiring method according to an embodiment of the present invention is shown. Such asfigure 1 As shown, an FPGA chip wiring method includes steps S101-S103:

[0021]Step S101: Perform the FPGA chip layout and obtain coordinates after the layout of each unit of the chip;

[0022]Specif...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More