Master control terminal, device terminal and method and system for transmitting multichannel audio data

A technology of audio data and main control terminal, which is applied in the directions of speaker distribution signal, electrical components, signal processing, etc., which can solve the problems of high hardware cost and high difficulty of I2S interface design.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

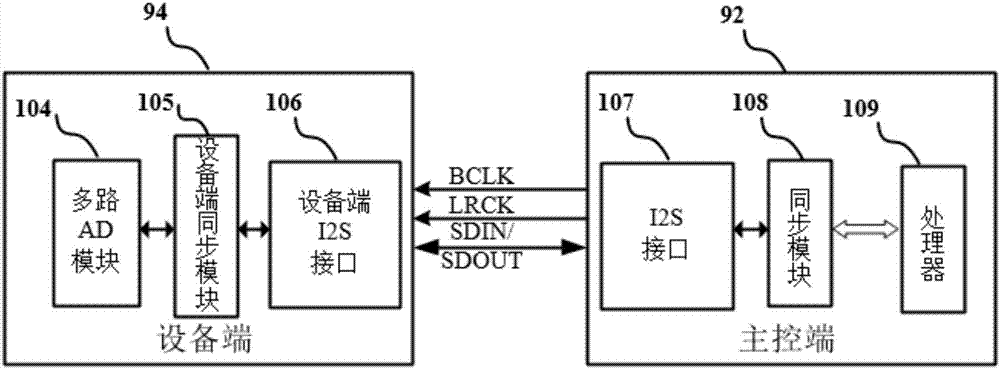

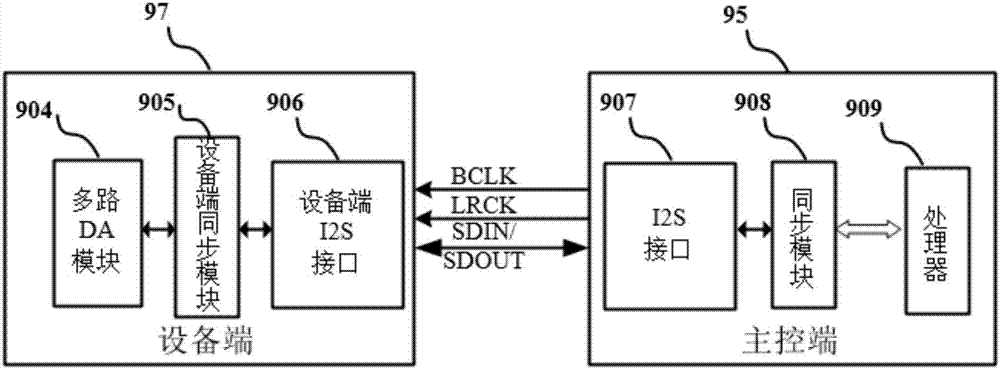

[0100] Figure 4 Shown is a functional block diagram of the master control end of an embodiment of the present invention, in this embodiment, the master control end 30 and the device end are connected through the I2S bus, the device end performs data sampling, and the device end is provided with a plurality of microphones, each Each microphone corresponds to one channel. The master control terminal 30 includes a clock adjustment module 301 , a clock output module 303 and a data receiving module 305 .

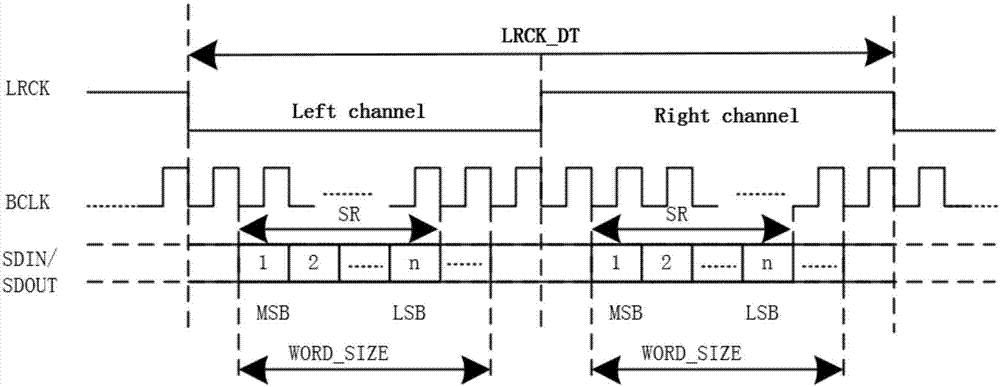

[0101] The clock adjustment module 301 changes the frame clock frequency and the bit clock frequency according to the number of audio channels on the device side. In this embodiment, the changed frame clock and bit clock satisfy the following formula: bclk=fs×N×Nbit×n, where lrck is the frame clock frequency, bclk is the bit clock frequency, fs is the sampling frequency, Nbit is the number of sampling bits, n is a positive integer, when the number of channels is even, N is eq...

Embodiment 2

[0108] Figure 5 Shows a functional block diagram of the device end in one embodiment of the present invention. In this embodiment, the device end 40 and the master control end are connected through the I2S bus, and the device end performs data sampling. The device end is provided with a plurality of microphones, each A microphone corresponds to a channel. The device end 40 includes a clock receiving module 401 and a data transmission module 403 .

[0109] The clock receiving module 401 is used to receive the changed frame clock and bit clock outputted by the master after changing the frequency of the frame clock and the frequency of the bit clock according to the number of channels of the device 40 . In this embodiment, the changed frame clock and bit clock satisfy the following formula: bclk=fs×N×Nbit×n, where lrck is the frame clock frequency, bclk is the bit clock frequency, fs is the sampling frequency, Nbit is the number of sampling bits, n is a positive integer, when...

Embodiment 3

[0115] Figure 7 Shows a flowchart of a method for transmitting multi-channel audio data at the master terminal according to an embodiment of the present invention, the method consists of Figure 4 The main control terminal 30 of an embodiment shown in the present embodiment, in this embodiment, the main control terminal 30 and the device end are connected through the I2S bus, the device end performs data sampling, and the device end is provided with a plurality of microphones, each microphone Corresponds to a channel. The master control terminal 30 includes a clock adjustment module 301 , a clock output module 303 and a data receiving module 305 .

[0116] In step S301, the master control terminal 30 changes the frame clock frequency and the bit clock frequency. The master control terminal 30 changes the frame clock frequency and the bit clock frequency according to the number of audio channels of the device terminal. In this embodiment, the changed frame clock and bit clo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More