Patents

Literature

150results about How to "Realize the mapping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

SDN (Software Defined Network) implementation method, device and system

ActiveCN105391568ARealize the mappingProgram controlData switching networksSoftware define networkPhysical network

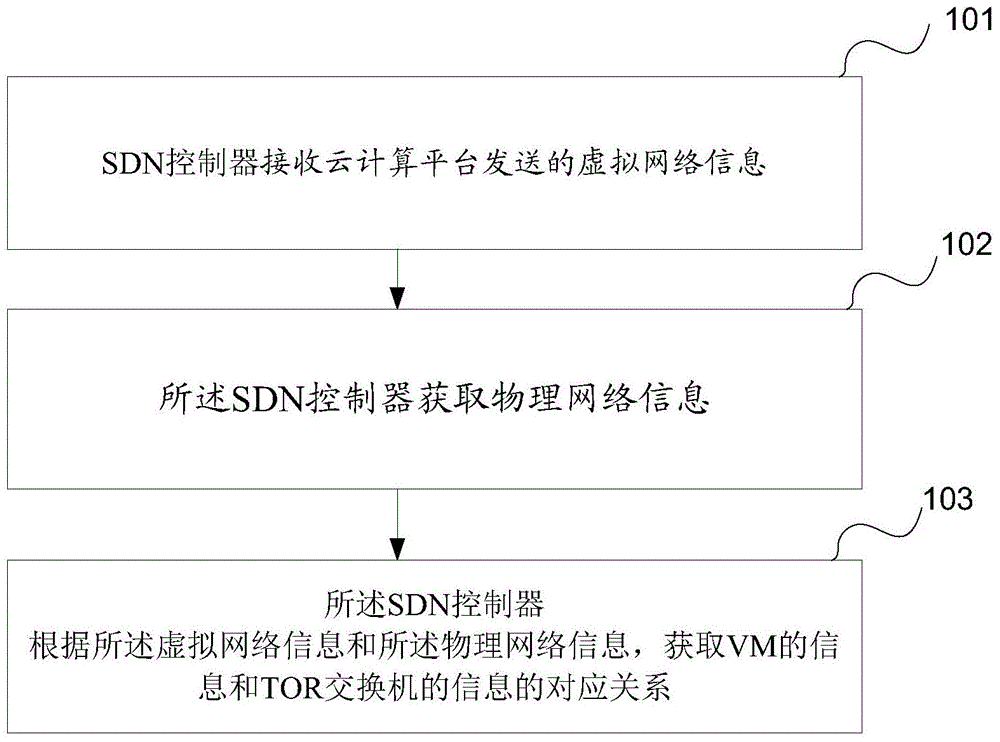

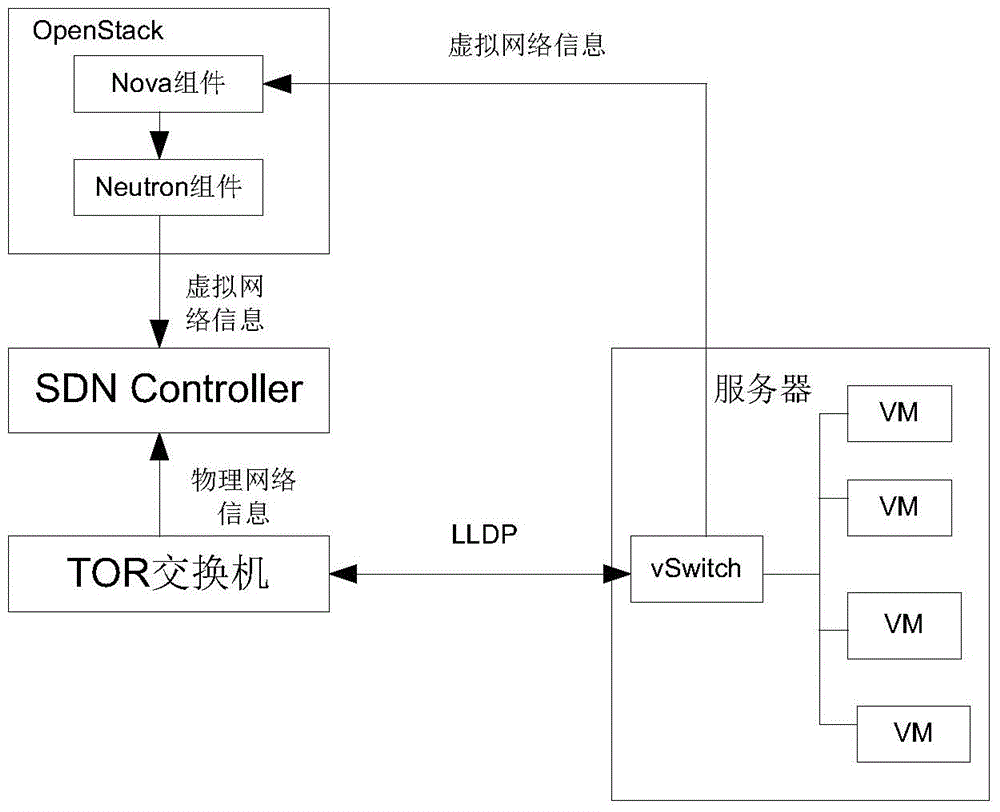

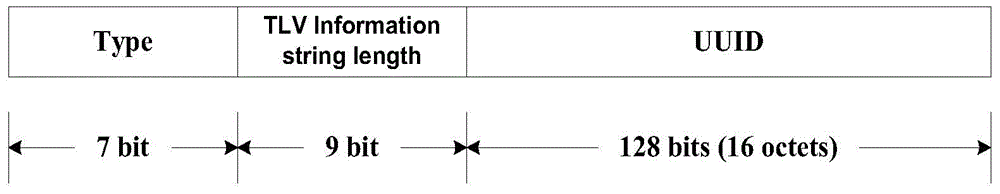

The invention discloses an SDN (Software Defined Network) implementation method. An SDN controller receives virtual network information transmitted by a cloud computing platform, and the virtual network information comprises the corresponding relation between VM information and information of a server for operating a VM. The SDN controller obtains physical network information, and the physical network information comprises the corresponding relation between the information of a TOR switcher and the information of the server. The SDN controller obtains the corresponding relation between the information of the VM and the information of the TOR switcher according to virtual network information and the physical network information. Therefore, the method can build a physical transfer path for the VM in a physical network, achieves the mapping from the virtual network to the physical network, and better supports the cloud computing platform to carry out the automatic distribution and adjustment of the businesses of the SDN controller as required.

Owner:HUAWEI TECH CO LTD

time sequence behavior detection method based on 3D human body key points

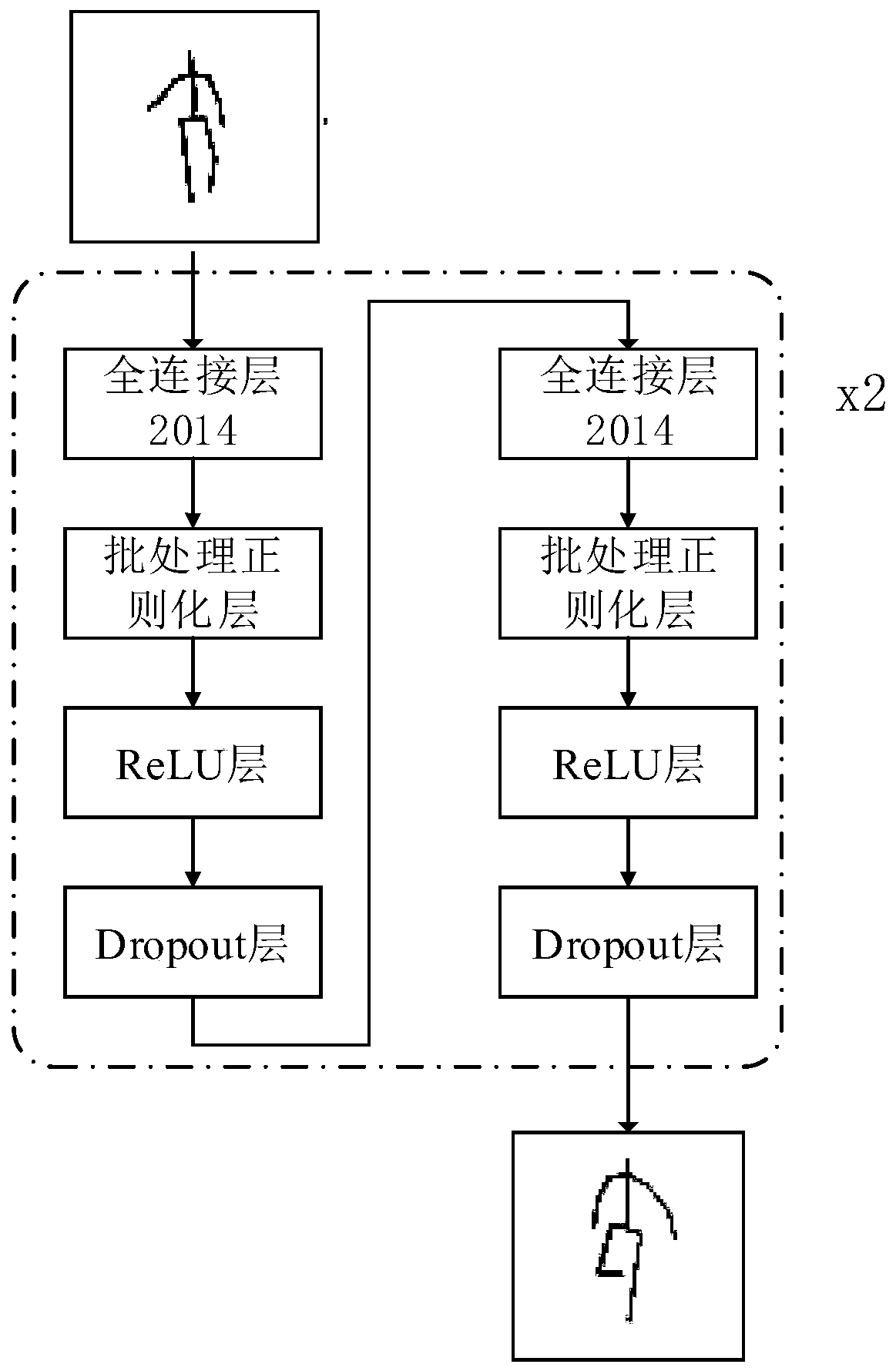

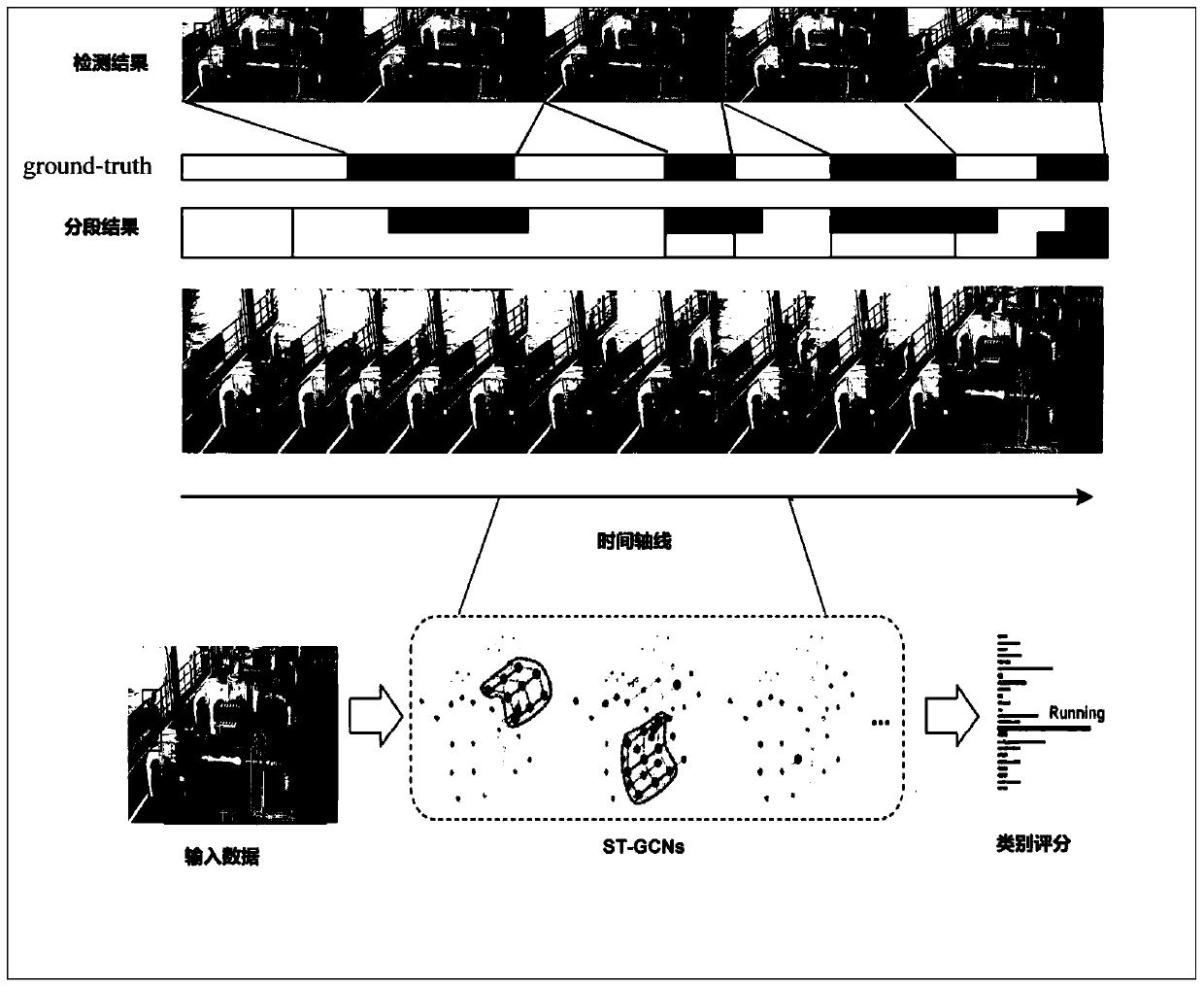

InactiveCN109919122AHigh precisionHigh speedCharacter and pattern recognitionData conversionJoint coordinates

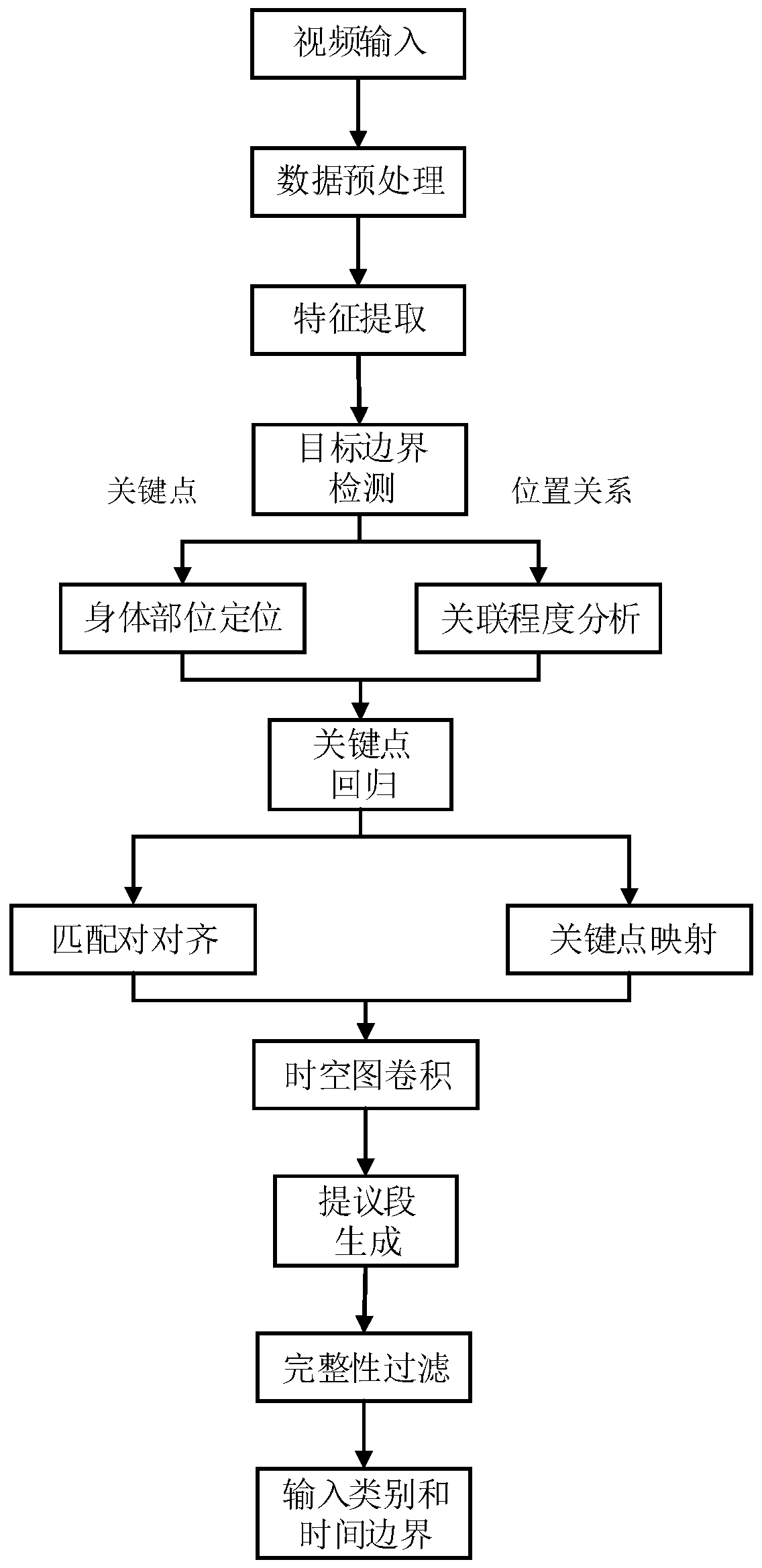

The invention discloses a time sequence behavior detection method based on 3D human body key points, and the method comprises the steps: taking video data as input, and converting the video data intocontinuous frame images through data preprocessing;c arrying out Feature extraction by using a multilayer CNN network, and detecting a boundary frame of a personnel target in the image; secondly, through body part positioning and correlation degree analysis, acquiring 2D human body key point coordinates and mapping from 2D human body key points to achieve 3D key points by constructing a key pointregression network; inputting the 3D joint coordinates into a space-time diagram convolutional network to carry out frame-level action recognition and classification on the whole video sequence, and grouping adjacent frames of the same label to obtain action proposal segments with different granularities; andprecisely correcting the time boundary of the action through fine-grained integrity filtering, so that the time sequence behavior detection in a complex scene is realized. According to the method, more valuable information can be analyzed from the 3D data, and the time sequence behavior detection and positioning precision is remarkably improved.

Owner:CHINA UNIV OF PETROLEUM (EAST CHINA)

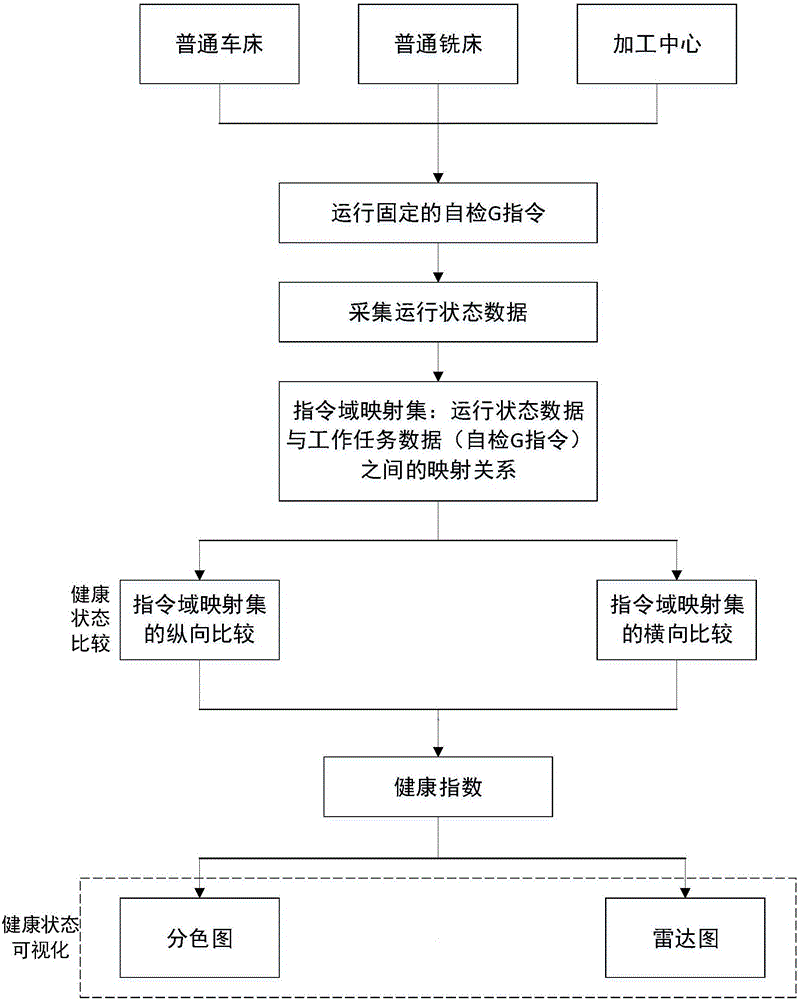

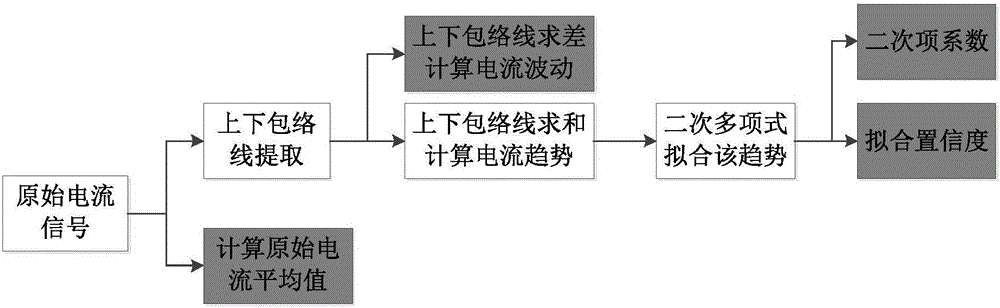

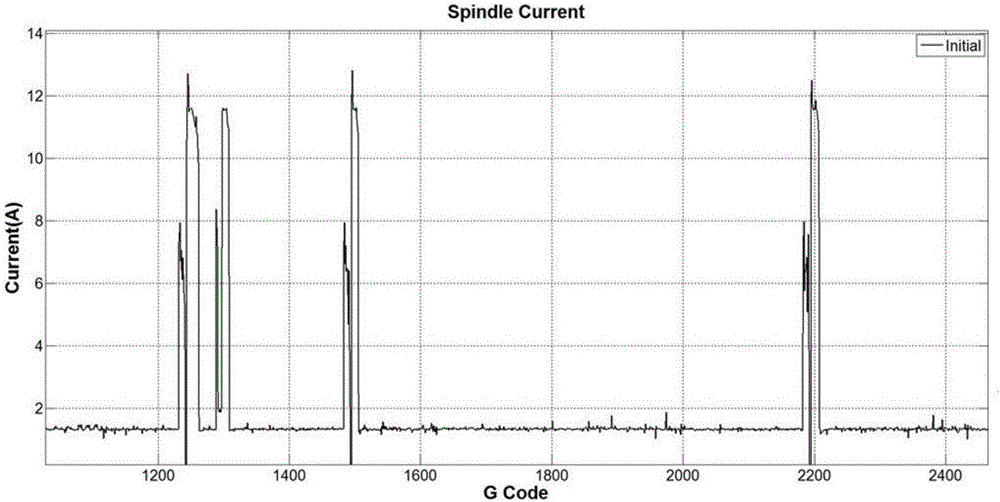

Health monitoring method for numerical control machine tool

ActiveCN105974886AClear running processThe data is relatively scientific and reasonableProgramme controlComputer controlNumerical controlHealth index

The invention discloses a health monitoring method for a numerical control machine tool, and the method comprises the steps: (1), executing a self-inspection G instruction, and collecting the operation state data; (2), building the mapping relation between the collected operation state data and the self-inspection G instruction, and forming an instruction domain mapping ensemble; (3), dividing the instruction domain mapping ensemble according to the self-inspection G instruction, extracting the instruction domain mapping under the self-inspection G instruction, obtaining the operation state data under the self-inspection G instruction, calculating an actual characteristic value according to the operation state data, comparing the actual characteristic value with a standard characteristic value, and obtaining a health index through calculation. The method improves the calculation basis of a key health index of the numerical control machine tool, the calculation method of the health index and the display mode of the health index, and can effectively solve a problem that the judgment of the health condition of the numerical control machine tool is not timely and accurate. Moreover, the obtained health index of the numerical control machine tool is displayed in a visualized manner, thereby improving the interaction effect of the numerical control machine tool with a person.

Owner:HUAZHONG UNIV OF SCI & TECH

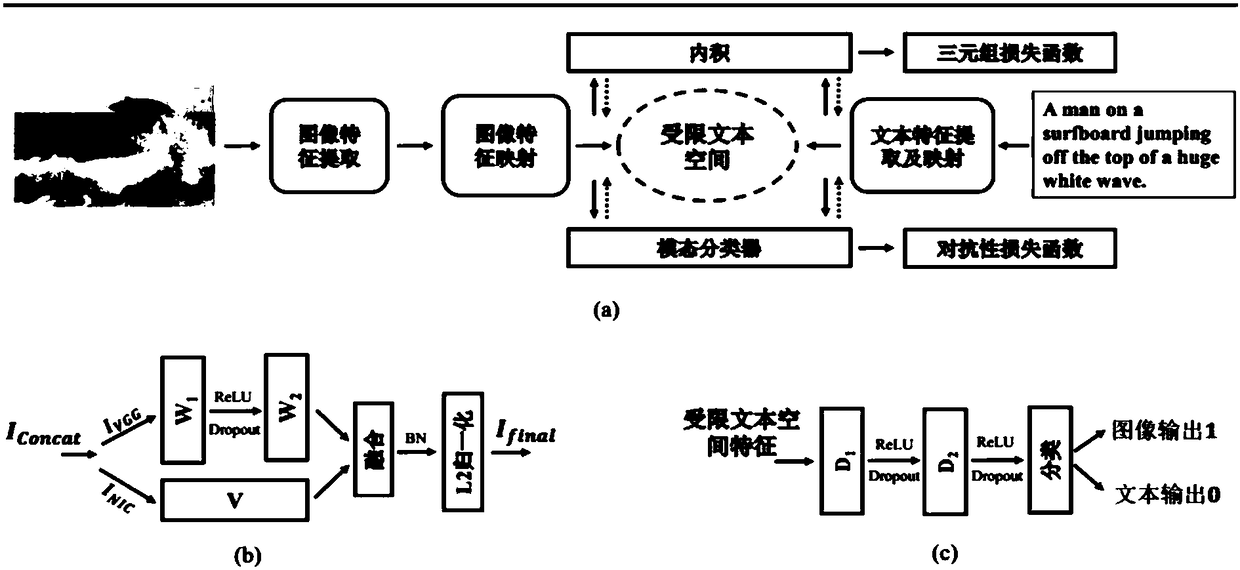

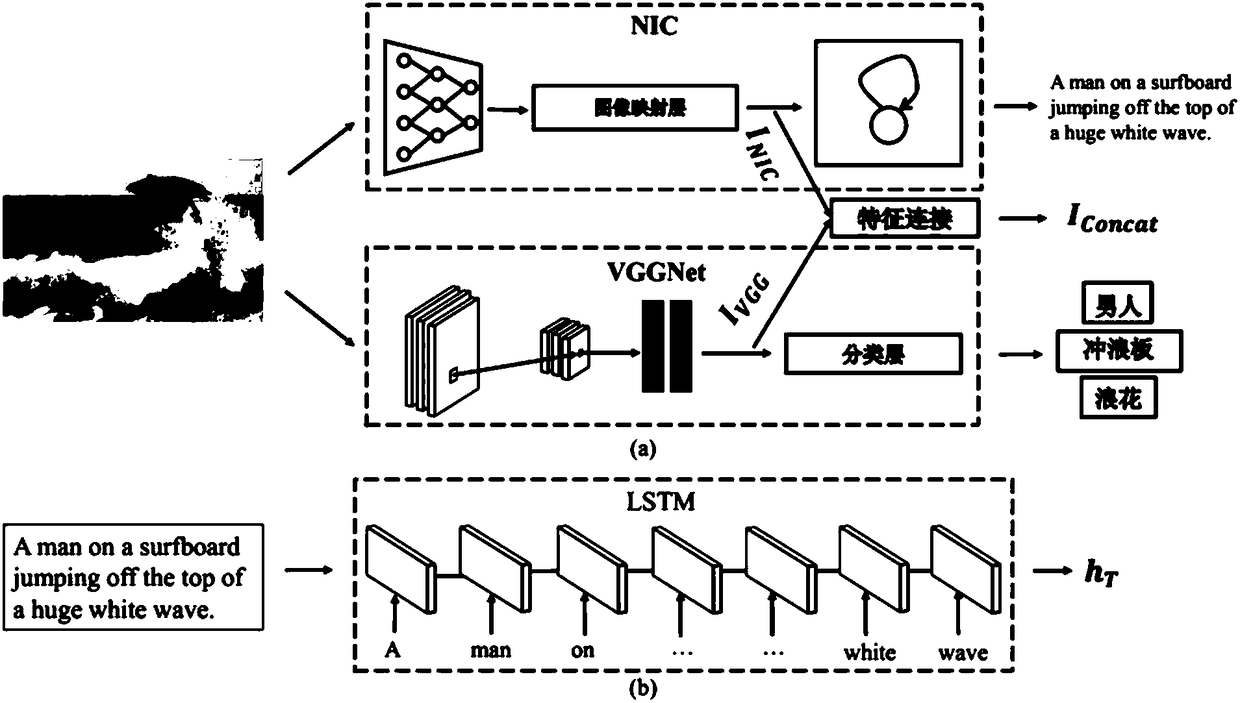

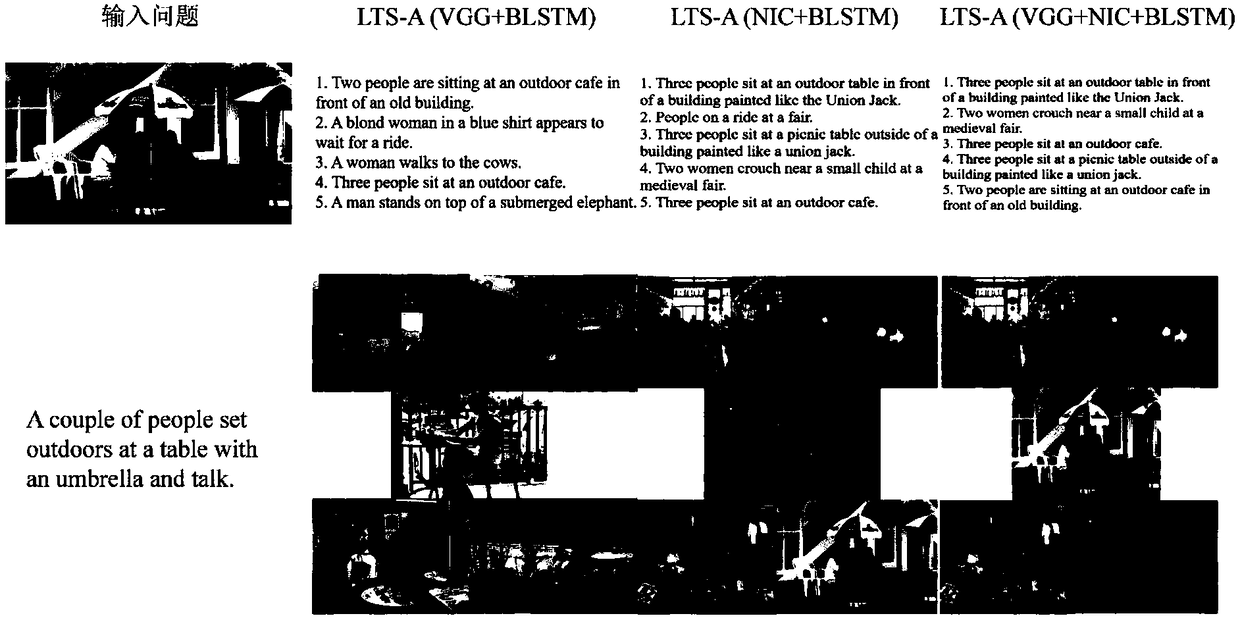

Antagonistic cross-media search method based on limited text space

ActiveCN108319686AReduce the variability of feature distributionRealize the mappingRelational databasesSelective content distributionComputer visionFeature mapping

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

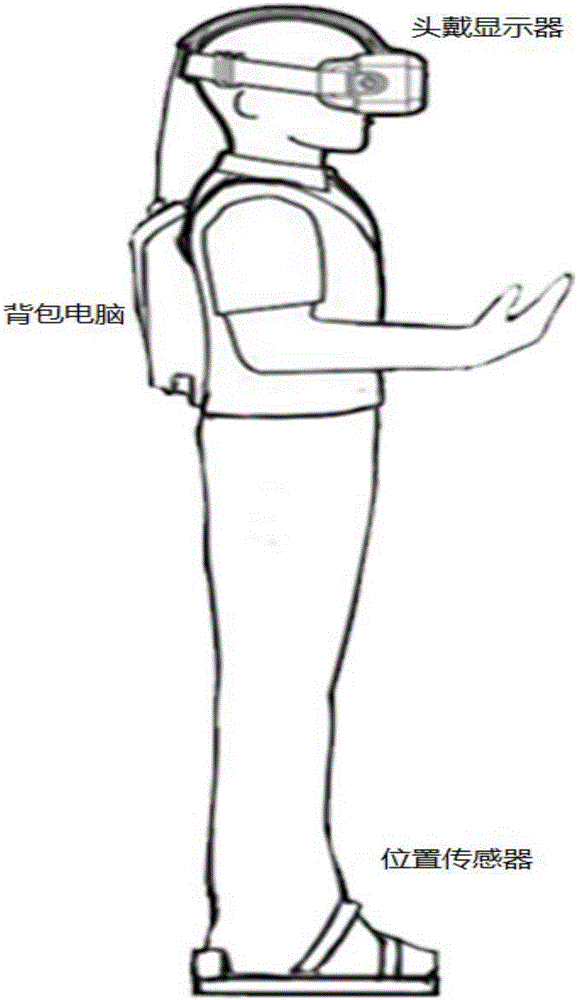

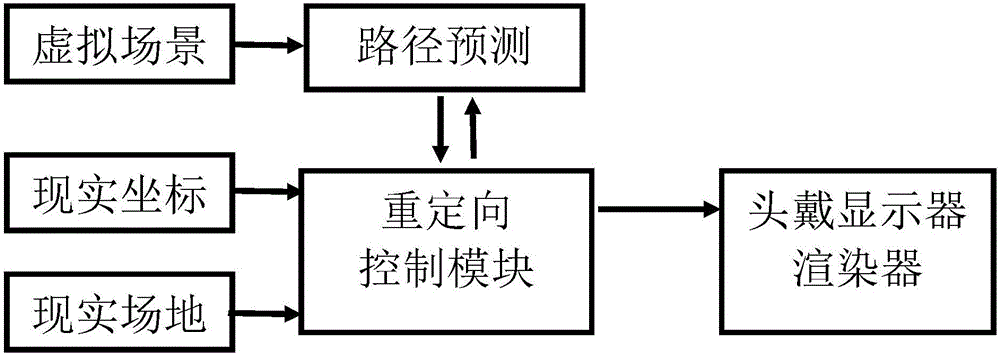

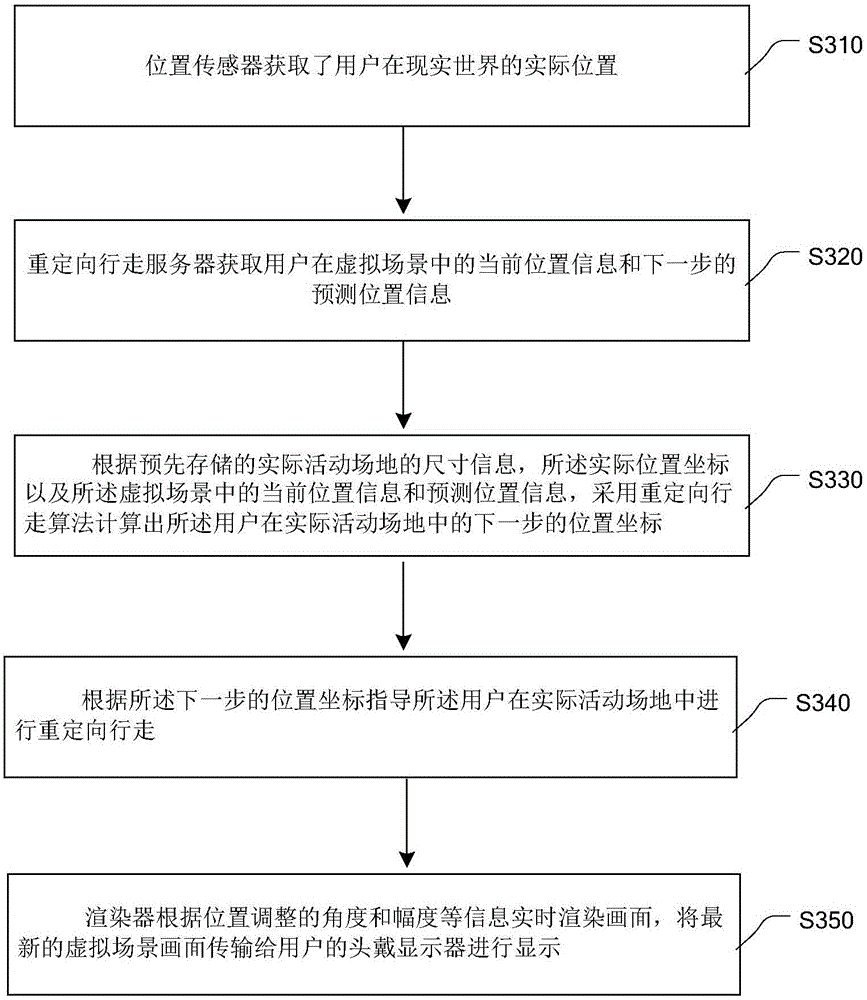

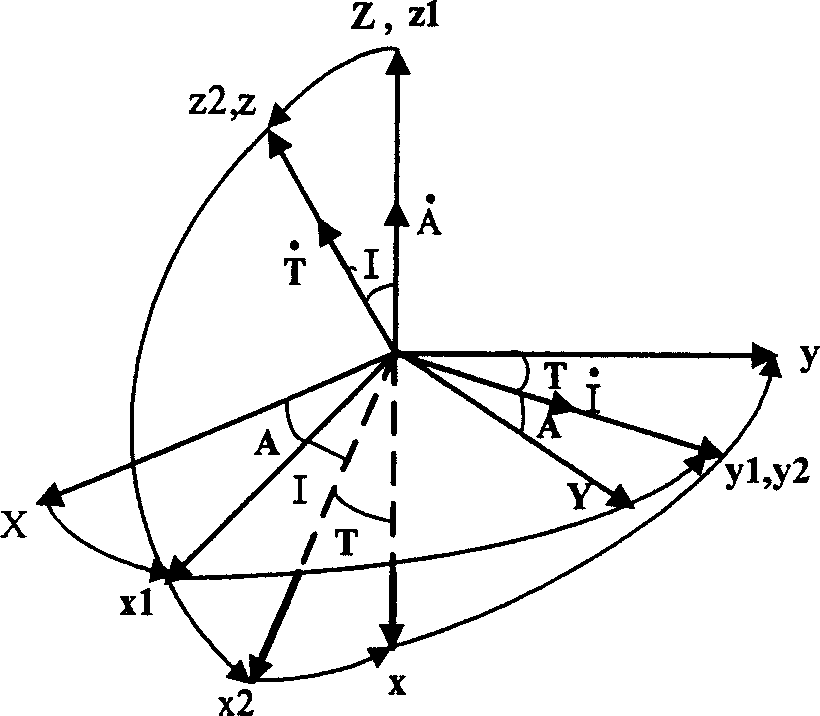

Method of redirection walking in virtual reality

InactiveCN106504334ARealize the mappingIncrease activity spaceInput/output for user-computer interactionImage data processingVirtual worldPosition sensor

The invention provides a method of redirection walking in virtual reality. The method of redirection walking in virtual reality includes the steps: by means of a position sensor, acquiring the practical position coordinates of the user in the practical activity space; acquiring the current position information and the predicted position information of the user in a virtual scene; according to the pre-stored size information of the practical activity space, the practical position coordinates and the current position information and the predicted position information in the virtual scene activity space, and using the redirection walking algorithm to calculate the position coordinates of the next step of the user in the practical activity space; and according to the position coordinates of the next step, guiding the user to perform redirection walking in the practical activity space. The method of redirection walking in virtual reality can acquire the walking path information of the user in the practical activity space according to the virtual scene, and can guide the user to walk freely in the virtual world without exceeding the boundary of the real world, thus enlarging the activity space of the virtual world, and realizing the mapping from the limited practical space to the virtual infinite space.

Owner:视境技术(深圳)有限公司

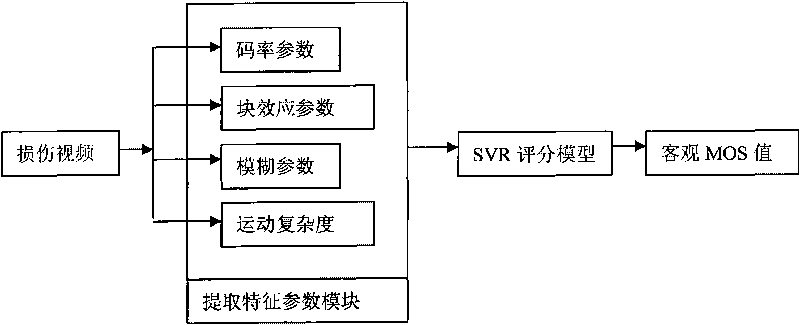

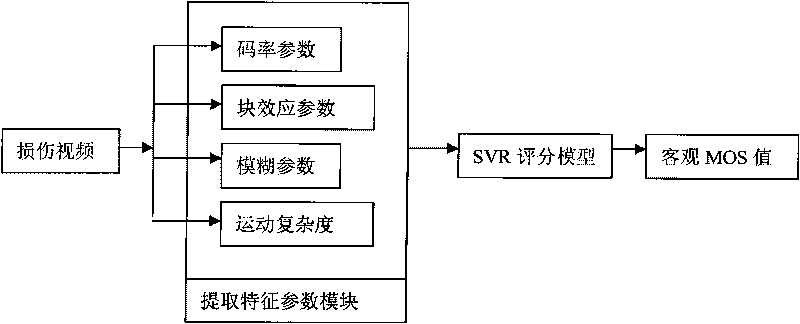

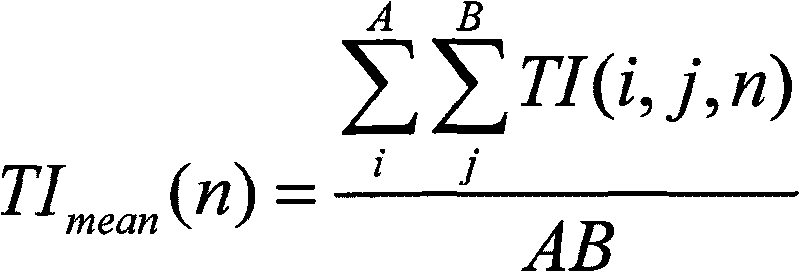

No-reference video quality evaluating method

ActiveCN101742353ARealize the mappingNo loss of precisionTelevision systemsTime domainImage resolution

The invention provides a no-reference video quality evaluating method, and aims to solve the problems of low relevance between an objective MOS value and a subjective MOS value output by the conventional method, weak prediction accuracy and weak generalization ability thereof. The method comprises the following steps: extracting blocking effect parameters, blur parameters and code rate parameters of video received by a receiving end; setting motion complexity parameters for the video according to the decoded time domain of the video; outputting the objective MOS value by using an evaluation model which is acquired in advance based on support vector (SV) regression (SVR) according to the blocking effect parameters, the blur parameters, the code rate parameters and the motion complexity parameters; and acquiring higher relevance with the subjective MOS value. On characteristic parameter selection, TS stream parameters are integrated with main sense injury parameters; and the evaluation model determining method adopts a method of the support vector regression. The method is applicable to videos in different resolution ratios, in particular to videos with encoder injury.

Owner:THE RES INST OF TELECOMM TRANSMISSION MIIT +2

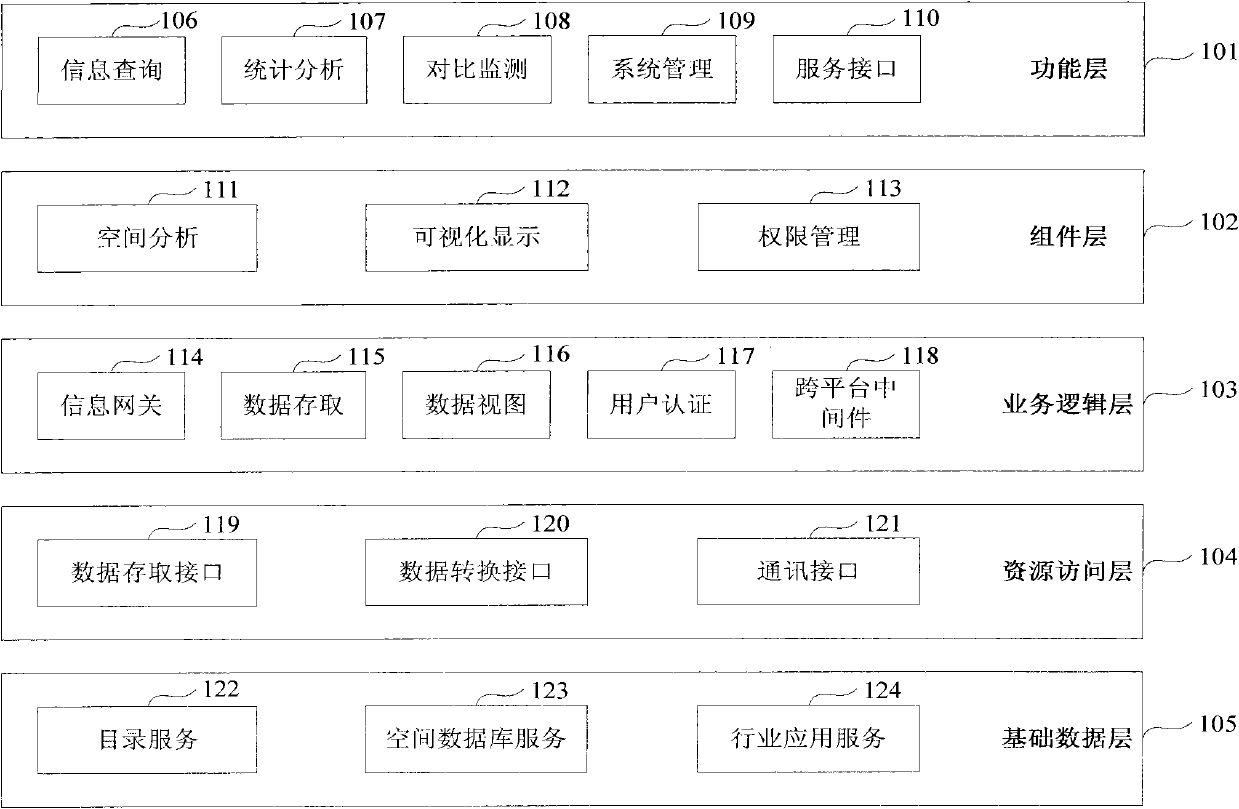

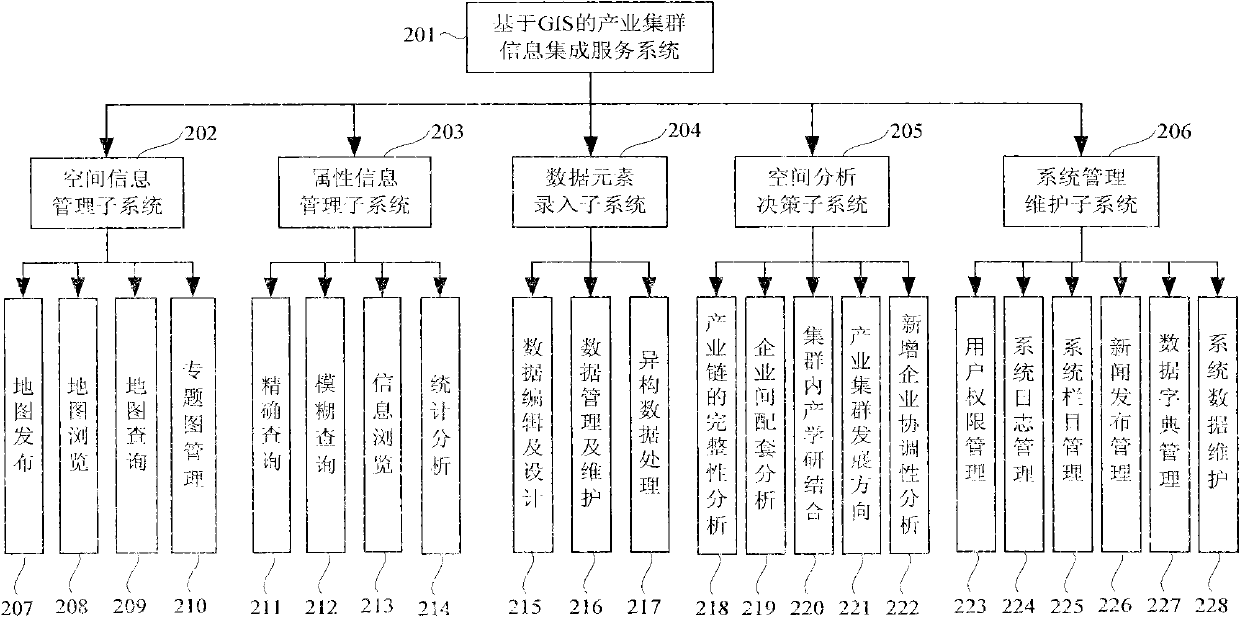

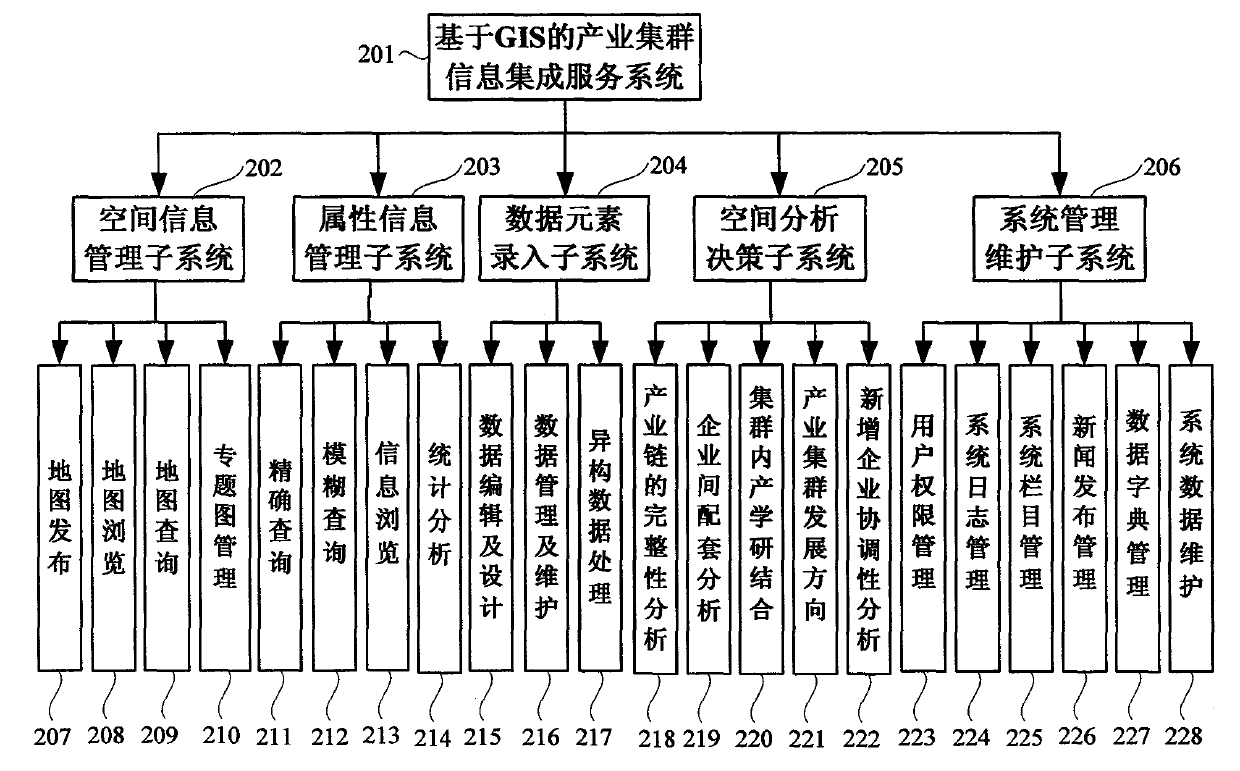

Geographic information system (GIS)-based industrial cluster information integration service system and method

InactiveCN101908165ARealize the mappingAchieve correspondenceResourcesInformation processingSystems management

The invention relates to the field of industrial cluster information integration services, in particular to a geographic information system (GIS)-based industrial cluster information integration and service method and an information integration service system adopting the same. The system mainly comprises a spatial information management subsystem, an attribute information management subsystem, a data element input subsystem, a spatial analysis and policy-making subsystem and a system management and maintenance subsystem. The GIS-based industrial cluster information integration service system and the GIS-based industrial cluster information integration method of the invention have the advantages of introducing advanced GIS technology to realize the mapping and corresponding of spatial information and many kinds of attribute information and meet the requirements of system users on the advancement, accuracy and timeliness of geographic information and technical information, and visibly, conveniently and fast providing the public service support of the resources of geographic orientations, equipment, technology, processes, products and the like for enterprises in and among clusters by utilizing content-based information processing technology and performing intelligent analysis through networks.

Owner:BEIJING ZHONGJIKEHAI TECH & DEV

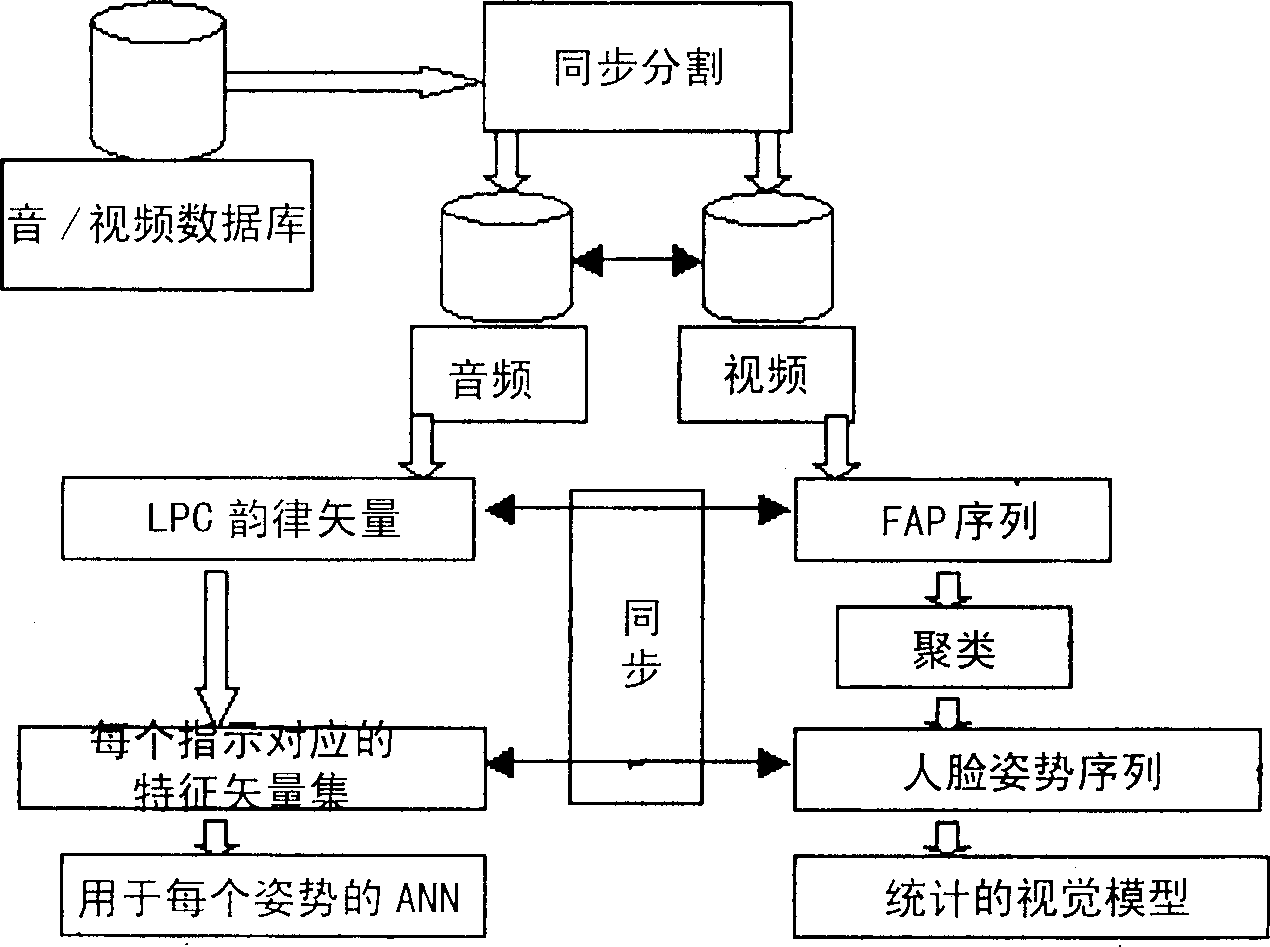

Statistics and rule combination based phonetic driving human face carton method

InactiveCN1466104ARealize the mappingThe way to implement the mappingBiological neural network modelsSpecial data processing applicationsFeature vectorRelational model

The invention is a method face cartoon driven by voice which is based on the combination of statistic and rules, it includes steps: gets the audio and video frequency data flow by using audio and video frequency synchronous cuttnig method; gets the corresponding eigenvector through audio and video frequency analyzing method; gets the radio and video frequency synchronous mapping relation model through statistic learning method; gets the face moving parameter which is corresponding to the vodei serial of the user by using the model and drives the face cartoon model. The invention uses video gathering, voice analyzing and photo processing, records the actual voice when speaking and the character points moving data.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

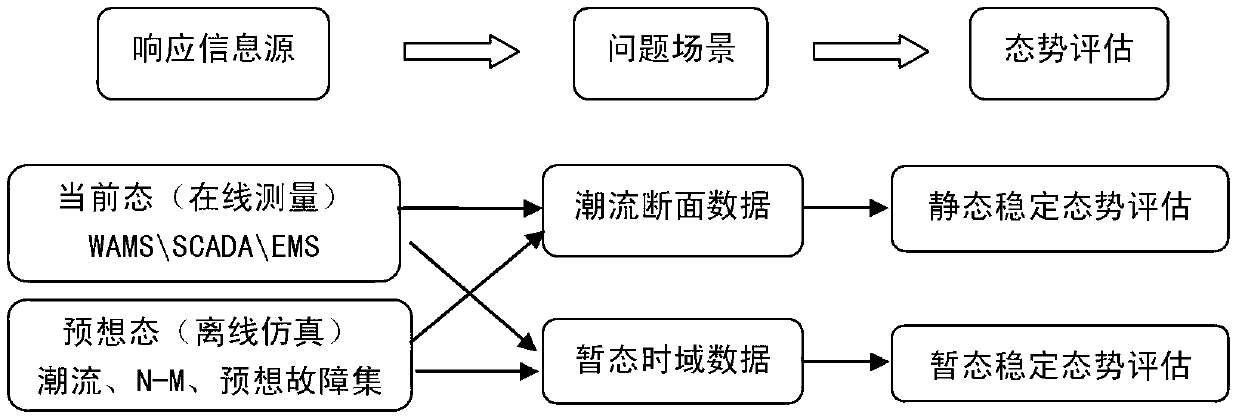

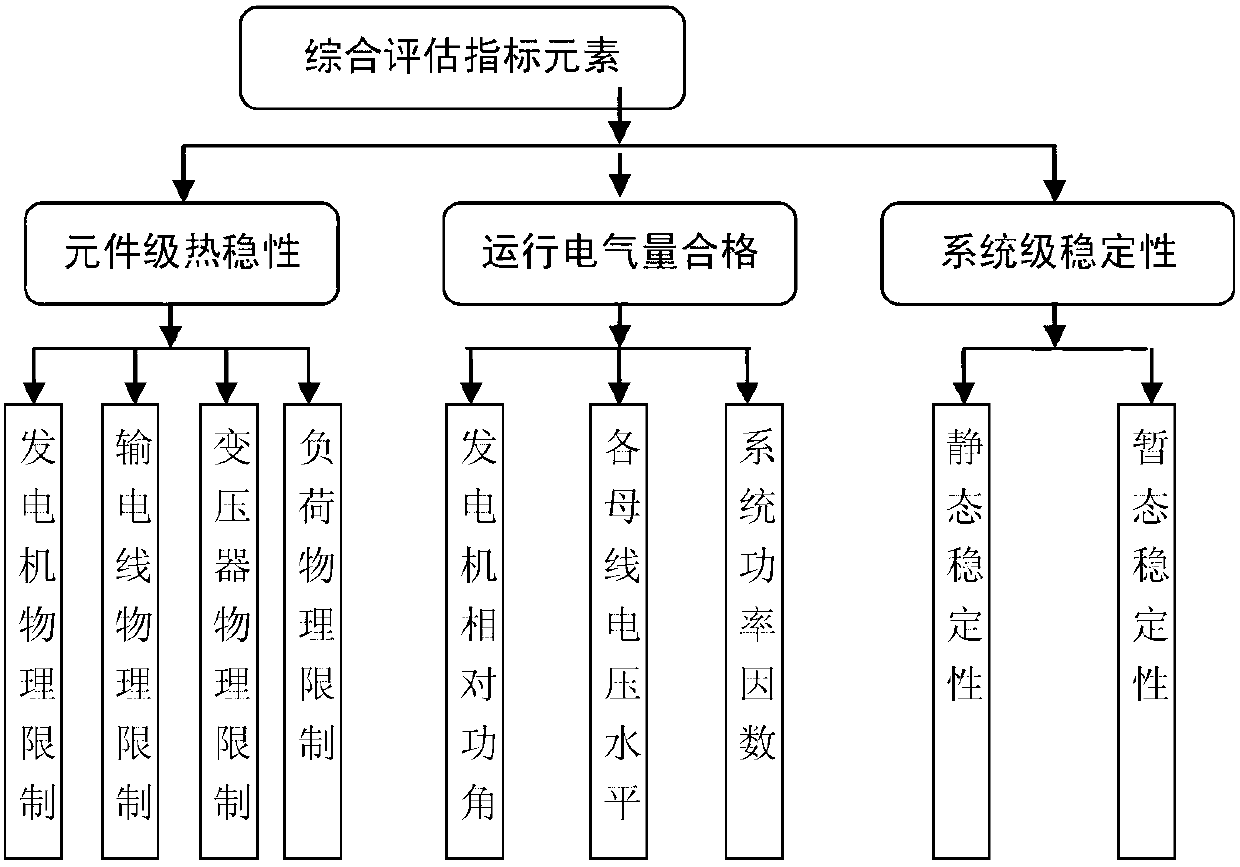

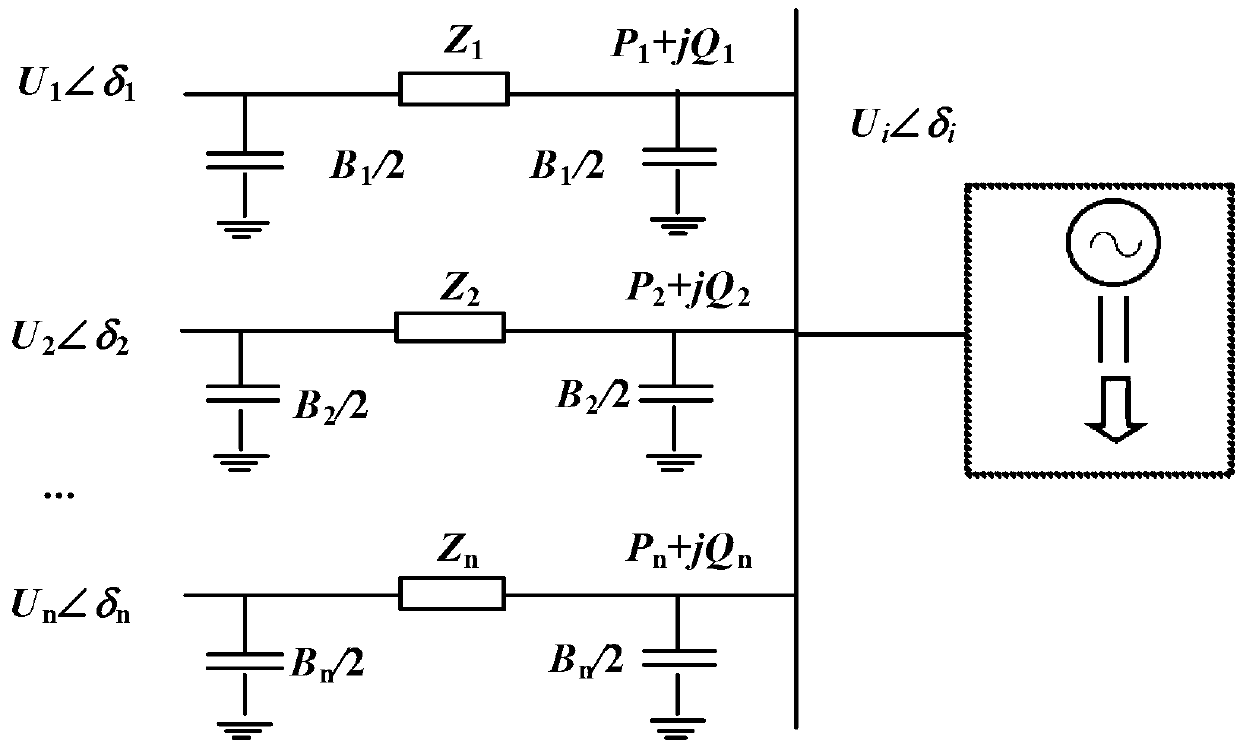

Large power grid overall situation on-line integrated quantitative evaluation method based on response

ActiveCN103279638ARaise the level of early warningReduce workloadData processing applicationsSystems intergating technologiesTime domainStable state

The invention provides a large power grid overall situation on-line integrated quantitative evaluation method based on a response. The method comprises a first step of acquiring power grid topology structural information from an SCADA system and an EMS system and establishing a corresponding relation between the power grid topology structural information and a WAMS system power grid component, a second step of acquiring present power grid operation method trend data from the SCADA system or the EMS system or a WAMS system or acquiring various preconceived trends or transient state fault time domain data from a DSA system, and a third step of dividing responding data into two operation scenes including a steady state (or a quasi-stable state) and a transient state (or a dynamic state) in a macroscopic mode, wherein static state stabilization situation assessment is carried out on a power grid through an on-line node-facing method, and transient state stabilization situation assessment is carried out on the power grid through an on-line unit-facing method. Static state and transient state comprehensive assessment indicators are constructed based on component class thermostabilization, electric parameter acceptable range and system class stabilization, the comprehensiveness and reasonability of the overall situation assessment indicators are improved, and the efficiency of overall situation integrated assessment is improved through the method that tasks are carried out at the same time.

Owner:STATE GRID CORP OF CHINA +1

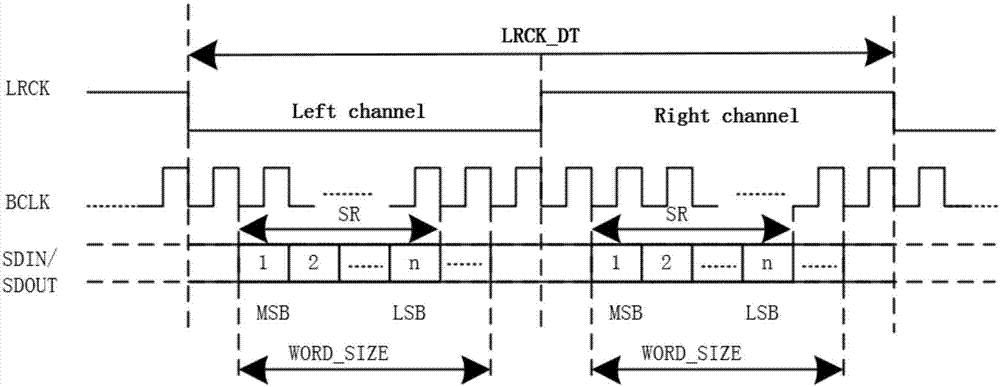

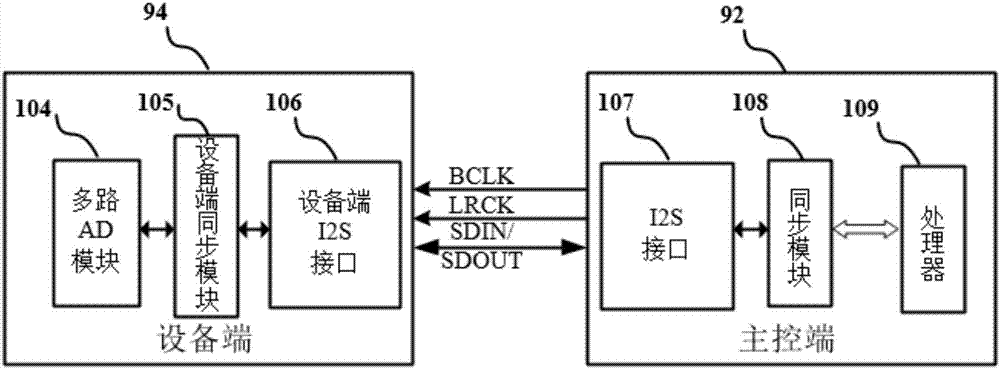

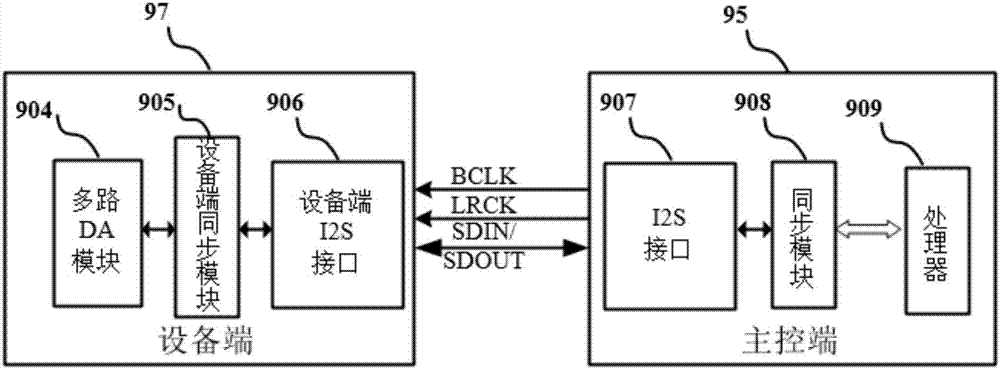

Master control terminal, device terminal and method and system for transmitting multichannel audio data

ActiveCN106911987ARealize the mappingOvercome difficultySignal processingLoudspeaker signals distributionComputer hardwareTransmission protocol

The invention relates to a system for transmitting multichannel audio data. The system for transmitting multichannel audio data comprises a master control terminal and a device terminal, and the device terminal is connected with the master control terminal through a bus; the master control terminal comprises: a clock adjustment module, a clock output module and a data receiving module; and the device terminal comprises a clock receiving module and a data transmission module. The invention further provides a master control terminal, a device terminal and a method and system for transmitting multichannel audio data. A multichannel audio bus transmission protocol for realizing multichannel data transmission can be realized without adding an interface conversion chip to the master control terminal, and the defects of high design difficulty and high hardware cost of an I2S interface in the multichannel data transmission application are overcome.

Owner:ALLWINNER TECH CO LTD

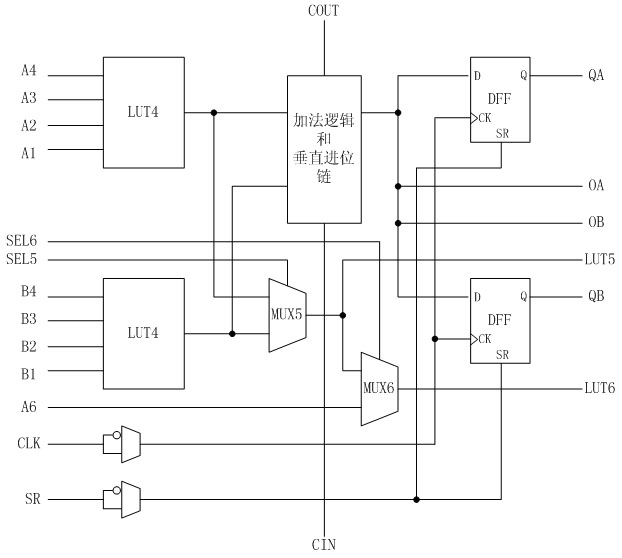

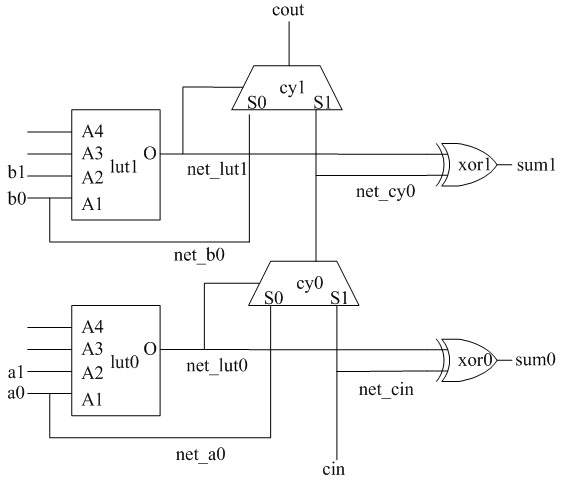

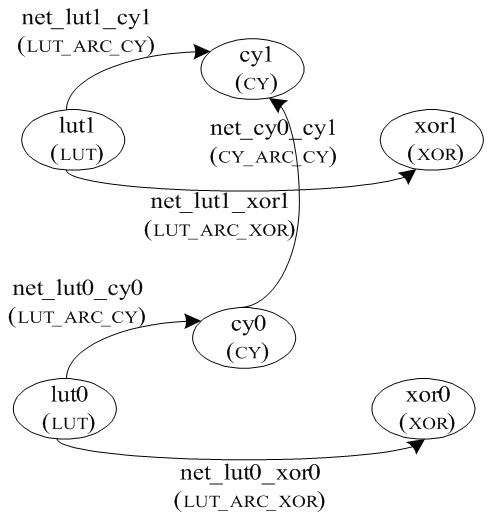

General packing method for FPGA (field programmable gate array) configurable logical block (CLB)

InactiveCN102054110AImprove chip logic resource utilizationImprove timing performanceSpecial data processing applicationsModularitySystem architecture design

The invention belongs to the technical field of electronics, in particular to a general packing method for an FPGA (field programmable gate array) configurable logical block (CLB). The method comprises the following steps: configuring and describing chips of the FPGA CLB as a series of directed simple graphs for constraining a satisfaction problem picture matching method; and then identifying a logical function sub-circuit supported by the chip from a user circuit by using the constraint satisfaction problem picture matching method, and packing. According to the invention, only if a library file which describes a target FPGA logical function circuit is pre-defined, the FPGA chips of different structures, such as various functional configurations of a quick carry chain, a distribution type memory, a shift register, an LUT5 (local user terminal 5), an LUT6 (local user terminal 6) and the like can be packed, thereby effectively improving the utilization rate of the logical resources of the chips, and improving the time sequence performance of the circuit. According to the invention, the circuit is optimized according to the appointed requirements, and the mapping of various modularized circuits is realized, thus the method has significant application in system architecture designs and reconfigurable systems.

Owner:FUDAN UNIV

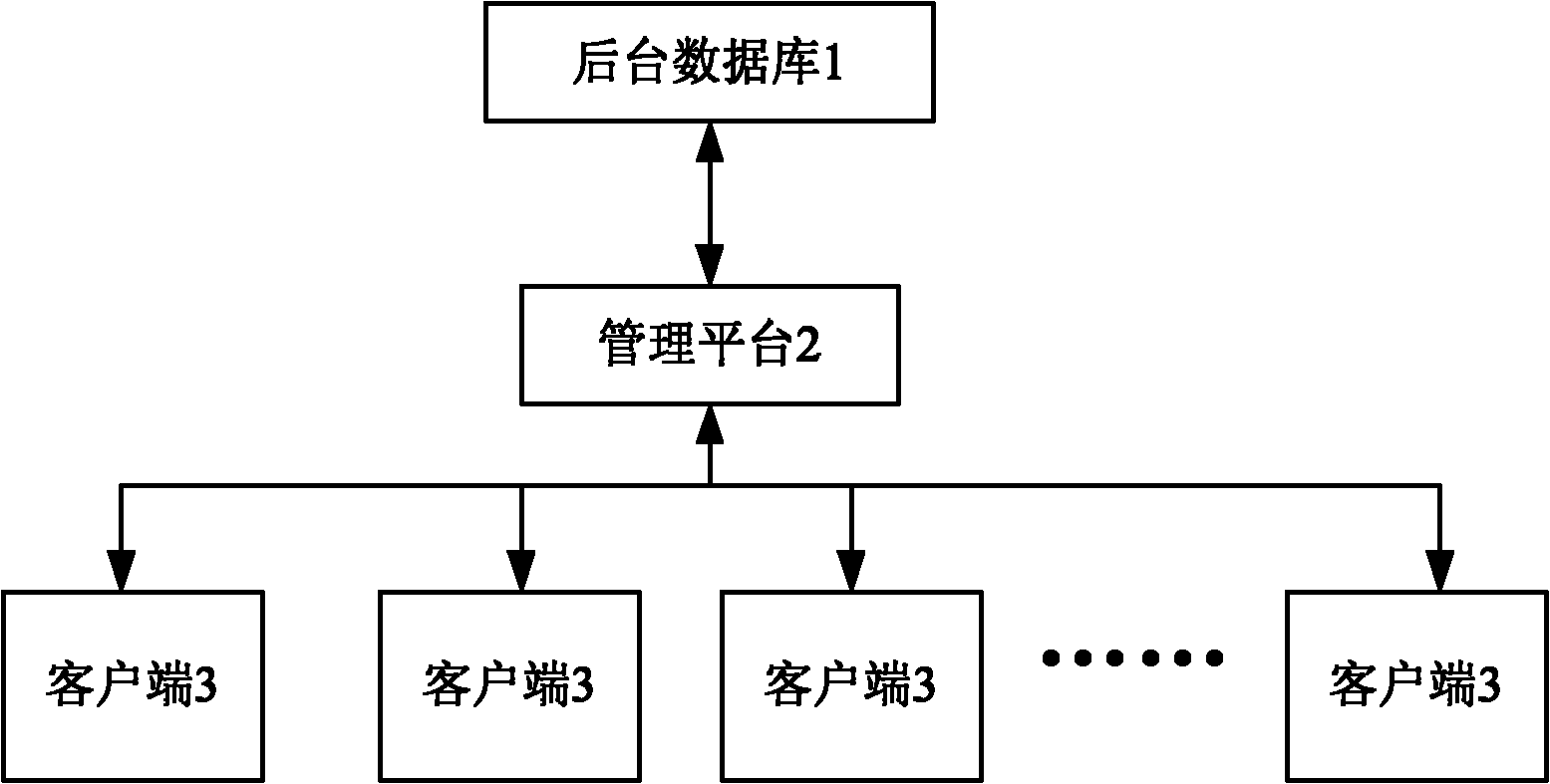

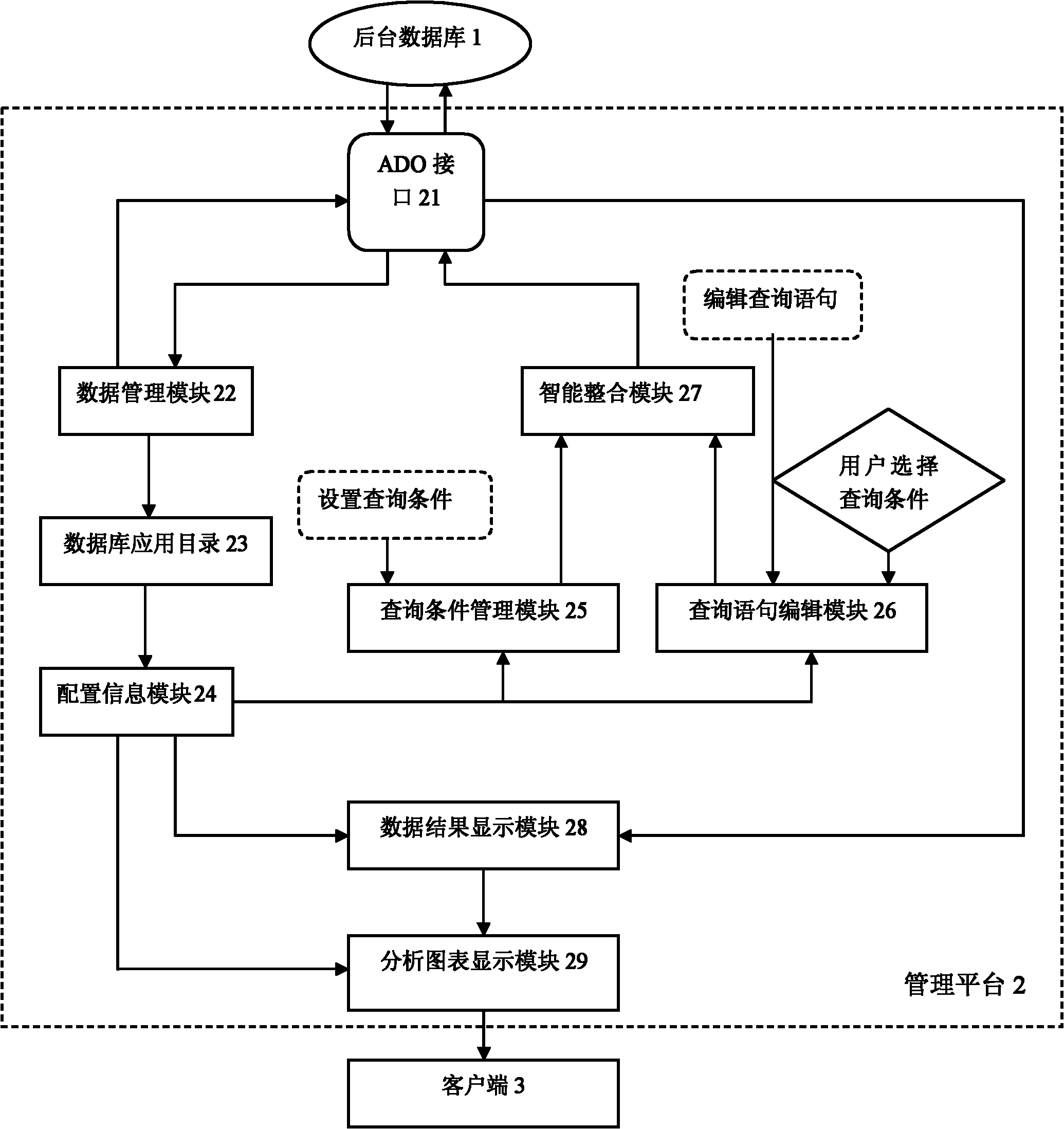

User-oriented database management system

ActiveCN102012945ASolve the generality problemSolving the Contradiction of Ease of UseSpecial data processing applicationsData connectionDatabase application

The invention discloses a user-oriented database management system, comprising backstage databases, a management platform and a client, wherein the management platform is provided with a data management module, a configuration information module, a query condition management module and a query sentence edit module; the client is provided with query interfaces, and the management platform can login through any query interface; the data management module is connected with the backstage databases, and one or more database applications are set in the backstage databases; and the configuration information module sets configuration data for each backstage database, outputs a conditional variable set to the query condition management module and outputs a primary query sentence set and data connection parameters to the query sentence edit module. As the conditional variables in the conditional variable set correspond to the query conditions displayed on the query interfaces one by one, the query conditions are transferred to parameter sequences to replace the variable names of the conditional variables in the primary query sentences, therefore, the query conditions are selected by a user and then are dynamically combined with the conditional variables and the primary query sentences, query systems can be dynamically managed, and the query functions of the original system can be expanded.

Owner:重庆亿煊新材料科技有限公司

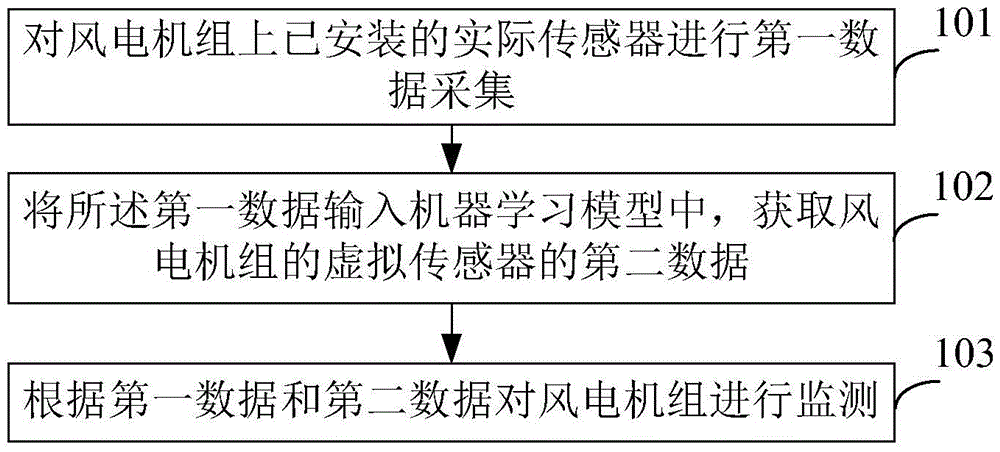

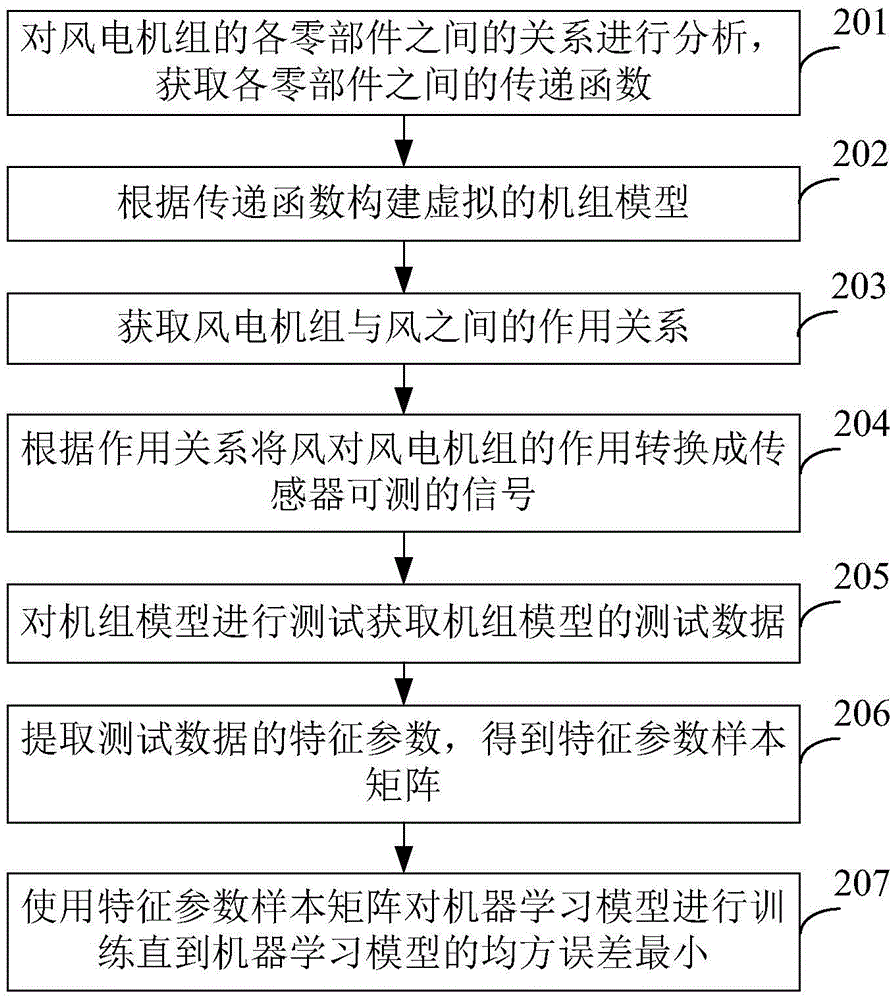

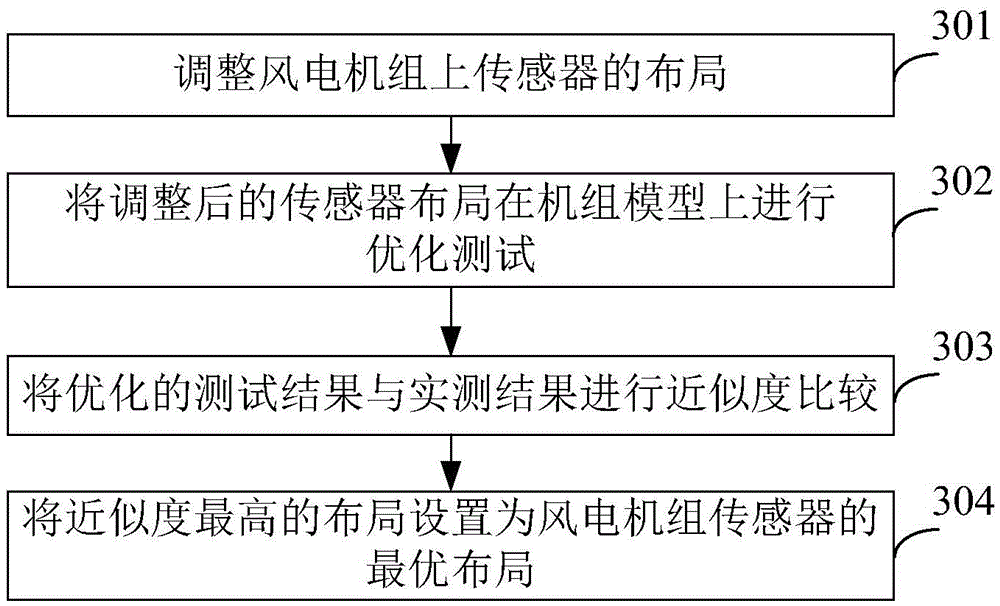

Method and device for monitoring wind turbine set

ActiveCN105604807AImprove accuracy and effectivenessRealize the mappingMachines/enginesWind motor monitoringAutomotive engineeringData entry

The invention provides a method and a device for monitoring a wind turbine set. The method comprises the following steps: acquiring first data from practical sensors mounted on the wind turbine set; inputting the first data into a machine learning model; acquiring second data from virtual sensors of the wind turbine set; monitoring the wind turbine set according to the first data and the second data. As mapping between the practical sensors and the virtual sensors can be realized due to the machine learning model, omnidirectional state monitoring of the wind turbine set can be realized via the mounted practical sensors. Therefore, the accuracy and the effectiveness of monitoring can be improved.

Owner:BEIJING GOLDWIND SCI & CREATION WINDPOWER EQUIP

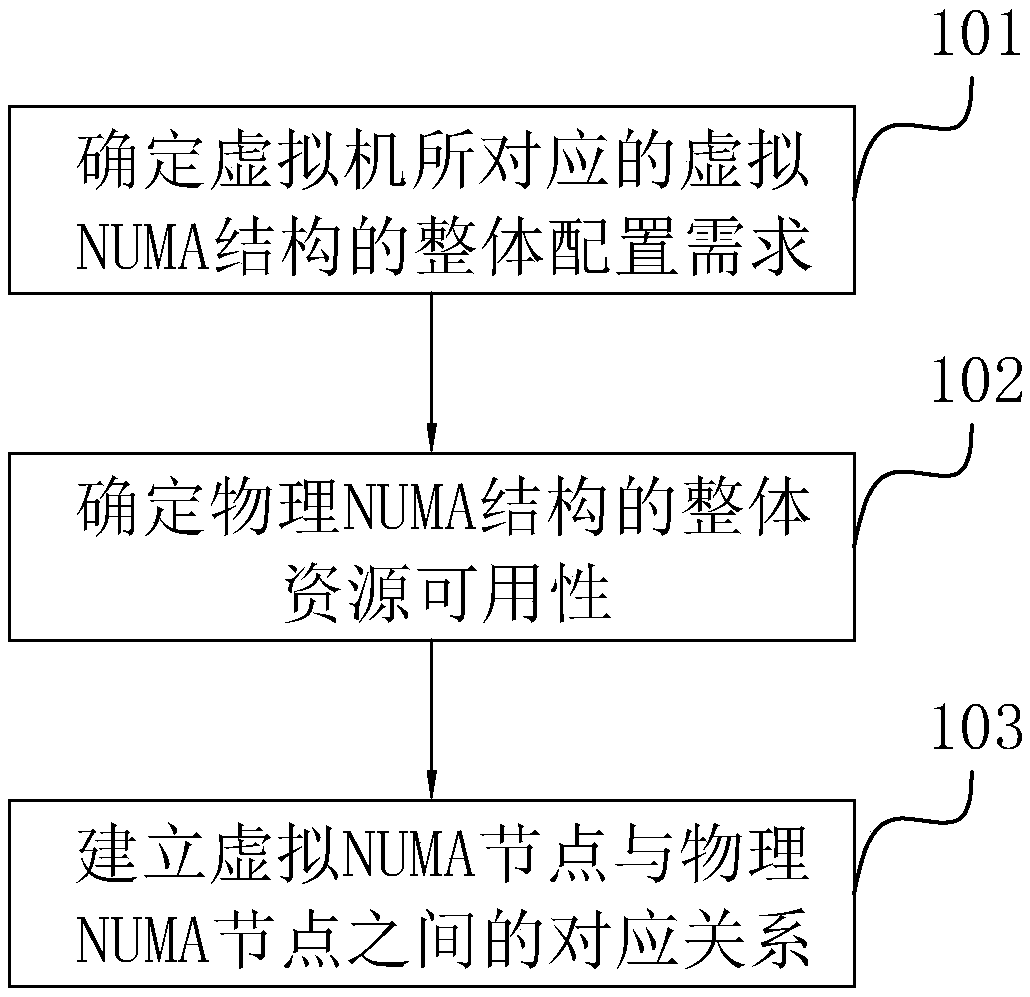

Resource scheduling allocation method, computer system and super-fusion architecture system

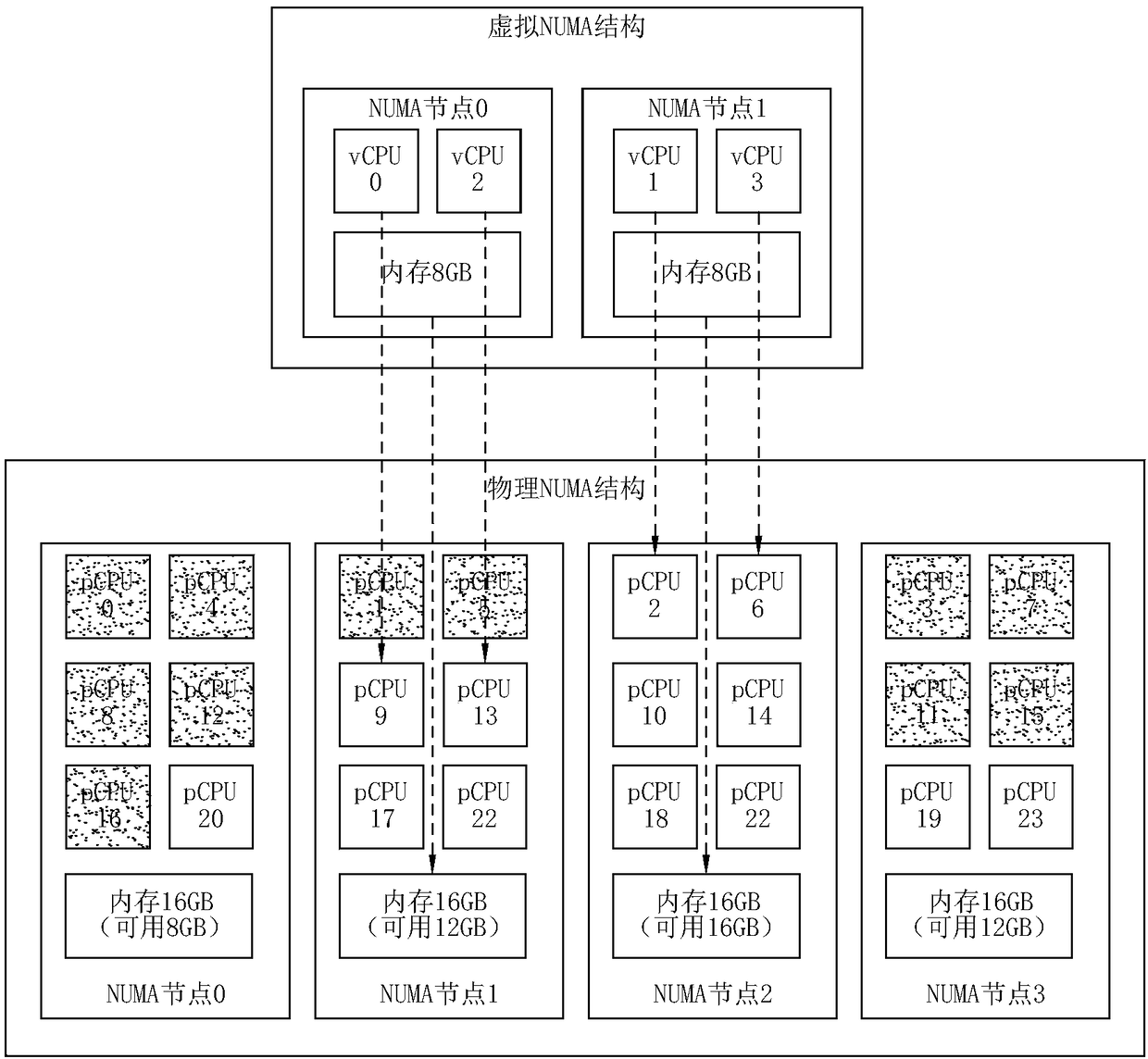

ActiveCN108196958ASecure available resourcesReduce resource contentionResource allocationVirtual memoryComputerized system

The invention relates to a resource scheduling allocation method, a computer system and a super-fusion architecture system. The resource scheduling allocation method comprises the steps of determiningan overall configuration demand of a virtual NUMA structure corresponding to a virtual machine, wherein the overall configuration demand comprises sub-configuration demands of a virtual NUMA node, and the sub-configuration demands include a first configuration demand for a virtual CPU core and a second configuration demand for a virtual memory; determining overall resource availability of a physical NUMA structure, wherein the overall resource availability comprises sub-resource availability of a physical NUMA node, and the sub-resource availability includes first resource availability for aphysical CPU core and second resource availability for a physical memory; and based on the overall configuration demand and the overall resource availability, establishing a corresponding relationshipbetween the virtual NUMA node and the physical NUMA node. The resource scheduling allocation method realizes mapping and binding of the virtual NUMA structure and the physical NUMA structure, so thatphysical resources are reasonably allocated.

Owner:武汉泽塔云科技股份有限公司

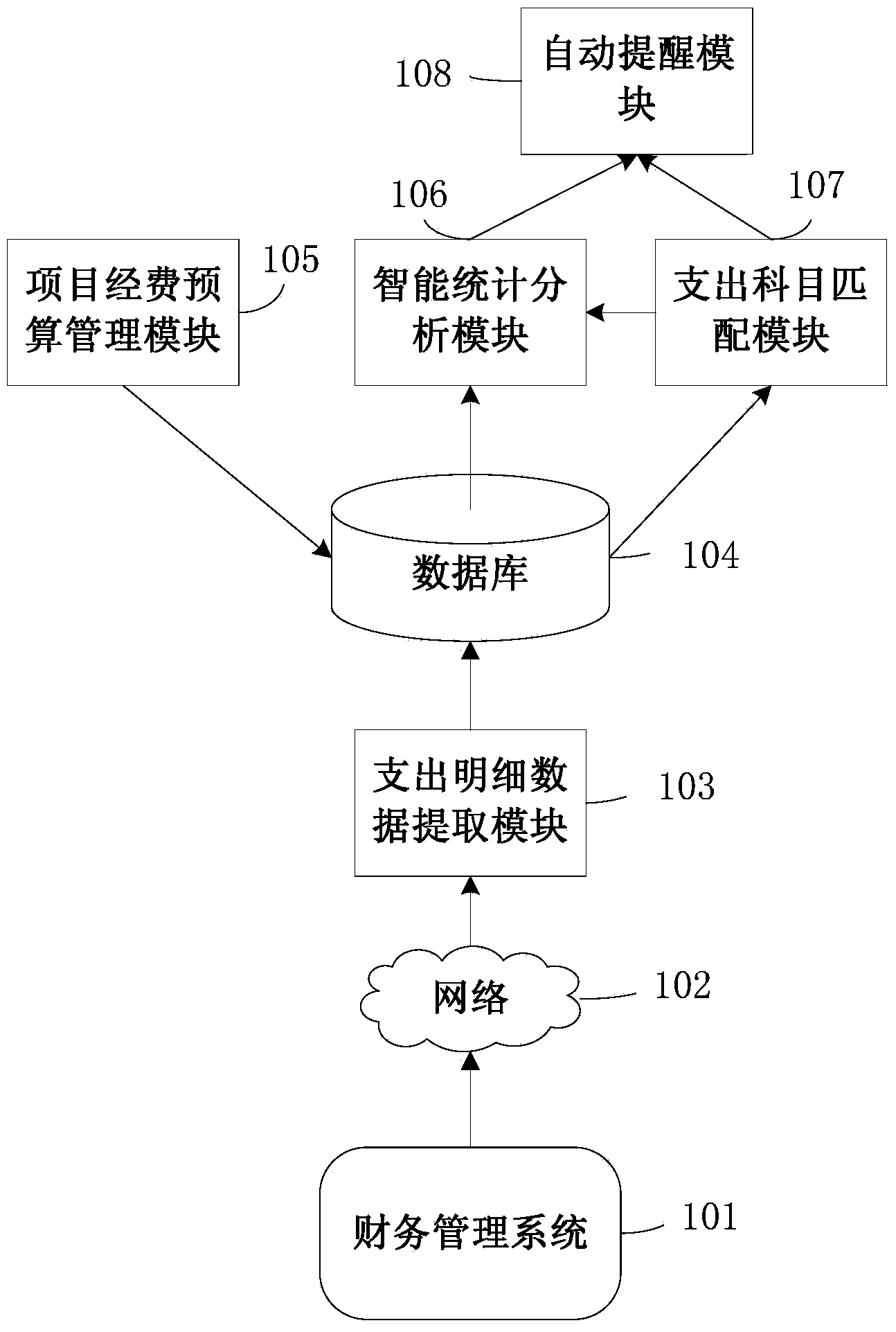

Scientific research item budget enforcement intelligent warning system

The invention provides a scientific research item budget enforcement intelligent warning system which comprises an item budget management module, an expenditure subject matching module, an intelligent statistic analysis module, an automatic warning module and an expenditure detail data extracting module. The item budget management module is used for being connected with a user and a database, and item information and budge data are added, deleted, modified and checked. The expenditure subject matching module is used for providing a matching function between expenditure details and item budge subjects. The intelligent statistic analysis module is used for providing a statistic analysis function of sub-subject budget expenditure with a scientific research item as a unit. The automatic warning module is used for warning on user budget expenditure situations in real time by calling the intelligent statistic analysis module and the expenditure subject matching module. The expenditure detail data extracting module is used for obtaining expenditure details in a scientific research organization financial management system automatically.

Owner:北京市农林科学院信息技术研究中心

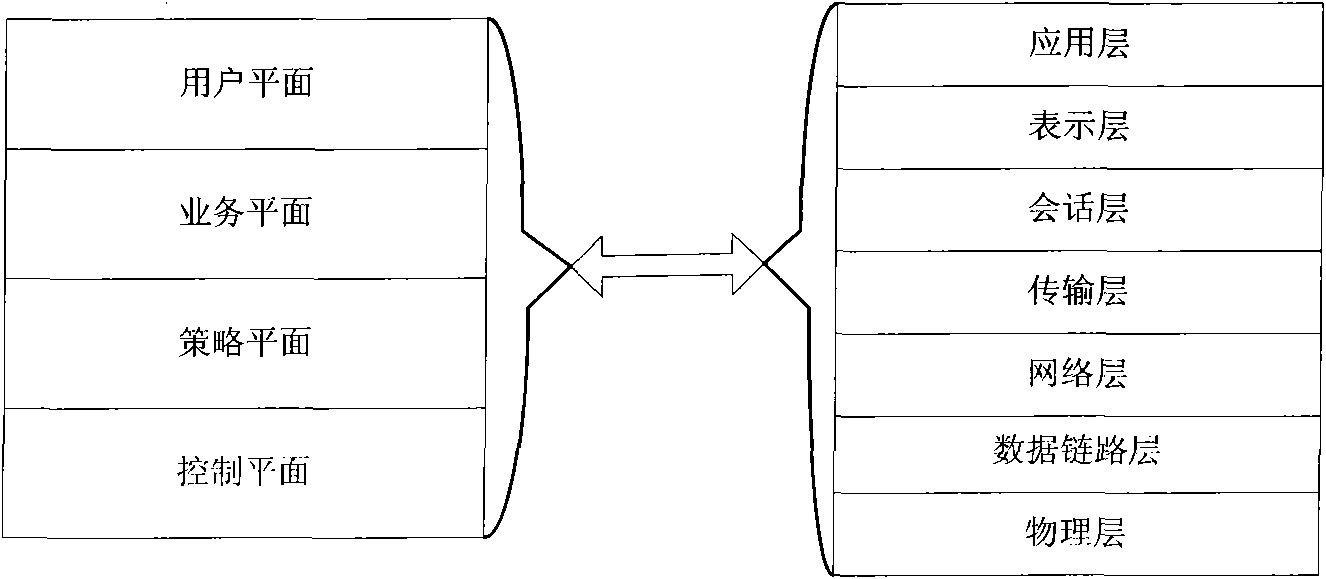

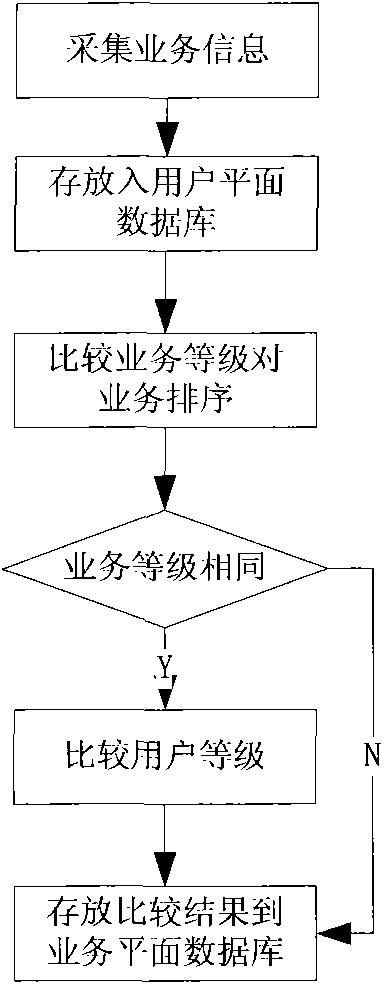

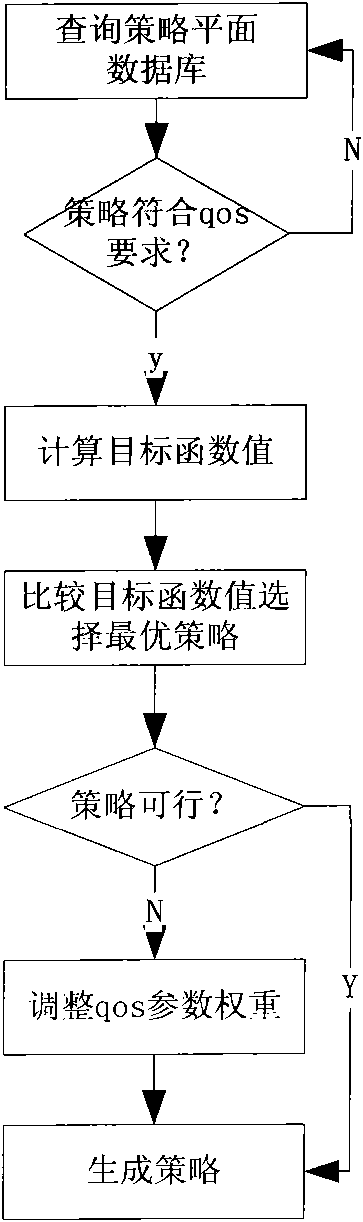

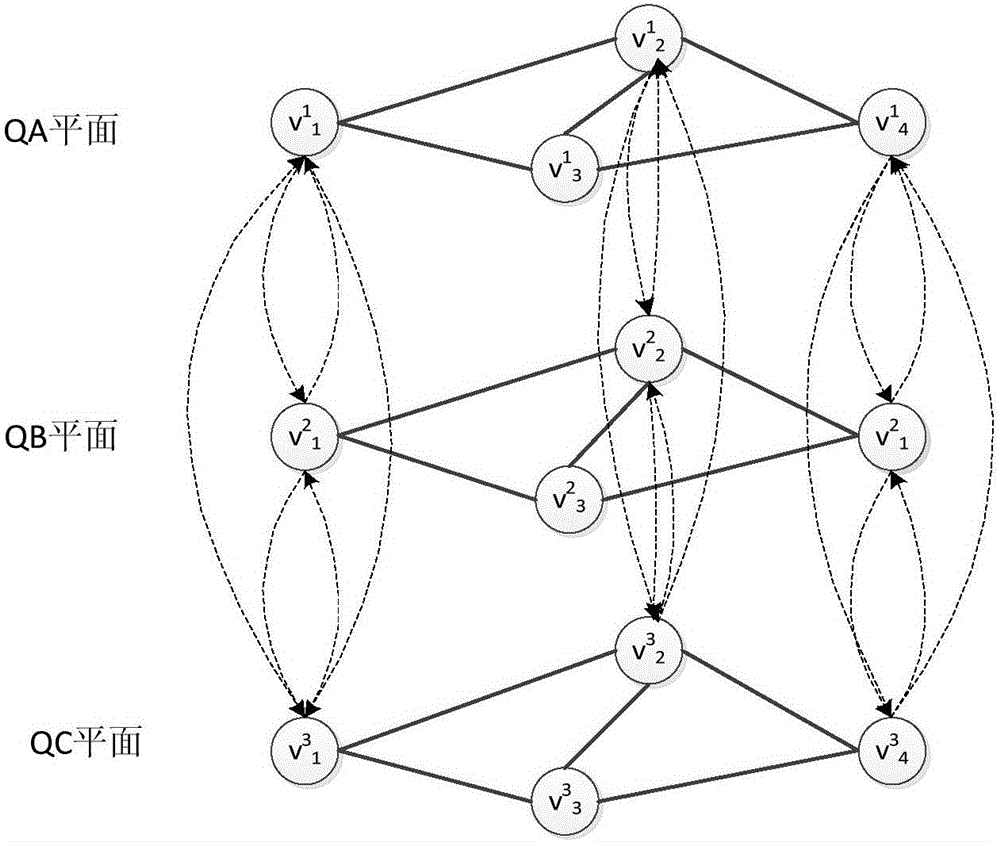

Dynamic adaptive cognitive network quality of service (QoS) mapping method

ActiveCN102025732AMeet different requirementsRealize the mappingTransmissionQuality of serviceResource utilization

The invention discloses a dynamic adaptive cognitive network quality of service (QoS) mapping method, comprising the following steps: grading a user on a user plane; comparing the service priority on a service plane; setting up an objective function on a strategy plane to adaptively adjust the weighting mode of the QoS of the strategy plane; and discussing the method for measuring obtained parameters on a control panel. By utilizing the method provided by the invention, the different requirements of different service-based cognitive network users for different QoS are met, the dynamic parameters among the user plane, the service plane, the strategy plane and the control plane are mapped, and the maximum utilization of network resources is realized.

Owner:NANJING UNIV OF POSTS & TELECOMM

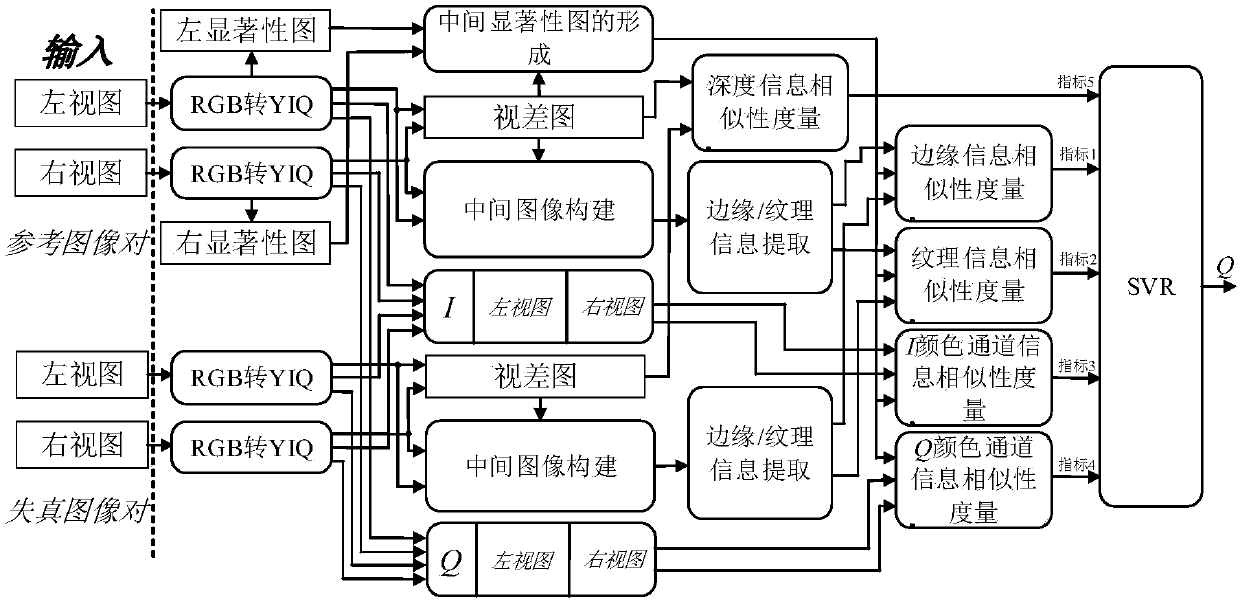

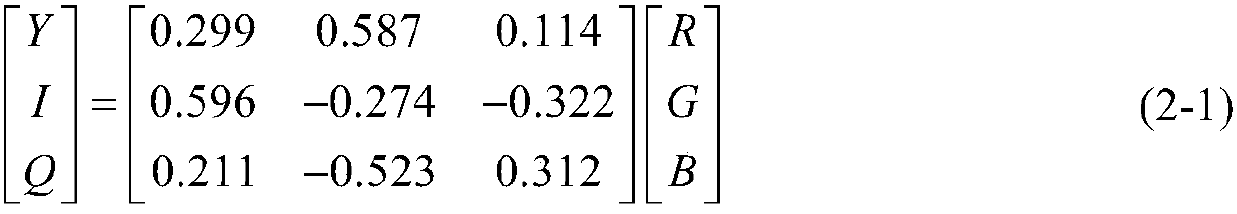

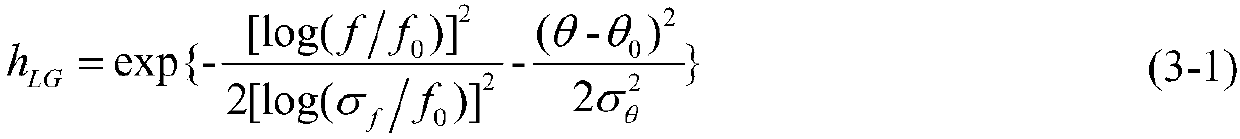

An objective evaluation method of full-reference stereo image quality based on visual salient image feature enhancement

ActiveCN109523506ARealize the mappingAchieve objective evaluationImage enhancementImage analysisObjective qualityIntermediate image

The invention discloses an objective evaluation method of full-reference stereo image quality based on visual salient image feature enhancement. At first, a stereoscopic image is converted from an RGBcolor space to a YIQ color space, The brightness components are extracted from Y-channel to obtain disparity map and visual saliency map, and then the left and right views of Y-channel are fused to obtain the intermediate image, and then the edge / texture and depth information features with significantly enhanced vision are extracted, and similarity measurement is carried out to obtain the corresponding measurement index. Secondly, color information features are extracted from I and Q channels of stereoscopic images, binocular fusion and similarity measurement are carried out, and color information metrics with significantly enhanced vision are obtained. Finally, all the metrics are predicted by support vector regression training, and the objective quality score is obtained. Experiments show that the objective evaluation and the subjective evaluation of the stereoscopic image quality proposed by the invention have good consistency, and the performance is superior to most existing stereoscopic image quality evaluation methods.

Owner:ZHEJIANG UNIV

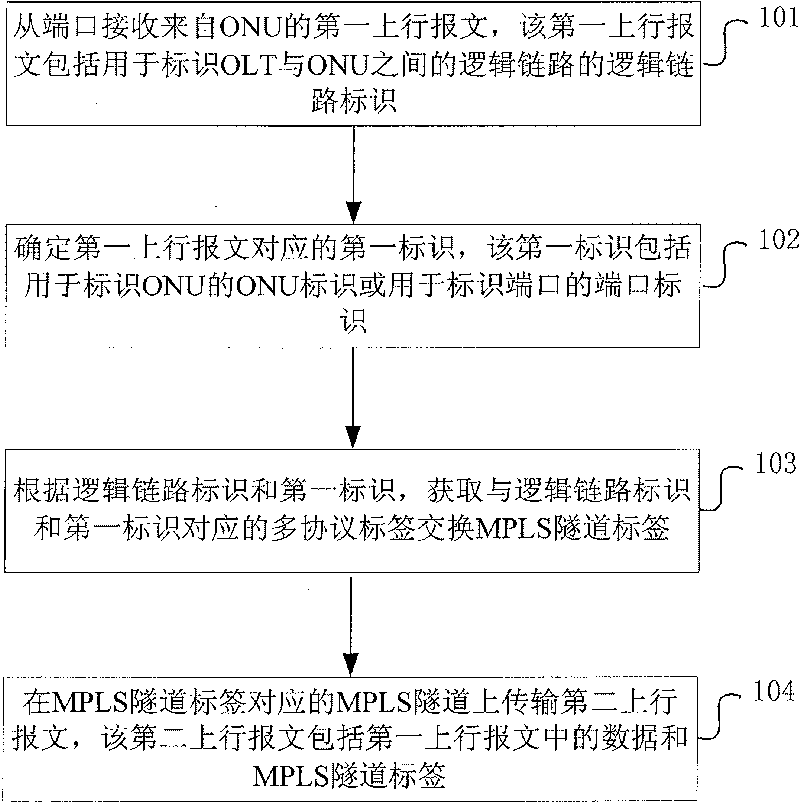

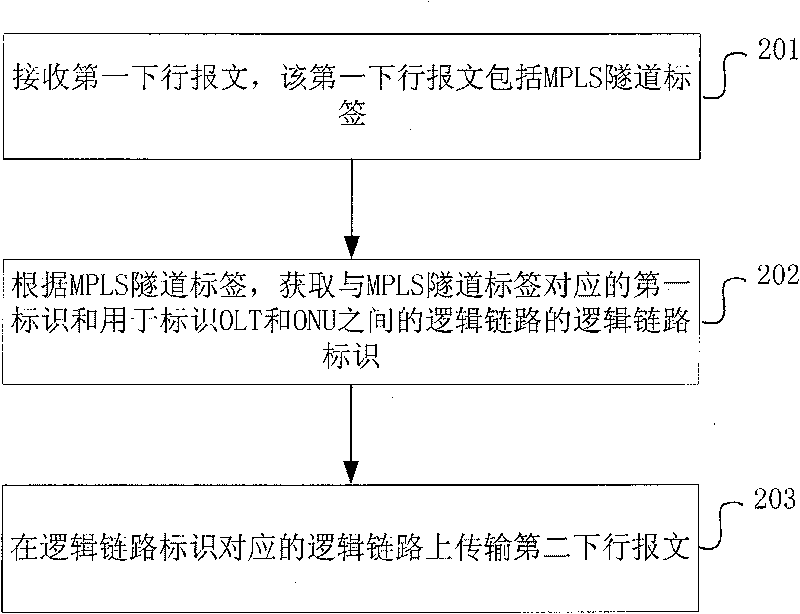

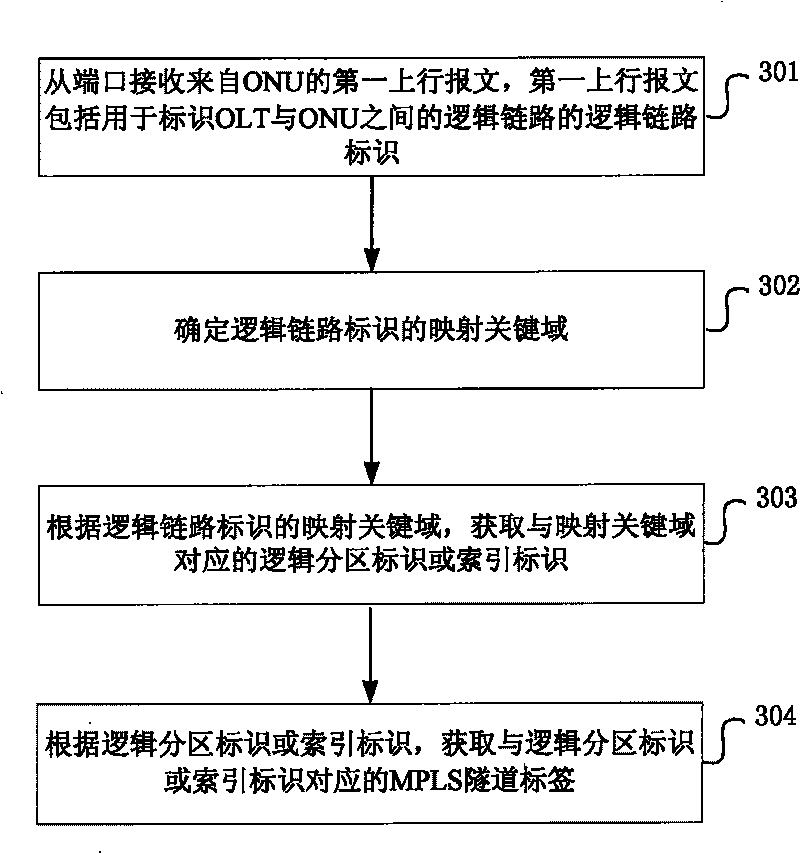

Method and system for transmission of message in optical communication system and optical line terminal

ActiveCN101729372ARealize the mappingUnlimited capacityMultiplex system selection arrangementsStore-and-forward switching systemsCommunications systemOptical line termination

The invention discloses a method and a system for the transmission of a message in an optical communication system and an optical line terminal, and belongs to the communication field. The method comprises: receiving, from a port, a first uplink message from an ONU, wherein the first uplink message includes a logic link identification; determining a first identification corresponding to the first uplink message, wherein the first identification comprises an ONU identification or a port identification; obtaining an MPLS tunnel label according to the logic link identification and the first identification; and transmitting a second uplink message on an MPLS tunnel corresponding to the MPLS tunnel label, wherein second uplink message comprises the data in the first uplink message and the MPLS tunnel label. The system comprises an optical network unit ONU and an optical line terminal OLT. The invention realizes the mapping between the logic link and the MPLS tunnel by establishing the corresponding relation between the MPLS tunnel and the logic link between the OLT and the ONT, so that the capacity for service configuration is not limited and the flexibility is strong.

Owner:HUAWEI TECH CO LTD

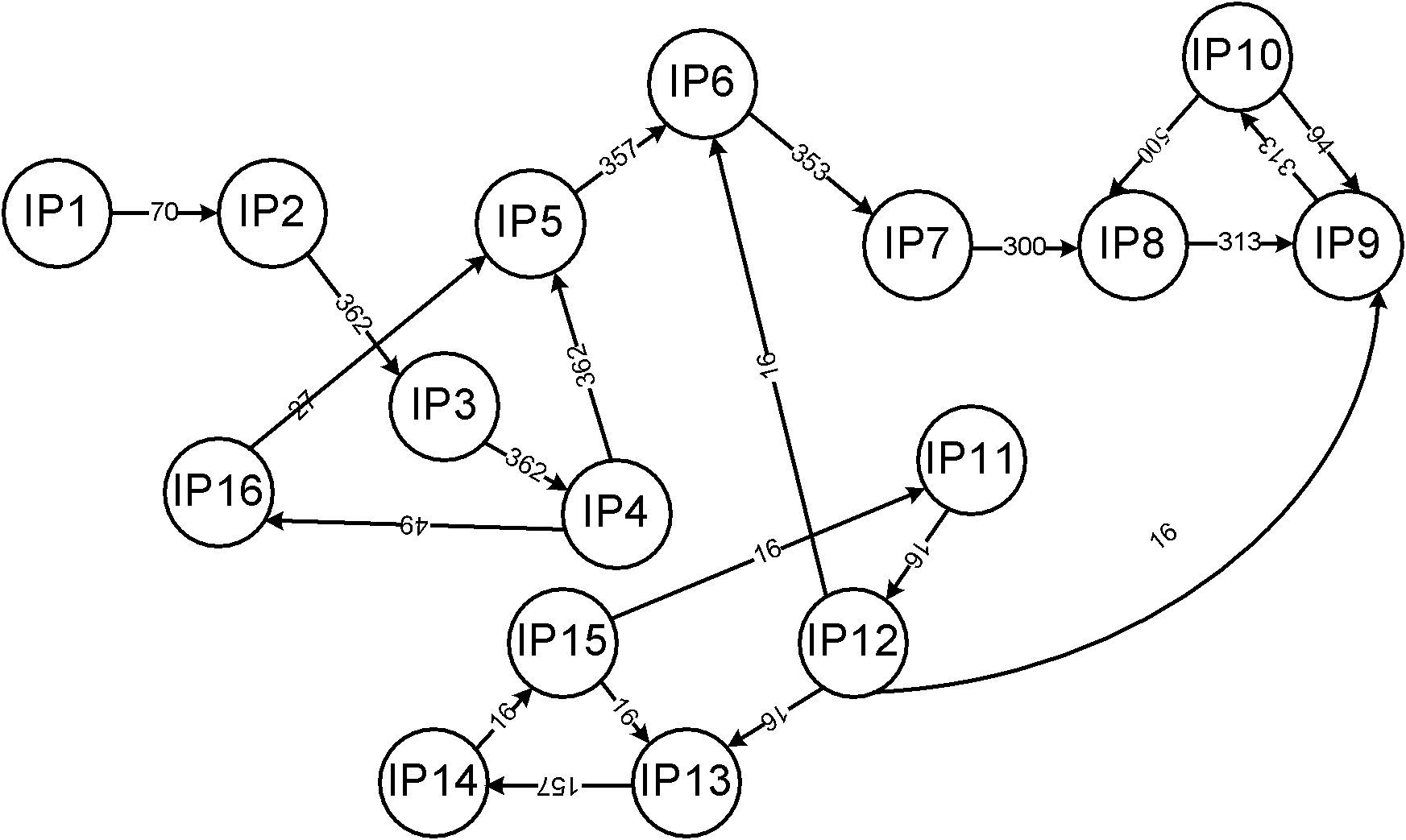

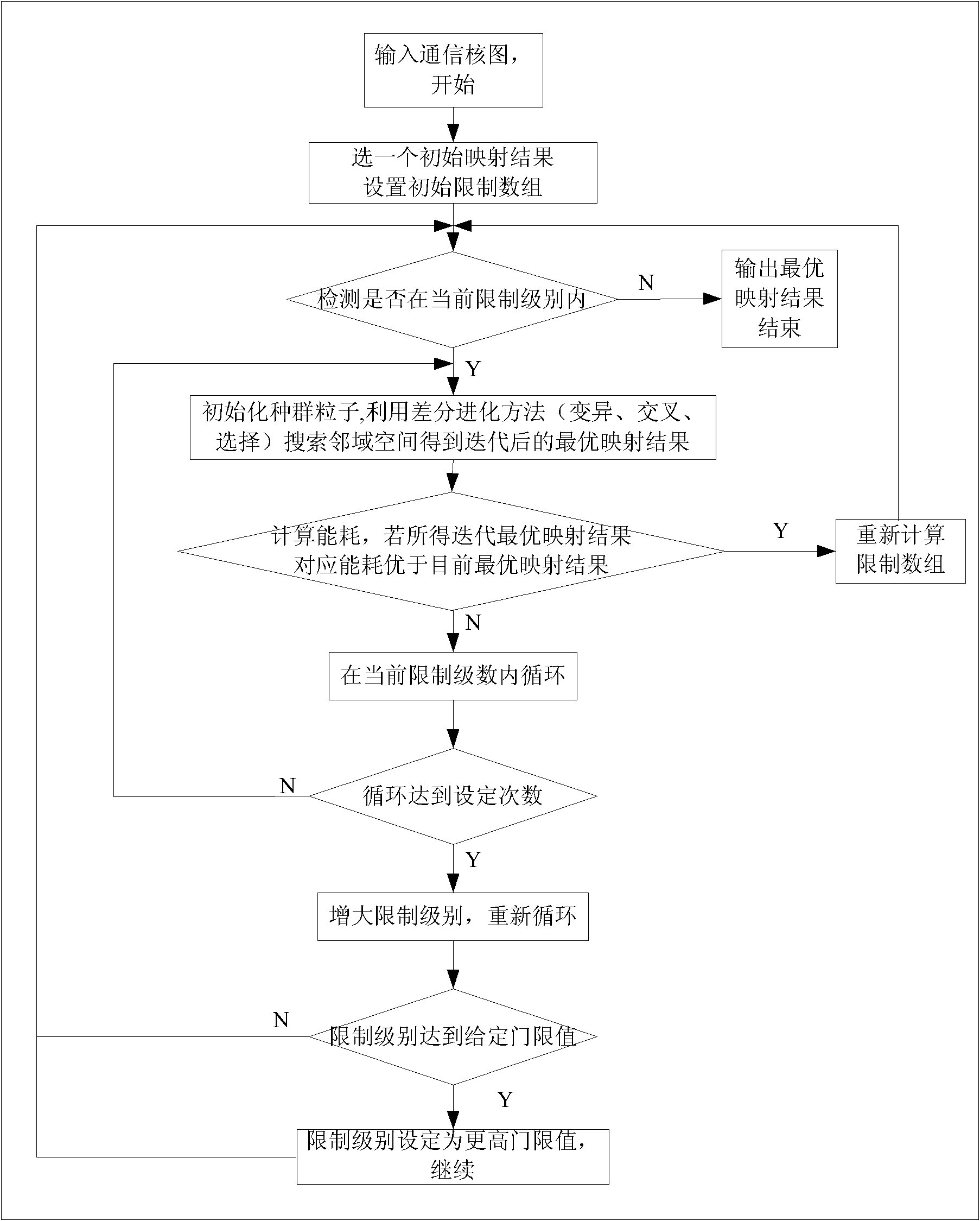

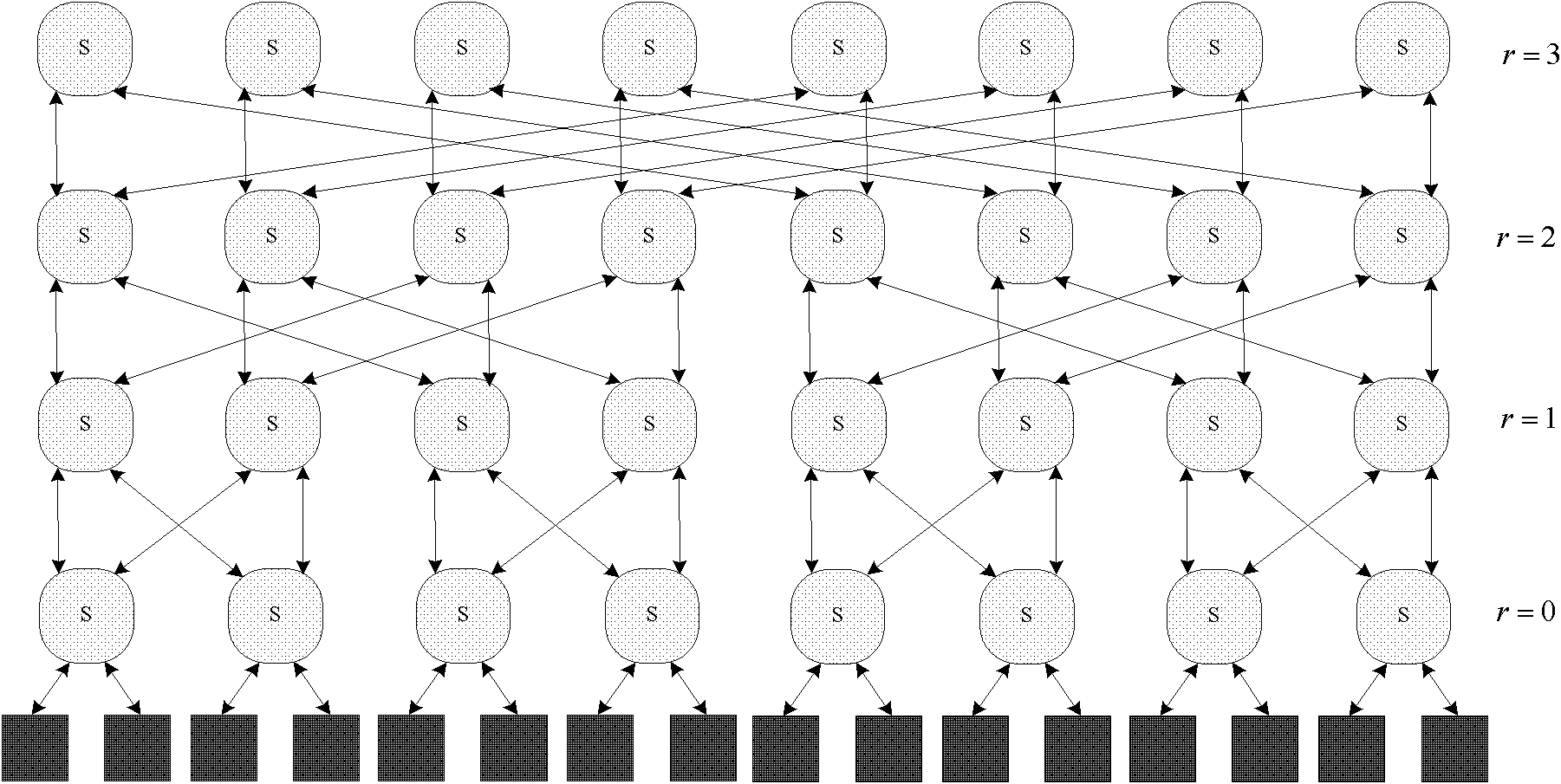

Fat tree type network-on-chip mapping method based on differential evolution and predatory search strategy

ActiveCN102325089AOvercoming the problem of being easily trapped in a local optimal solutionOptimum Energy Consumption ResultsData switching networksLocal optimumArray data structure

The invention discloses a fat tree type network-on-chip mapping method based on a differential evolution and predatory search strategy, which comprises the following steps of: (1) initializing the current optimal mapping result and defining a plurality of peripheral solutions which use any one solution as a center to form a limit array in the solution space; (2) setting limit arrays R[0], R[1],..., R[T-1] with the limit total amount of T at the periphery of the current optimal mapping result and defining the current limit variable to be R[i]; (3) searching the periphery of the current limit variable R[i] by adopting a differential evolution method; if a better solution is found out, updating the current optimal mapping result and turning back to the step (2); otherwise, turning to the step (4); (4) updating the current limit variable i which is equal to i plus 1; if i is smaller than T-1, turning back to the step (3); and otherwise, outputting the current optimal mapping result. By using the method, the problem of local optimum is solved through adjustment of limitation, the network energy consumption is greatly reduced, the mapping running time is reduced and the mapping of a low-energy consumption and rapid large-scale IP (Internet Protocol) core in the fat tree type network on a chip can be realized.

Owner:陕西光电子先导院科技有限公司

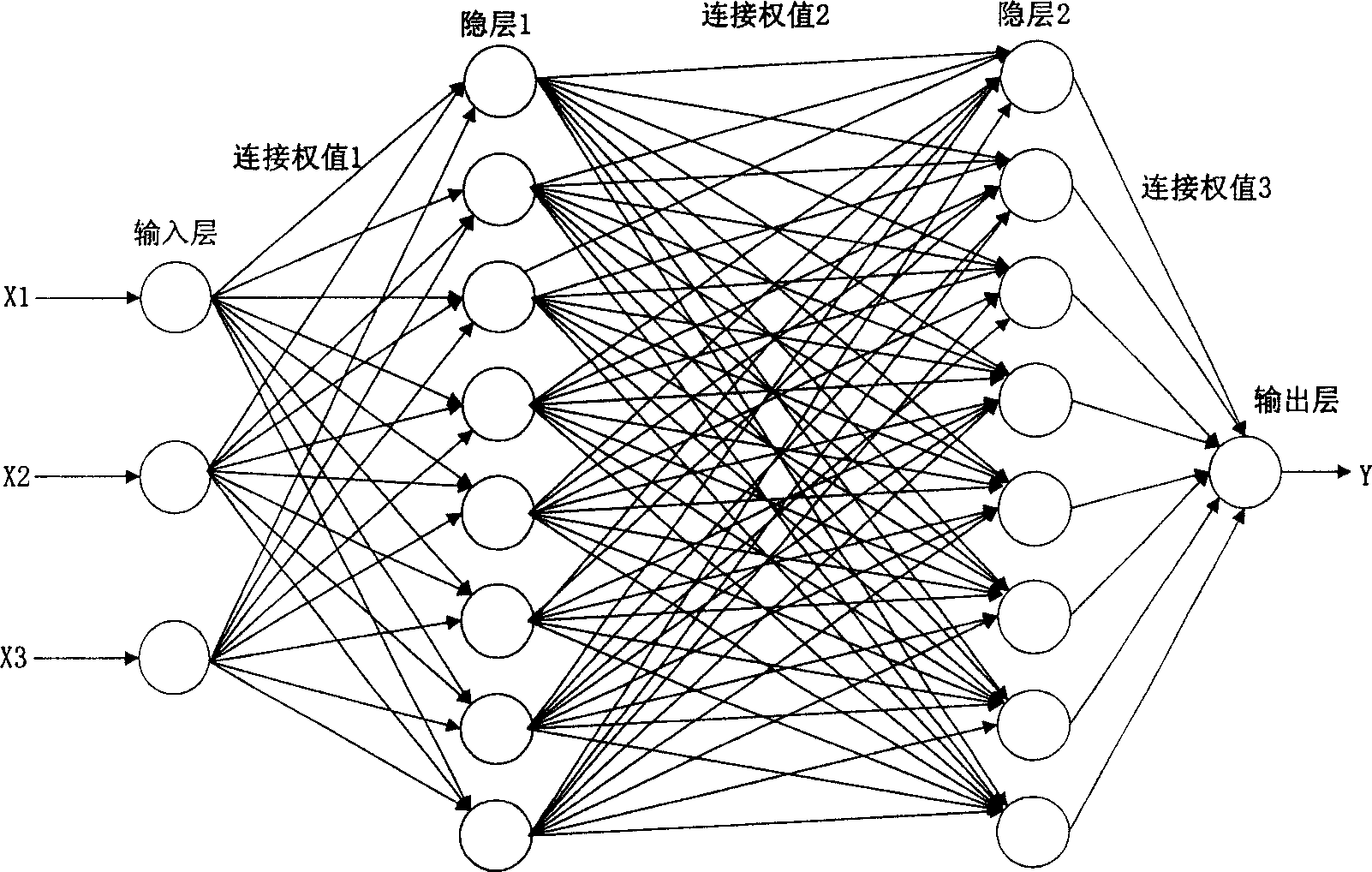

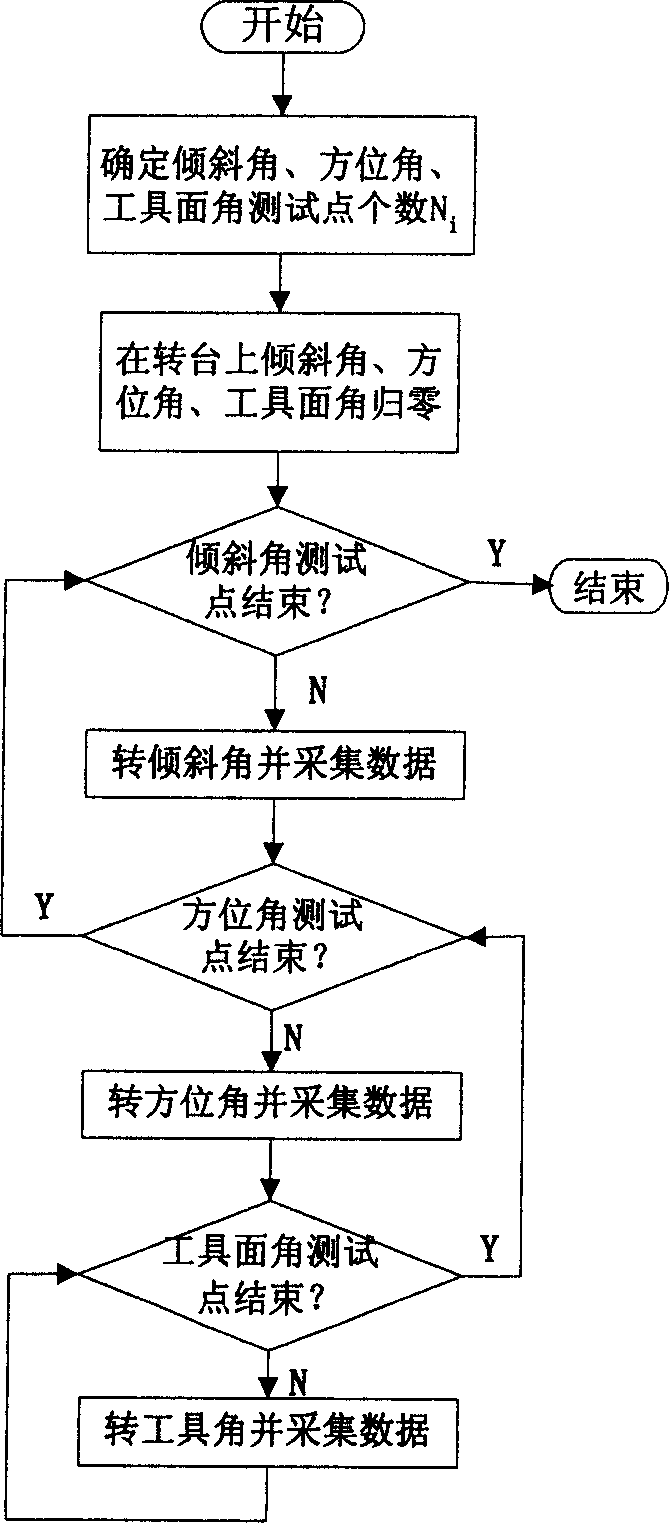

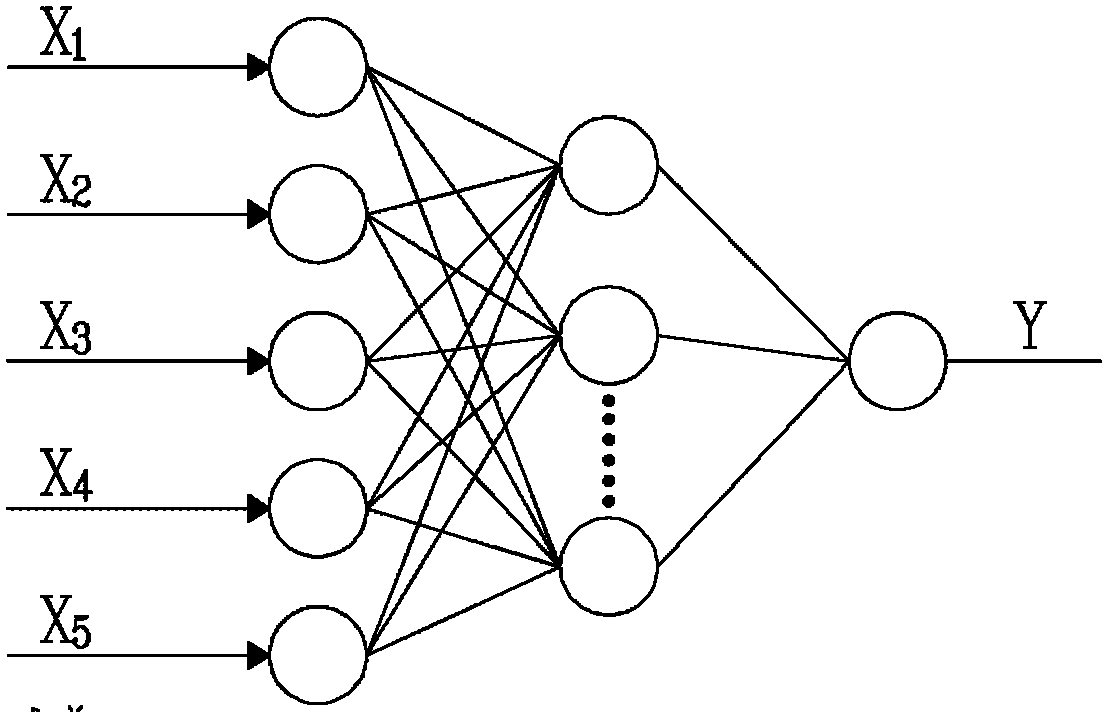

Well drilling slope level azimuth angle error compensating method based on neural network

InactiveCN1888384AOvercome the disadvantage of decreased accuracyRealize the mappingSurveyWell drillingNetwork model

The present invention relates to a borehole clinometer azimuth angle error compensation method based on neural network. Said method includes the following four steps: 1), according to the characteristics of borehole clinometer azimuth angle output signal defining structure model of neural network; 2), obtaining training sample of neural network; 3), making neural network training and obtaining optimum neural network model parameter; and 4), utilizing inclination angle, primarily-calculated azimuth angle and tool face angle to calculate real azimuth angle.

Owner:BEIHANG UNIV

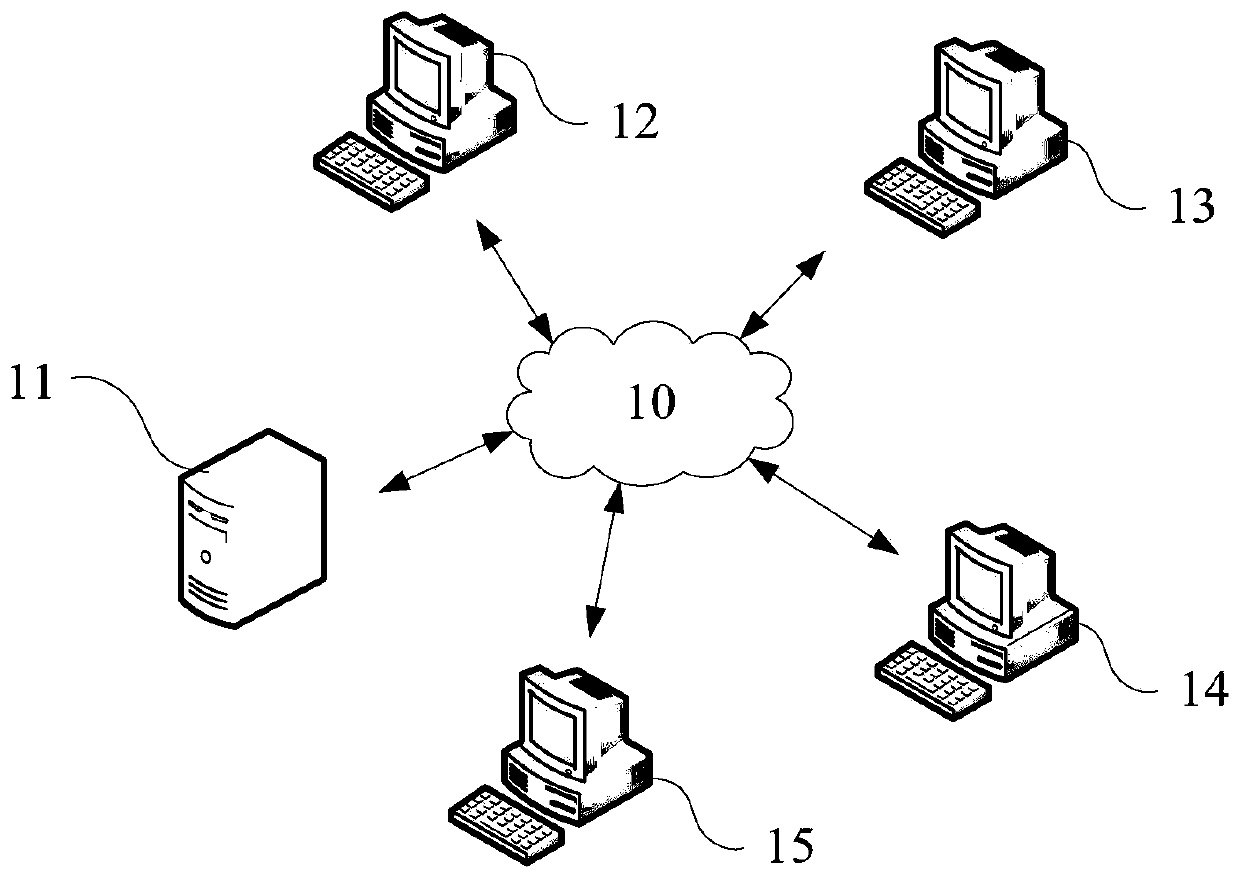

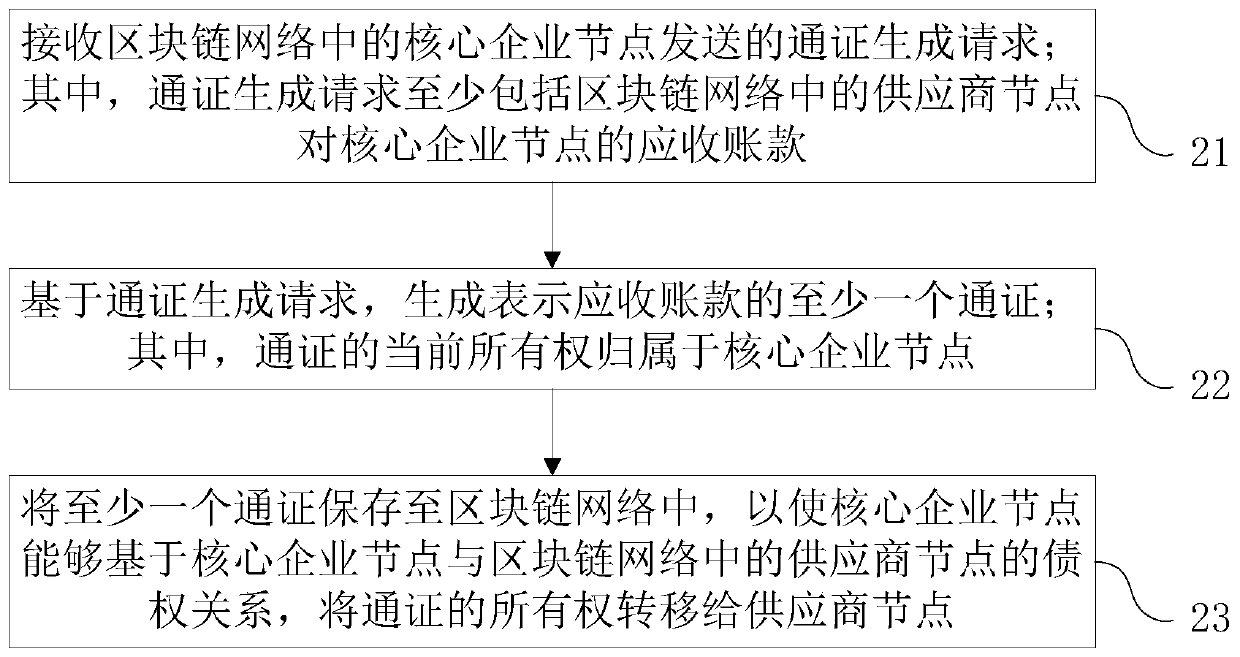

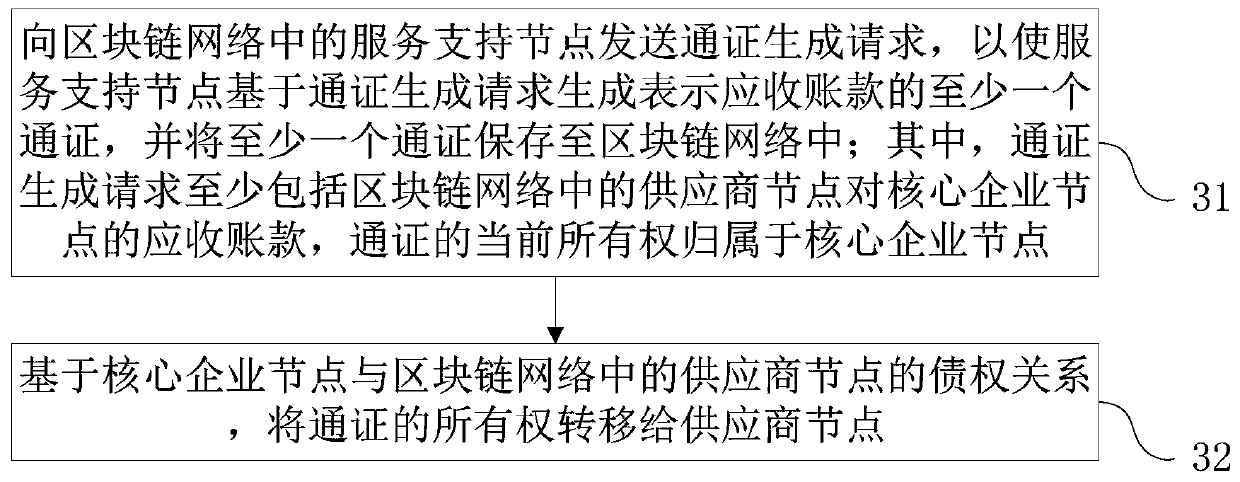

Token management method, supply chain financial system and electronic device

The invention discloses a token management method, a supply chain financial system and an electronic device, and the token management method comprises the steps: obtaining the token condition held bya supplier node from a block chain network; wherein the token is generated by a service support node in the block chain network based on receivable money of a supplier node to a core enterprise node;selecting at least part of pass held by the supplier node based on the pass condition; and transacting at least part of the token with a financial institution node or another supplier node in the block chain network. Through the above mode, the mapping of assets on the block chain is realized, the transfer and splitting of assets are facilitated, the flexibility of asset circulation is improved, and the fund circulation of small and medium-sized enterprises is ensured.

Owner:YGSOFT INC

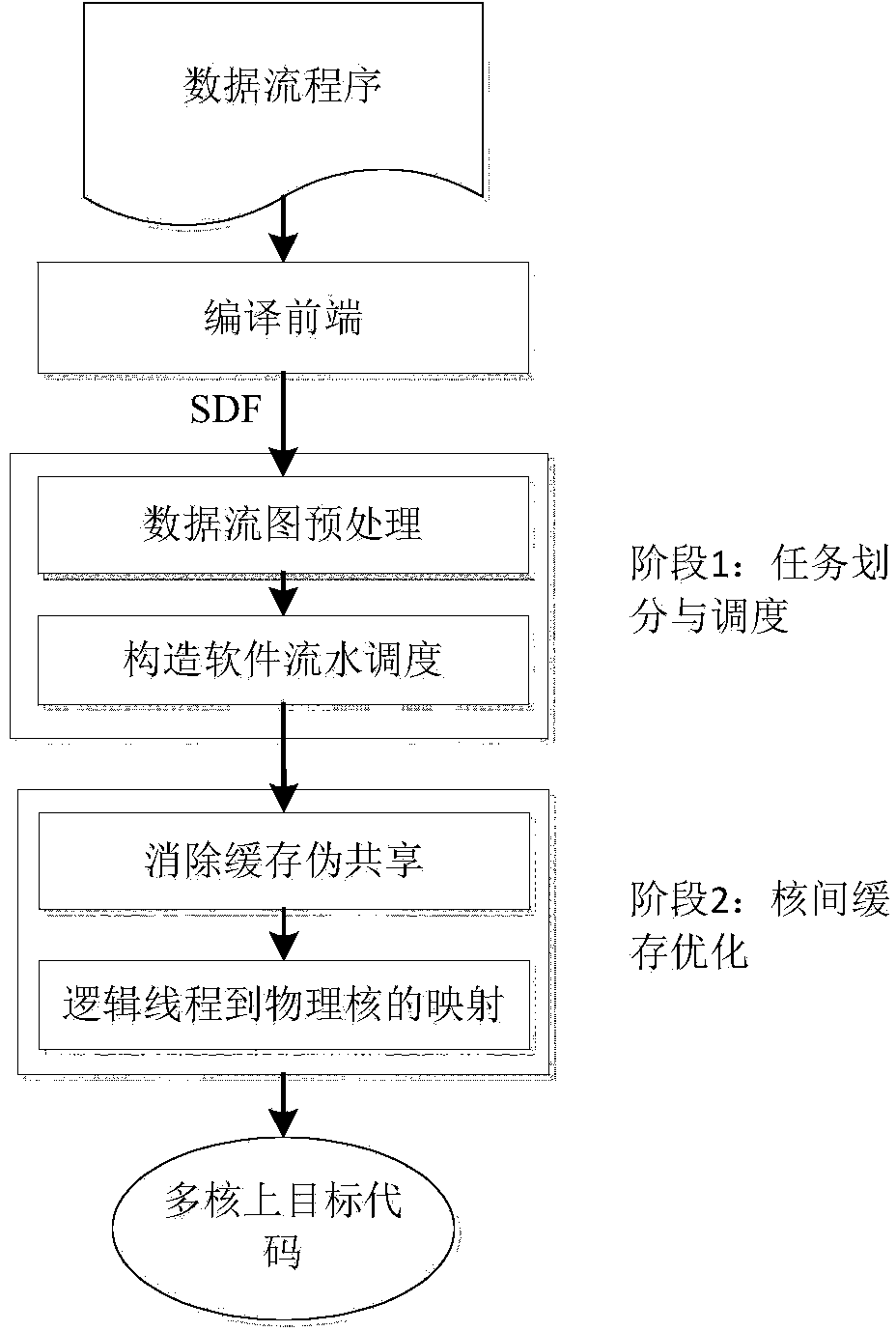

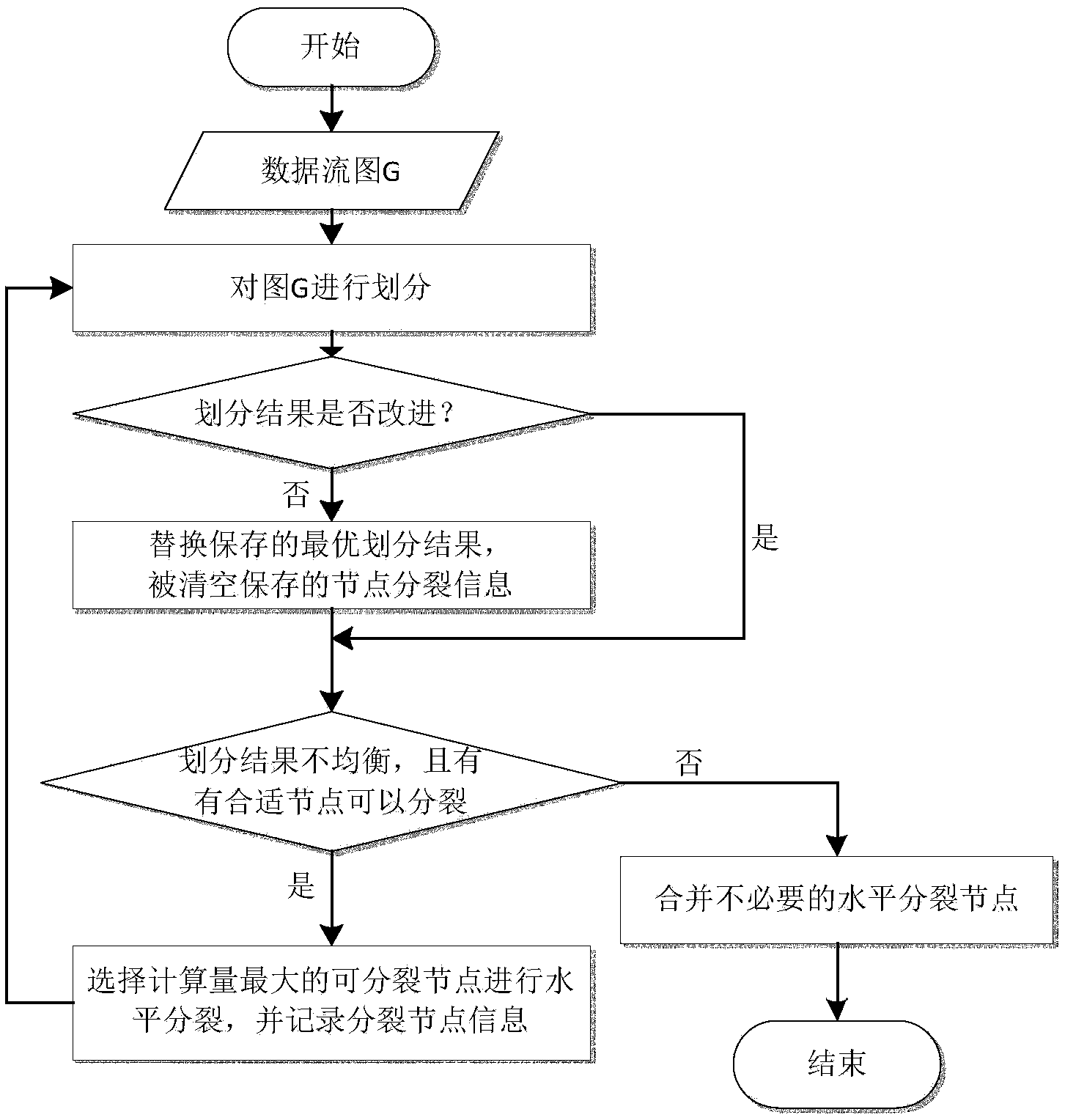

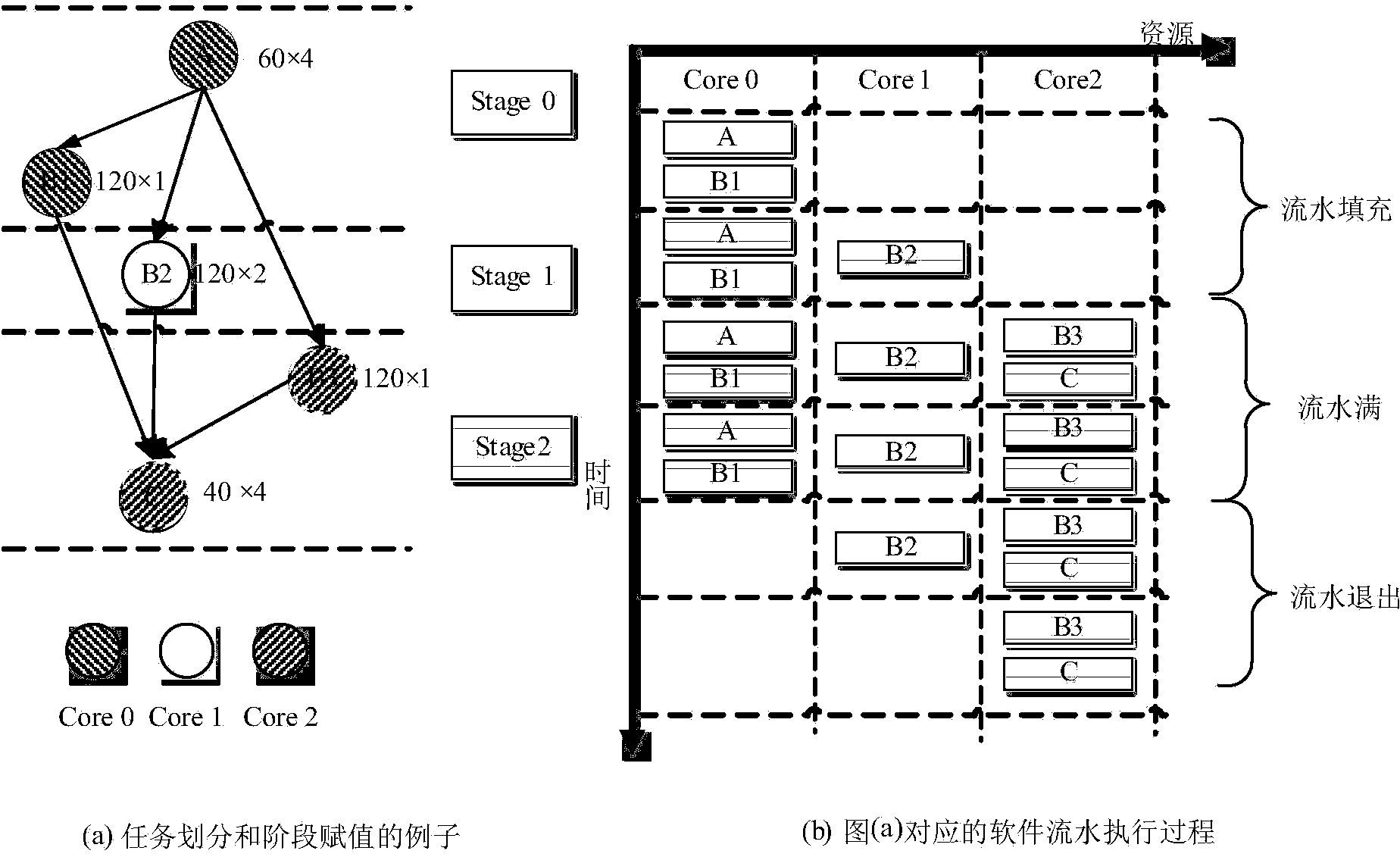

Data flow program scheduling method oriented to multi-core processor X86

ActiveCN103970602AReduce distractionsRealize the mappingProgram initiation/switchingResource allocationX86Parallel scheduling

The invention discloses a data flow program scheduling method oriented to a multi-core system. The method comprises the following steps that task partitioning of mapping from calculation tasks to processor cores is determined, and software pipeline scheduling is constructed; according to structural characteristics of a multi-core processor and execution situations of a data flow program on the multi-core processor, cache optimization among the cores is conducted. According to the method, data flow parallel scheduling and optimization related to the cache structure of a multi-core framework are combined, and high parallelism of the multi-core processor is brought into full play; according to the hierarchical cache structure and the cache principle of the multi-core system, access of the calculation tasks to a communication cache region is optimized, and the throughput rate of a target program is further increased.

Owner:HUAZHONG UNIV OF SCI & TECH

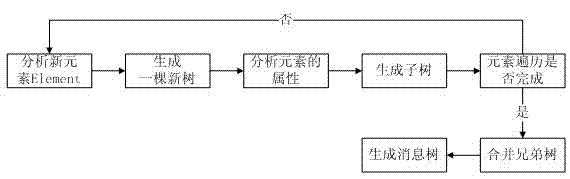

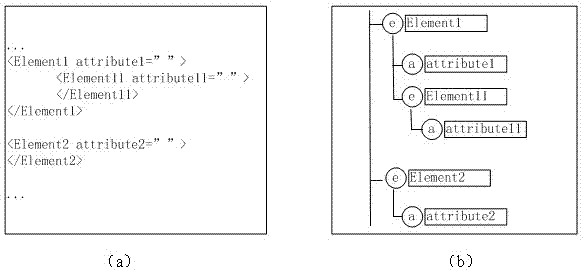

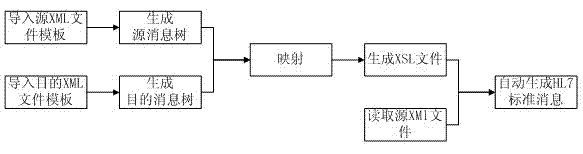

Method for generating HL7 (Health Level 7) message through mapping

The invention discloses a method for generating an HL7 (Health Level 7) message through mapping. The method comprises the steps of: firstly reading a source XML (Extensible Markup Language) file template and a destination XML file template; afterwards parsing the source XML file template and the destination XML file template so as to generate a source message tree and a destination message tree respectively; subsequently mapping the source message tree and the destination message tree so as to generate an XSL (Extensible Stylesheet Language) file; finally reading the resource XML file according to the XSL file and generating a corresponding message with a standard HL7 format automatically. According to the method provided by the invention, the mapping among nodes are realized through simple line connection and an XSL document recoded with all mappings is generated automatically; and with the method, a custom message can be converted into a standard HL7 message, and the standard HL7 message can be converted into the custom message as well, when the HL7 message is led into the source message tree and a custom message template is led into the object message tree.

Owner:杭州铭唐信息科技有限公司

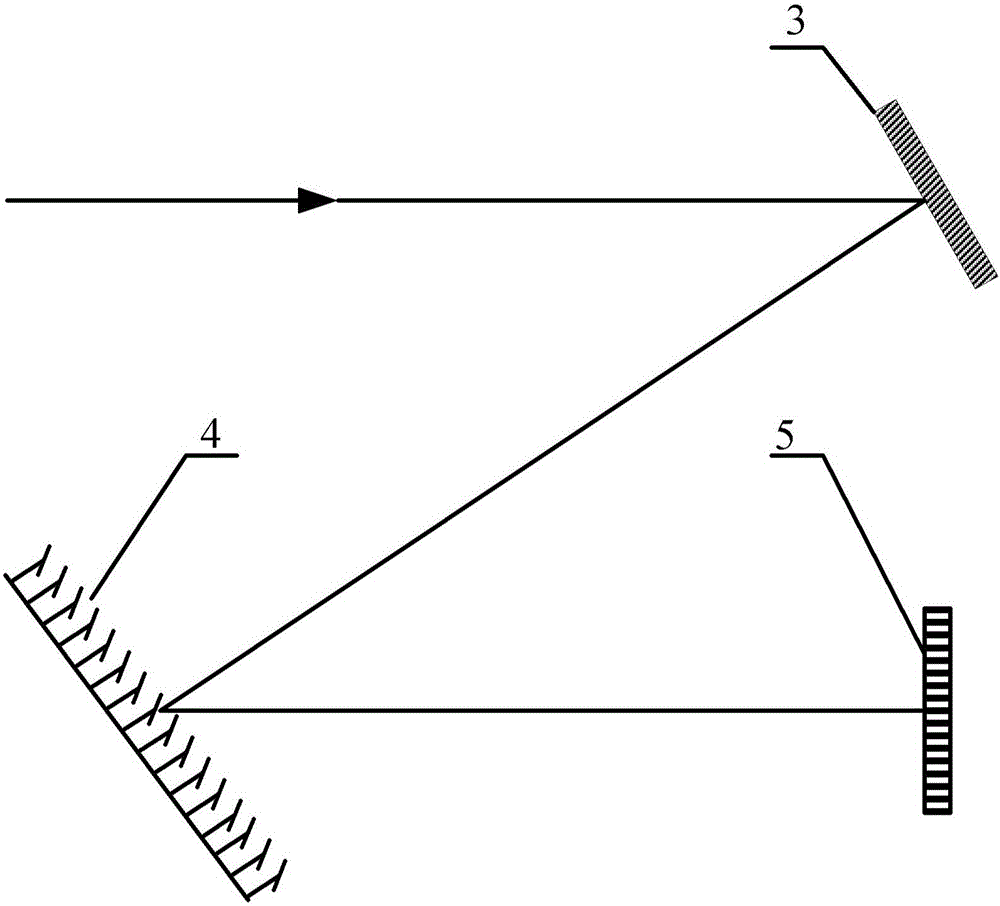

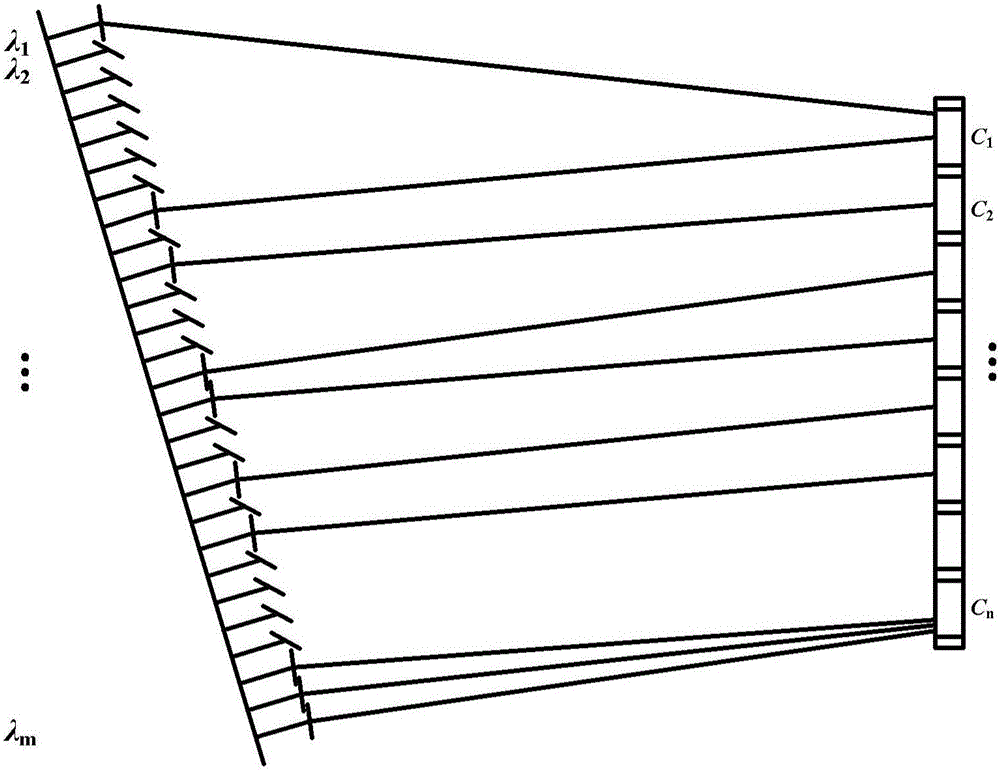

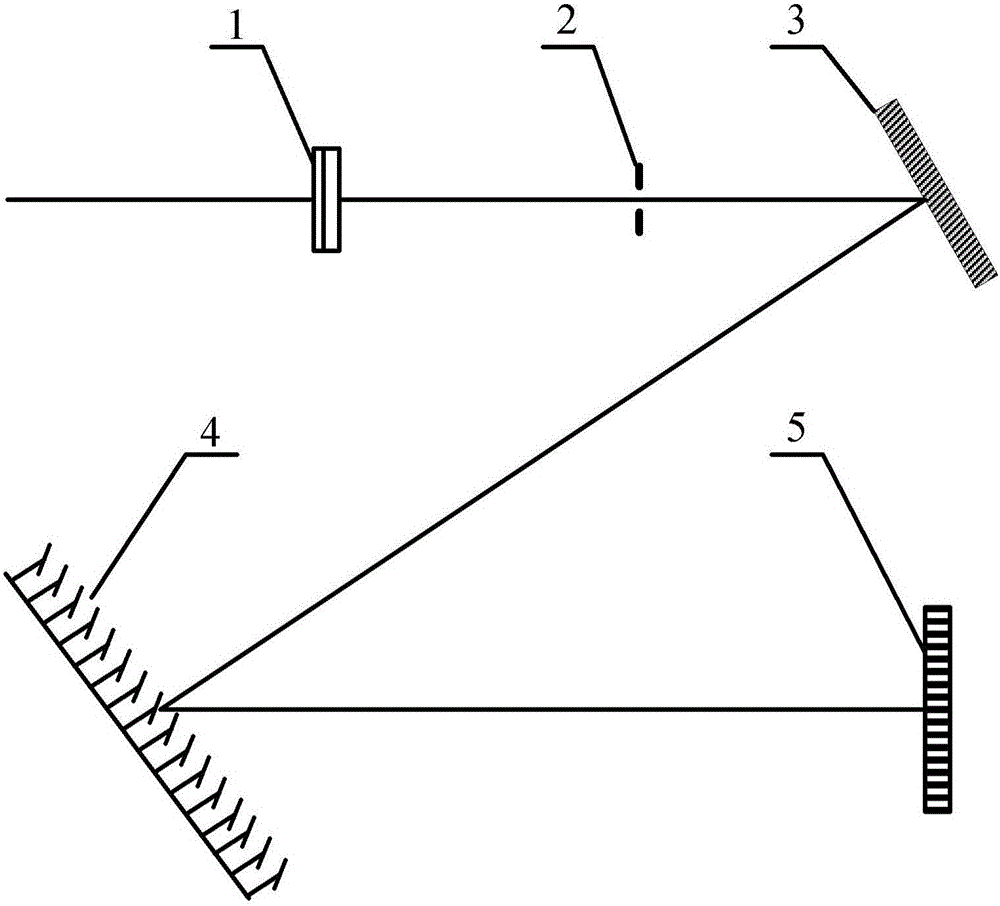

Light-splitting and spectrum-selecting device used for high spectral laser radar

InactiveCN106125090AHigh resolutionEasy to implementElectromagnetic wave reradiationImage resolutionLinear array

The invention provides a light-splitting and spectrum-selecting device used for a high spectral laser radar, including a blazed grating, a micromirror array and an APD linear array. The blazed grating performs light splitting of a target echo to obtain spatially-continuous monochromatic light, and projects the spatially-continuous monochromatic light to the micromirror array. Micro reflecting mirrors in the mircromirror array are overturned for reflecting monochromatic light of different center frequency spectrums to the APD linear array for detection, wherein in the condition of overturning a single row of micro reflecting mirrors, the minimal resolution ratio spectrum is obtained, and by controlling combined overturning of multiple rows of micro reflecting mirrors, a combined spectrum can be obtained. The invention effectively improves the spectrum resolution of the high spectral laser radar.

Owner:ACAD OF OPTO ELECTRONICS CHINESE ACAD OF SCI

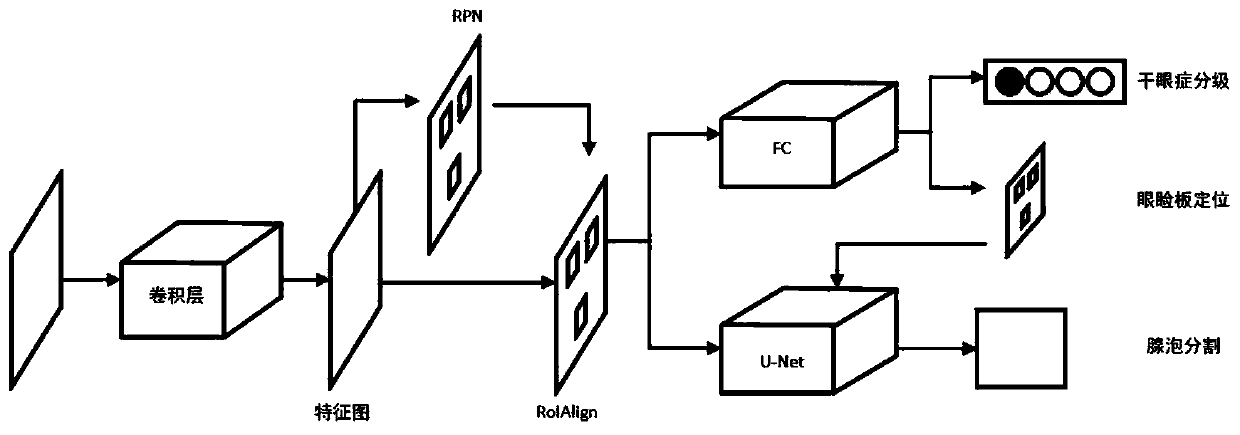

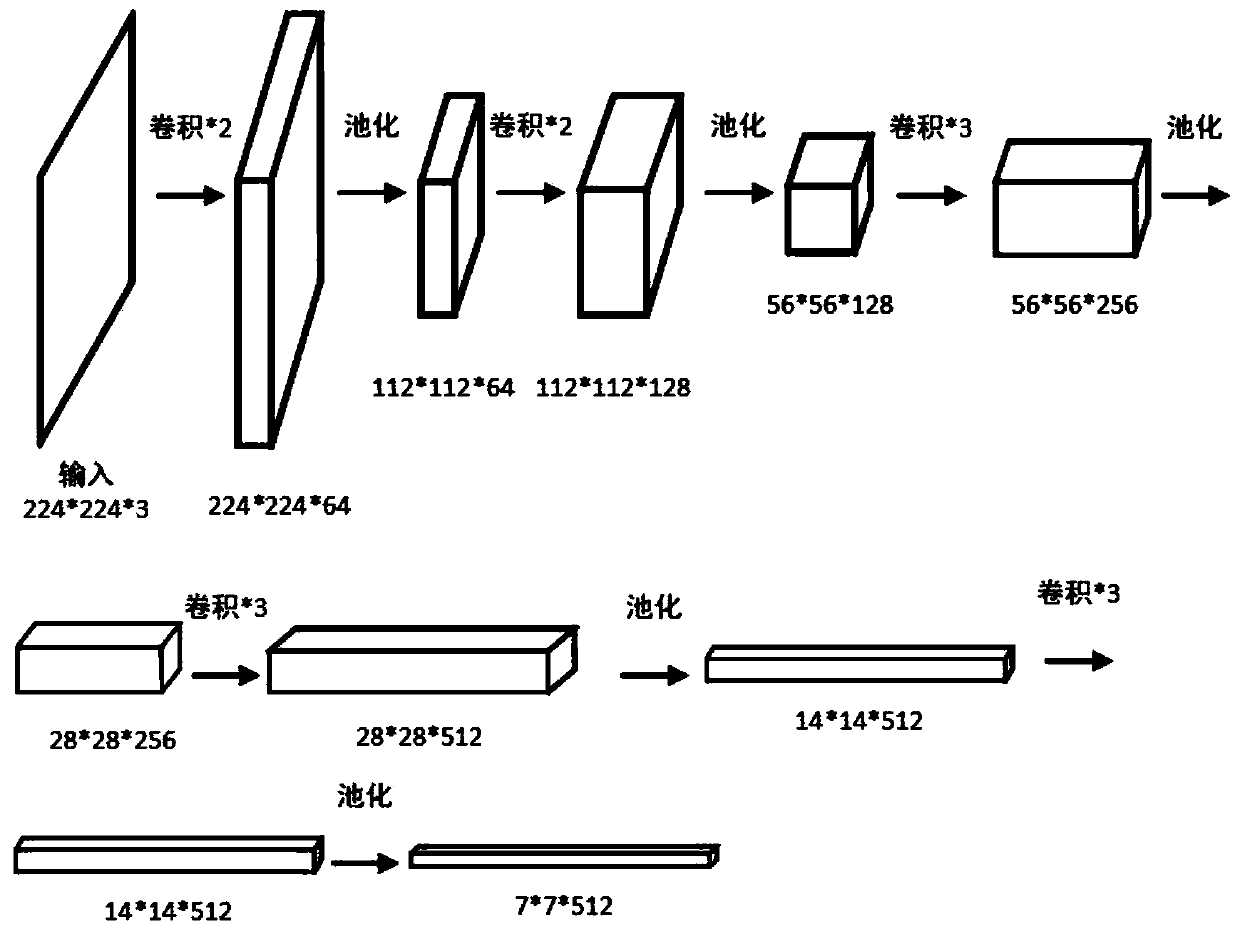

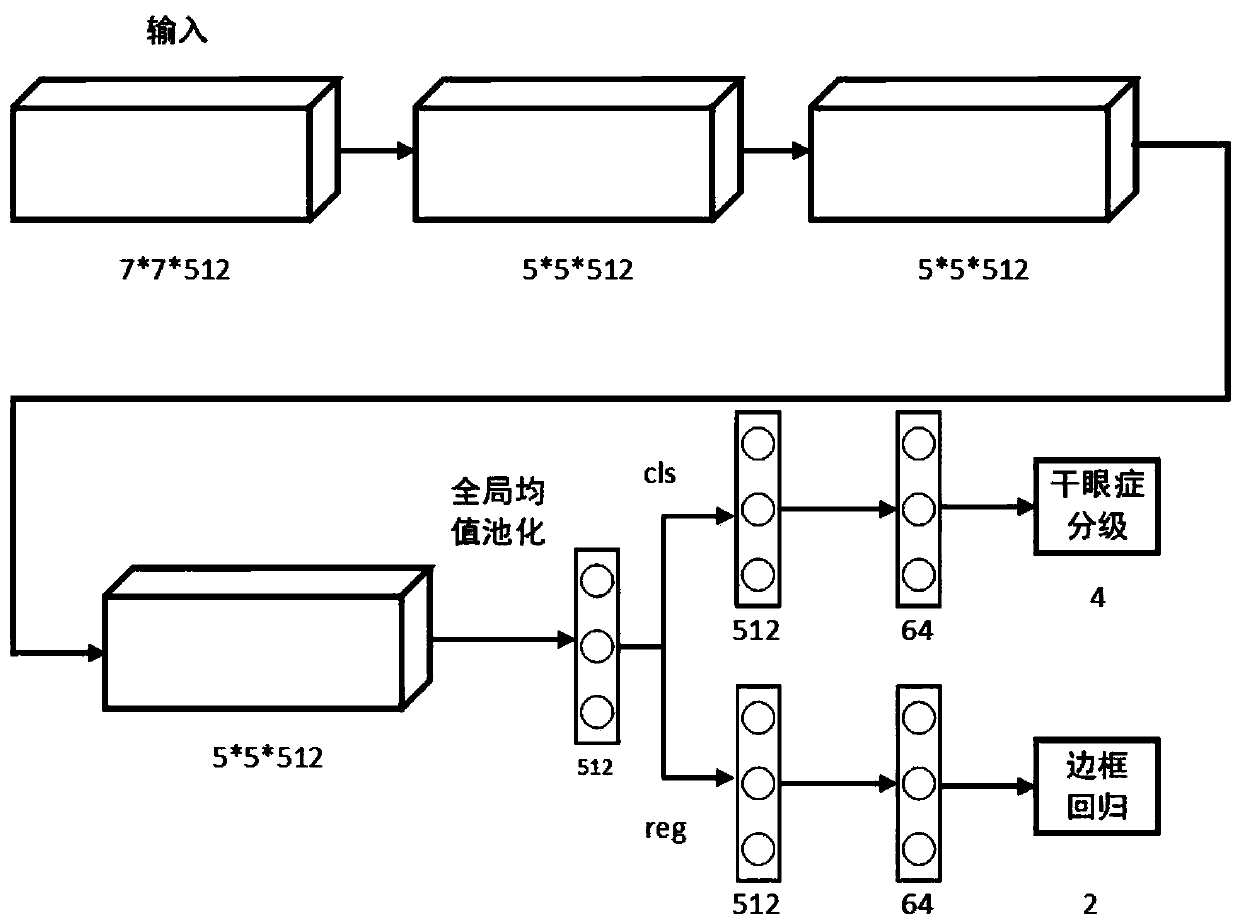

Xerophthalmia grading evaluation system based on regional adaptive multi-task neural network

PendingCN111127431AImprove diagnostic efficiencyAccelerateImage enhancementImage analysisMachine learningComputer memory

The invention discloses a xerophthalmia grading evaluation system based on a regional adaptive multi-task neural network. The system comprises a computer memory, a computer processor and a computer program which is stored in the computer memory and can be executed on the computer processor, wherein a trained xerophthalmia grading evaluation model is stored in the computer memory, and the xerophthalmia grading evaluation model comprises a VGG16 network, a regional recommendation network and a U-shaped full convolutional network. When the computer processor executes a computer program, the following steps are achievd by comprising steps of obtaining a to-be-tested original eyelid plate infrared image to carry out gray scale preprocessing, and carrying out bilateral filtering processing on asingle-channel gray scale image obtained after preprocessing; and inputting the processed image into a xerophthalmia grading evaluation model to obtain a xerophthalmia grading result, an eyelid platepositioning result and an alveolar segmentation result. According to the invention, automatic analysis of the eyelid plate infrared photograph can be realized, and auxiliary diagnosis of xerophthalmiagrading can be effectively carried out.

Owner:杭州求是创新健康科技有限公司

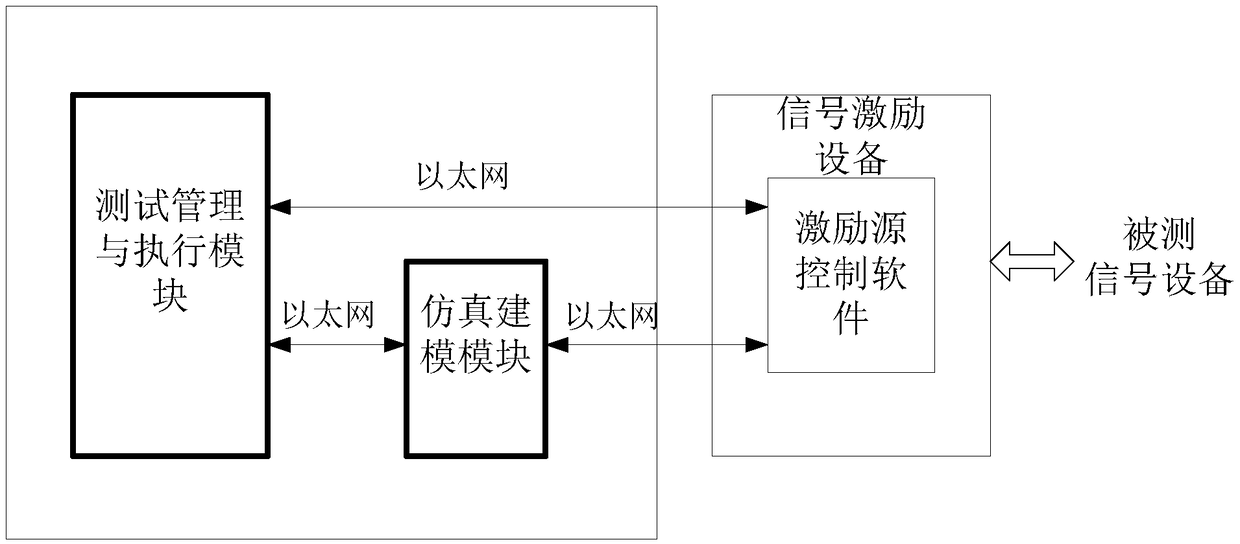

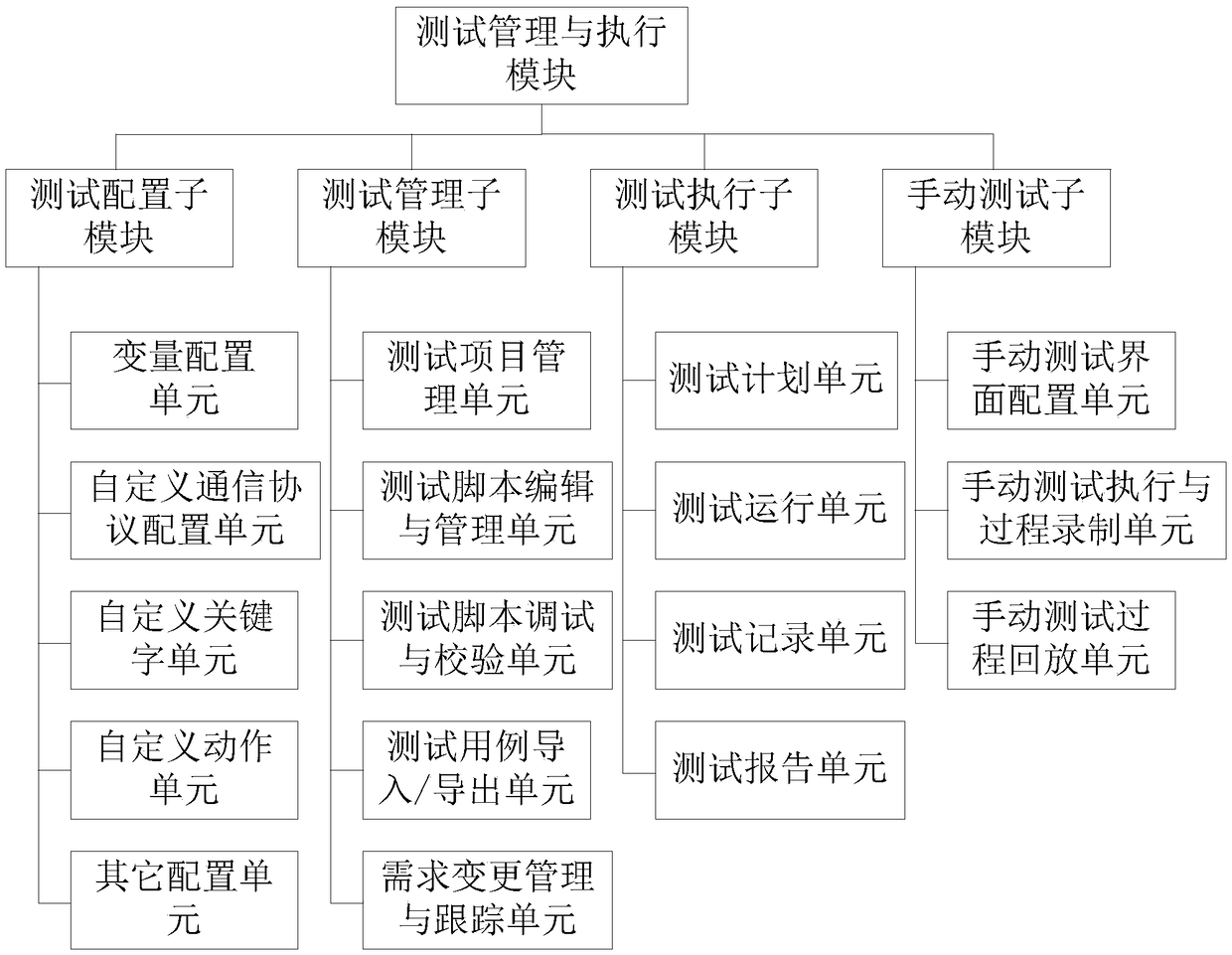

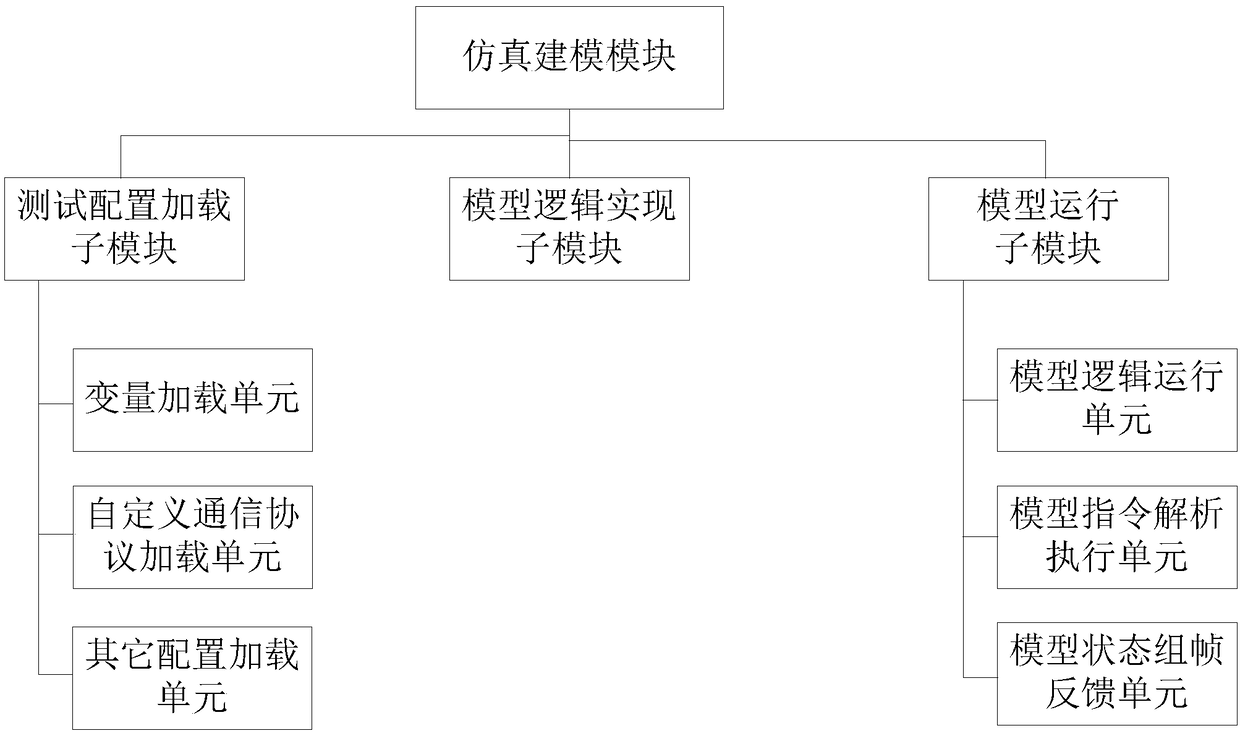

Universal automatic test system for rail transit signaling equipment

ActiveCN109062777AHigh degree of automationImplement configurationHardware monitoringSoftware testing/debuggingTest scriptSystem requirements

The invention discloses a universal automatic test system for rail transit signaling equipment, which has flexible interface and protocol configuration, automatic test and functions of equipment modeling and project management. The technical scheme is as follows: using keyword-based drivers, extensible, Easy-to-write test sequences are used as a way to edit test scripts, as the communication interface transmission mode require for supporting the signal equipment of the rail transit is interconnected with the test excitation source through the Ethernet, the coupling between the test excitationsource and the t excitation source is avoided, and the test interface mode can be added and configured according to the actual test interface requirement, so that the configuration of the communication protocol and the semantic definition and mapping are conveniently realized. Realize the closed-loop test management including system requirements, test requirements, requirements change management,test case management, test script framework import generation, test script editing, test plan generation, test plan execution, test process record, test report generation, automatic generation of round test plan according to defects, and so on, improve the degree of automation.

Owner:HUNAN CRRC TIMES SIGNAL & COMM CO LTD

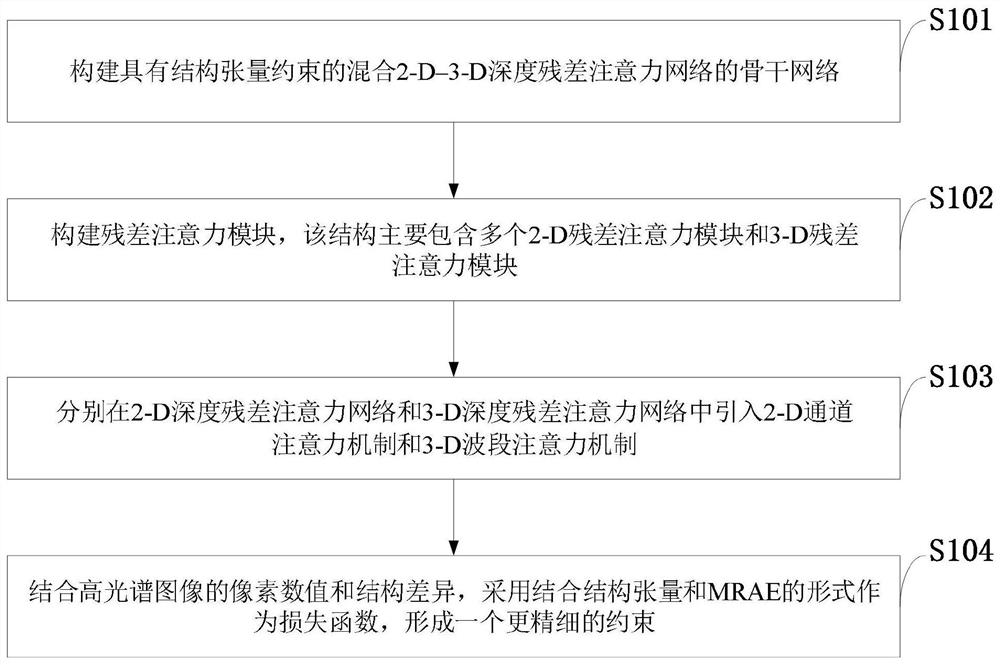

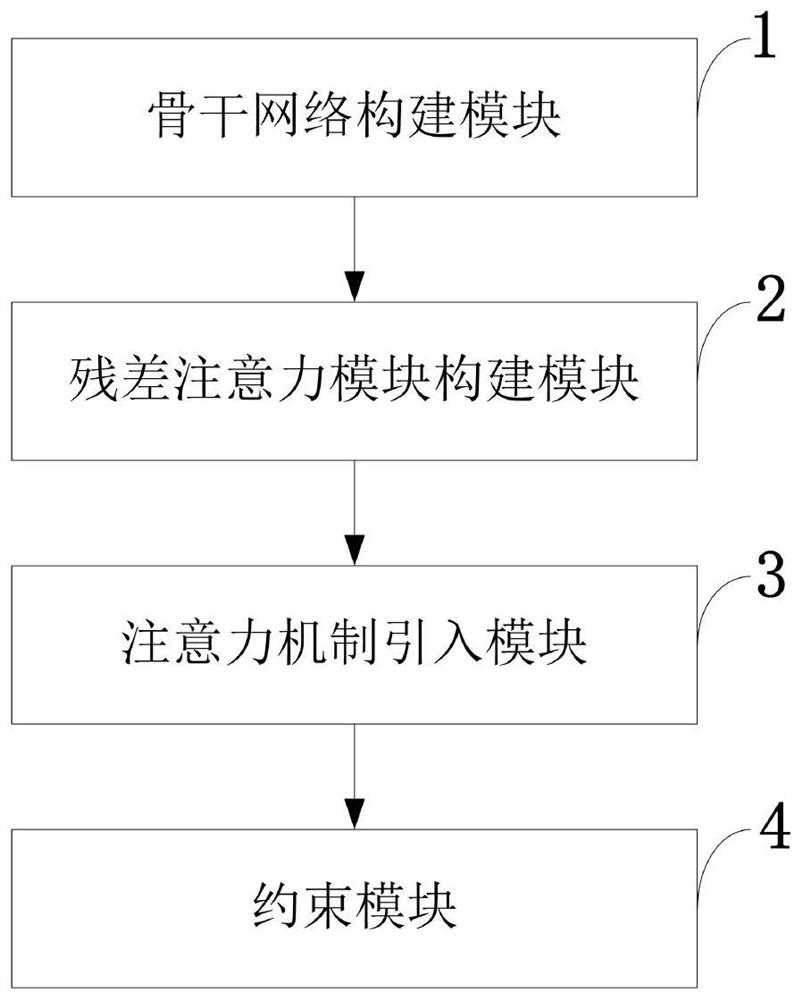

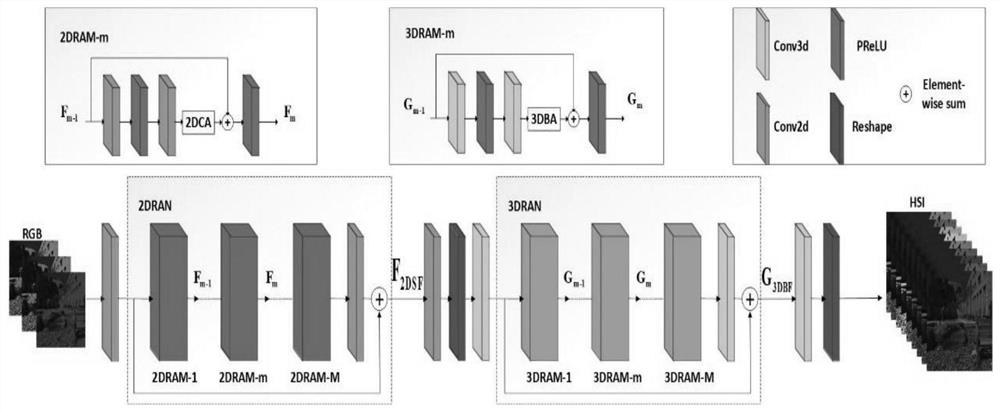

RGB image spectrum reconstruction method and system, storage medium and application

PendingCN112116065ARealize the mappingEnhancing Discriminative Learning AbilitySpectrum investigationNeural architecturesPattern recognitionHyperspectral image processing

The invention belongs to the technical field of hyperspectral image processing, and discloses an RGB image spectrum reconstruction method and system, a storage medium and application, and the method comprises the steps: constructing a backbone network of a hybrid 2D-3D deep residual attention network with structural tensor constraints; constructing a residual attention module, wherein the residualattention module comprises a plurality of 2-D residual attention modules and 3-D residual attention modules; respectively introducing a 2-D channel attention mechanism and a 3-D waveband attention mechanism into the 2-D deep residual attention network and the 3-D deep residual attention network; in combination with pixel values and structural differences of the hyperspectral image, adopting a mode of combining a structure tensor and MRAE as a loss function, and a finer constraint is formed. According to the method, end-to-end mapping from the RGB image to the hyperspectral image is realized,the characteristic response of the channel and the waveband dimension is self-adaptively recalibrated, the discriminant learning ability is enhanced, and the finer and more accurate hyperspectral image can be recovered in the training process.

Owner:XIDIAN UNIV

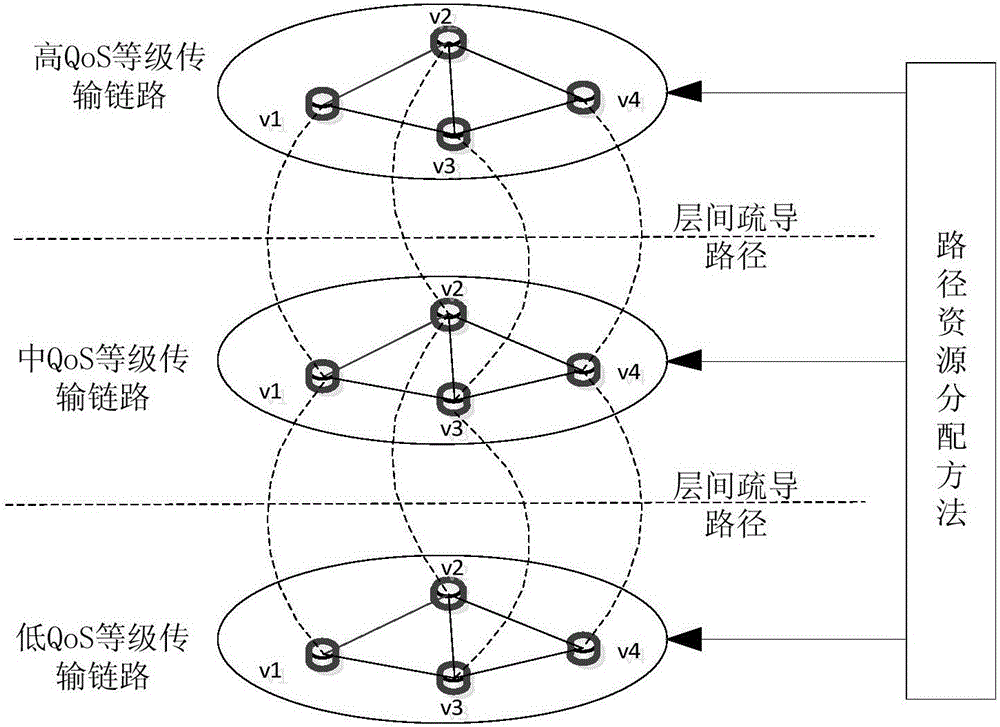

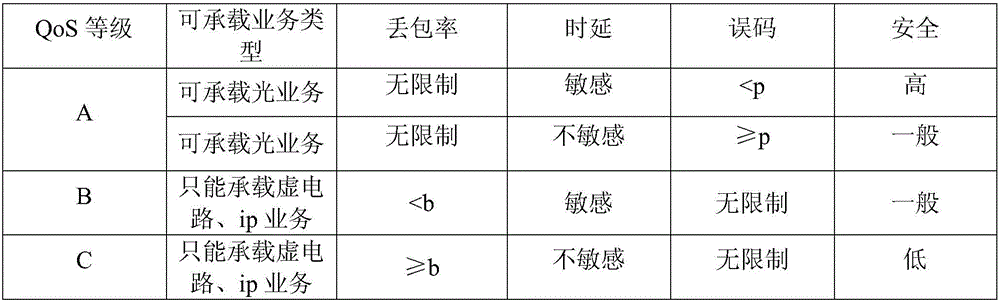

QoS differentiation-based path resource allocation method applied to hybrid network

ActiveCN106341351AAchieving All-in-One RepresentationSolve the problem of huge differences in multi-layer resource representationData switching networksQuality of serviceGranularity

The invention relates to a QoS differentiation-based path resource allocation method applied to a hybrid network. According to the method, the levels of the quality of services which can be provided by different path resources of the network are differentiated, and a QoS hierarchical graph is established; different resource allocation strategies are adopted according to different QoS requirements of service requests; the physical resources and logical resources of the hybrid network are taken into consideration in a unified manner; and therefore, resources at each level are deeply integrated, the complexity of the method can be decreased; the QoS requirements of business can be dynamically adjusted, so that the success rate of resource allocation can be ensured; path resource allocation which satisfies the requirements of multi-type, multi-granularity and multi-QoS requirement business can be achieved, and different network path resource information can be shared according to different QoS requirements.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

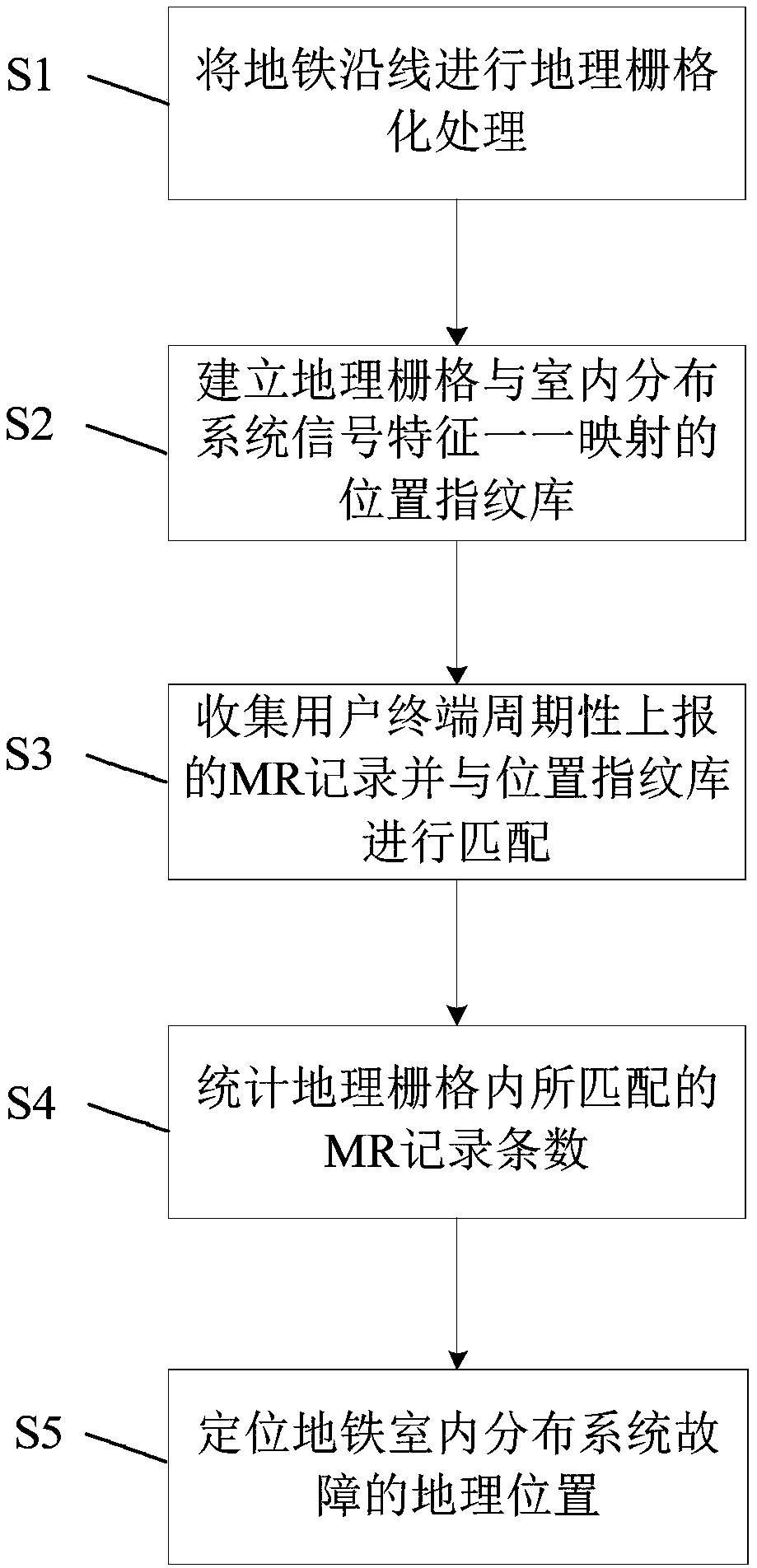

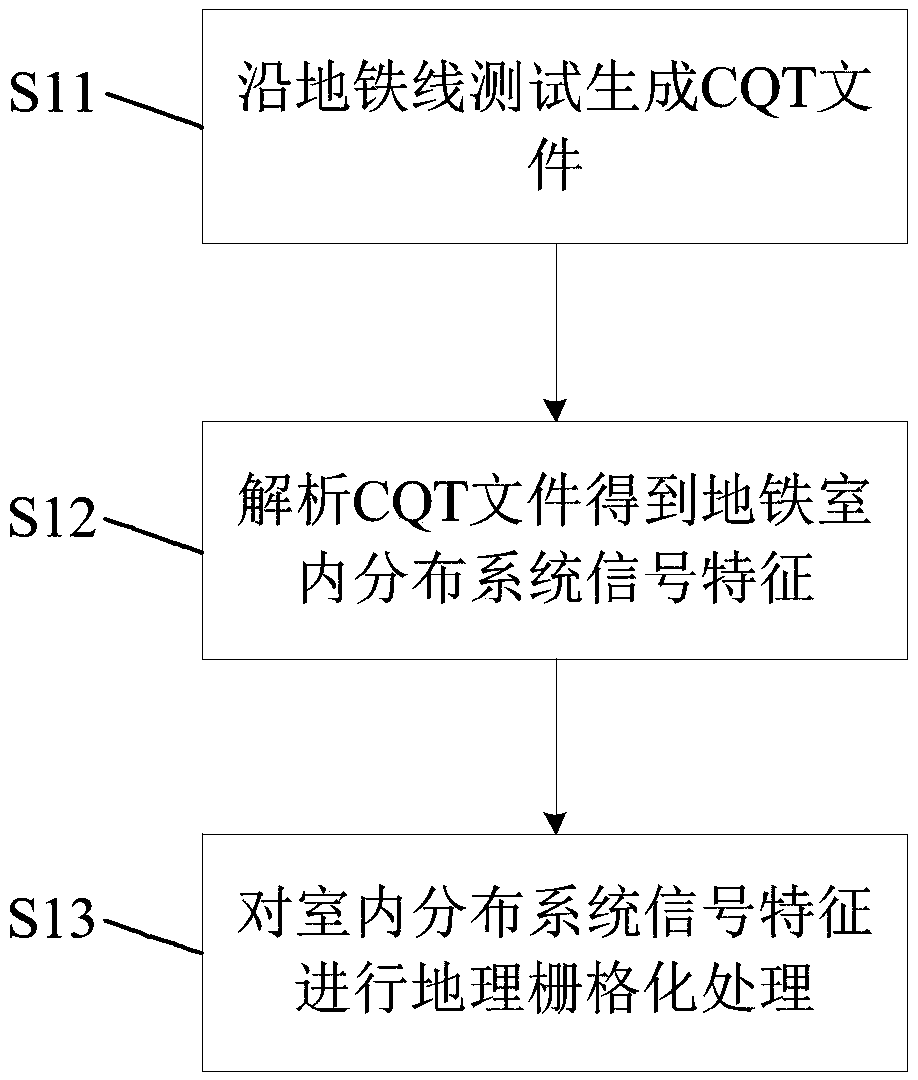

Method and system for locating failure of subway indoor distribution system

InactiveCN108718254APrecise positioningUniform average speedData switching networksWireless communicationGeographic siteGranularity

The invention discloses a method for locating a failure of a subway indoor distribution system. The method includes the steps that S1, a subway is subjected to geographical rasterization processing along a line; S2, a position fingerprint database of one-to-one mapping between geographical rasters and signal features of the indoor distribution system is established; S3, MR records reported periodically by a user terminal are collected and matched with the position fingerprint database; S4, the number of the matched MR records in the geographical rasters is counted; S5, according to the geographical rasters, the geographical position of the failure of the subway indoor distribution system is located. The invention further discloses a system for locating the failure of the subway indoor distribution system. Through measurement, a covering level feature fingerprint of each geographical raster in the subway is obtained to realize synchronous generation and mapping of the geographical rasters and the position fingerprint database, MR original files with the minimum time granularity are collected to realize relative and real-time localization for the failure of the subway indoor distribution system, and the failure of the subway indoor distribution system is accurately located.

Owner:中国联合网络通信有限公司湖北省分公司

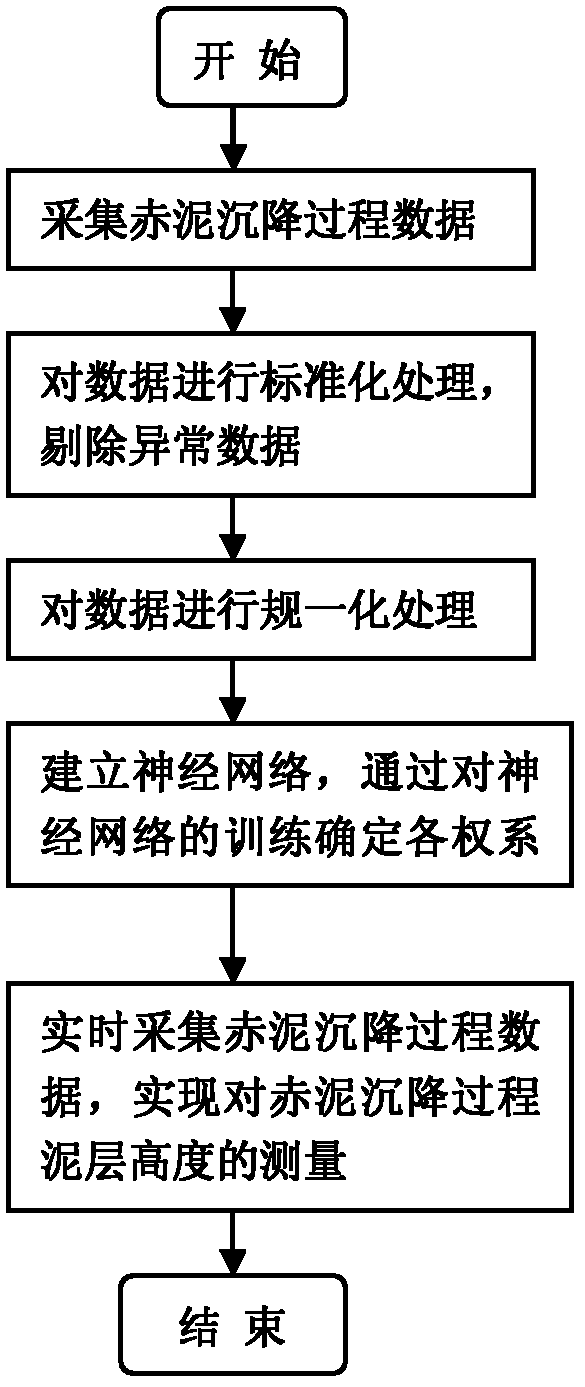

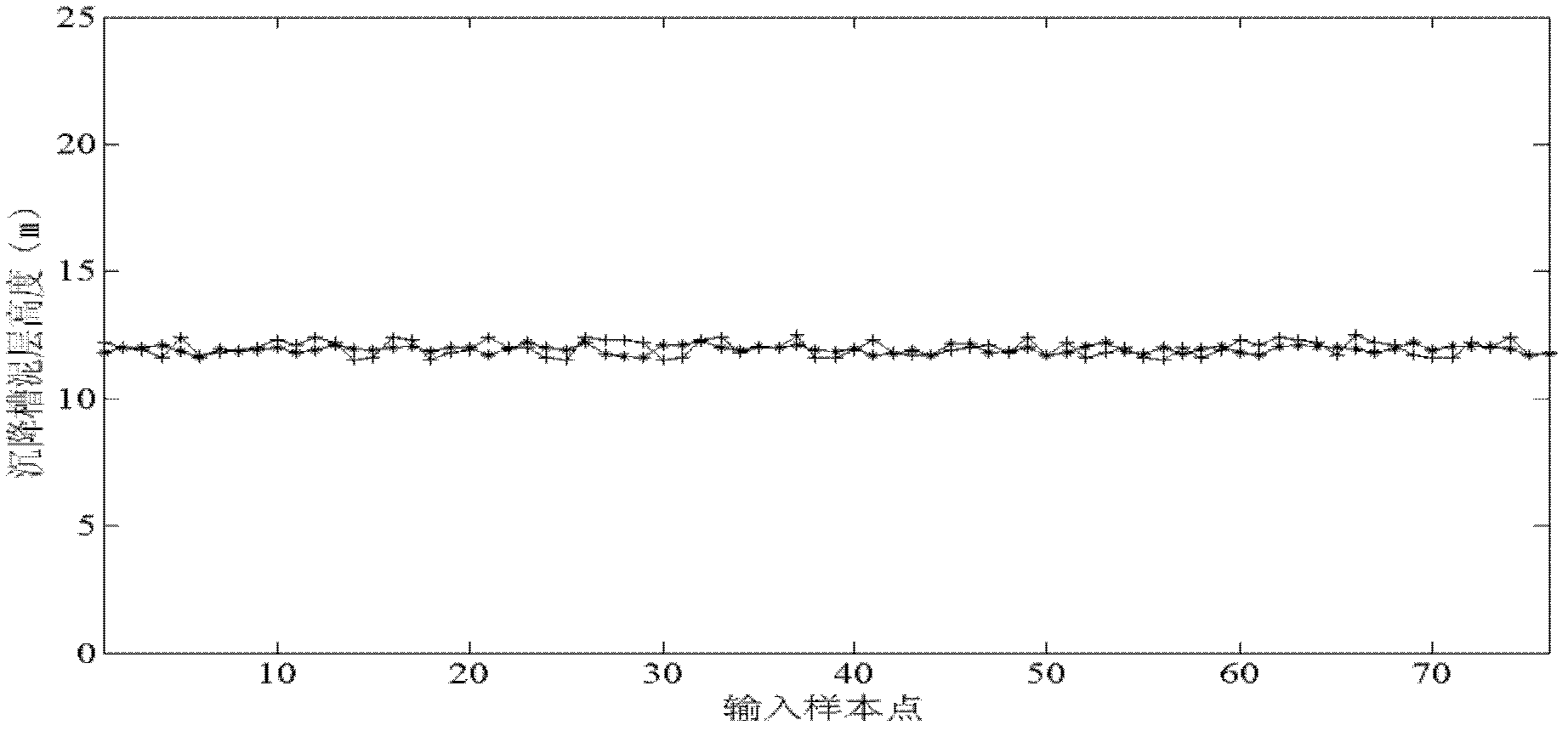

A kind of soft measurement method of mud layer height in red mud settlement process

InactiveCN102289718ARealize real-time online measurementRealize the mappingMeasurement devicesNeural learning methodsRed mudMineralogy

A soft measurement method for the height of the mud layer in the red mud settlement process belongs to the field of automatic measurement technology, comprising the following steps: establishing a mapping with the mud layer height (L) of the settlement tank by collecting the data of the red mud settlement process under different working conditions; Standardize the collected red mud settlement process data and eliminate abnormal data; standardize the data and use function transformation to map its value to the value interval of [0.1, 0.9]; substitute the data processed in step 3 into the neural network, The weight coefficients are determined through the training of the neural network; the data of the red mud settlement process is collected in real time, and the collected data is processed by steps 2-3, and brought into the trained neural network in step 4 to realize the settlement of the red mud The measurement of the height of the mud layer in the process; the real-time online measurement of the height of the mud layer is realized, which overcomes the shortcomings of the current method, which is large in maintenance, expensive, and not widely used.

Owner:NORTHEASTERN UNIV ENG & RES INST CO LTD