General packing method for FPGA (field programmable gate array) configurable logical block (CLB)

A programming logic and user-friendly technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as inability to handle functional configurations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

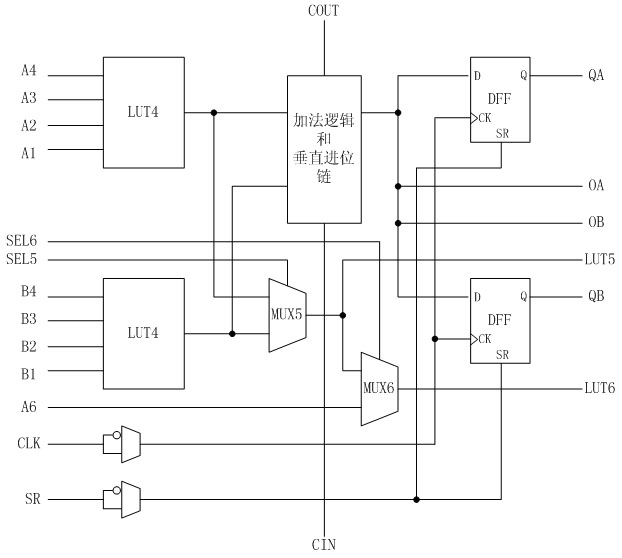

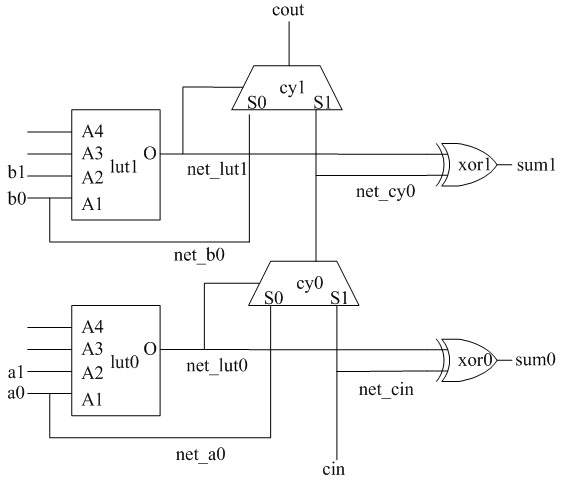

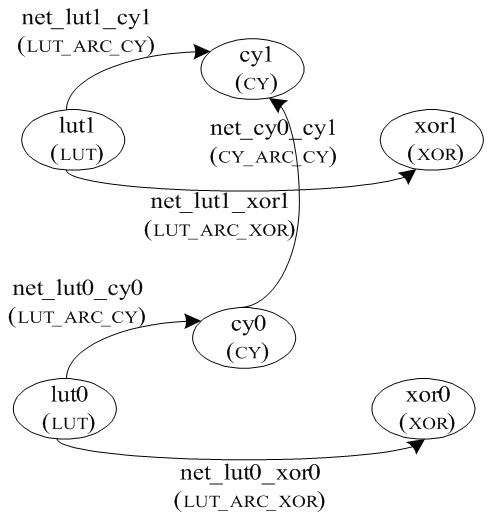

[0080] Assuming that the subscriber circuit adopts figure 2 A two-bit adder in the target graph G u that is image 3 . Figure 7 is the carry chain function circuit of the configurable logic block, and the modeled sample diagram G p Such as Figure 8 shown. The process of solving the two-bit adder bin packing problem with the method of constrained satisfiability problem is as follows:

[0081] (1) The sample graph G p Both vertices and directed edges in are mapped to variable sets X:

[0082] , x LUT Refers to the variable corresponding to the component LUT, x LUT_ARC_XOR Refers to the variable corresponding to the line network LUT_ARC_XOR, and other variables are named in a similar way.

[0083] (2) Put the target graph G u All vertices and directed edges in are mapped to the range D:

[0084] d lut0 Refers to the value corresponding to the element lut0, d net_lut0_xor0 Refers to the value corresponding to net_lut0_xor0, and other values are named in a s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More