Fat tree type network-on-chip mapping method based on differential evolution and predatory search strategy

A differential evolution, on-chip network technology, applied in the network field, can solve the problems of back-end wiring trouble, crosstalk between lines, difficult to apply IP core mapping, etc., to achieve the effect of optimal energy consumption results and shorten the running time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

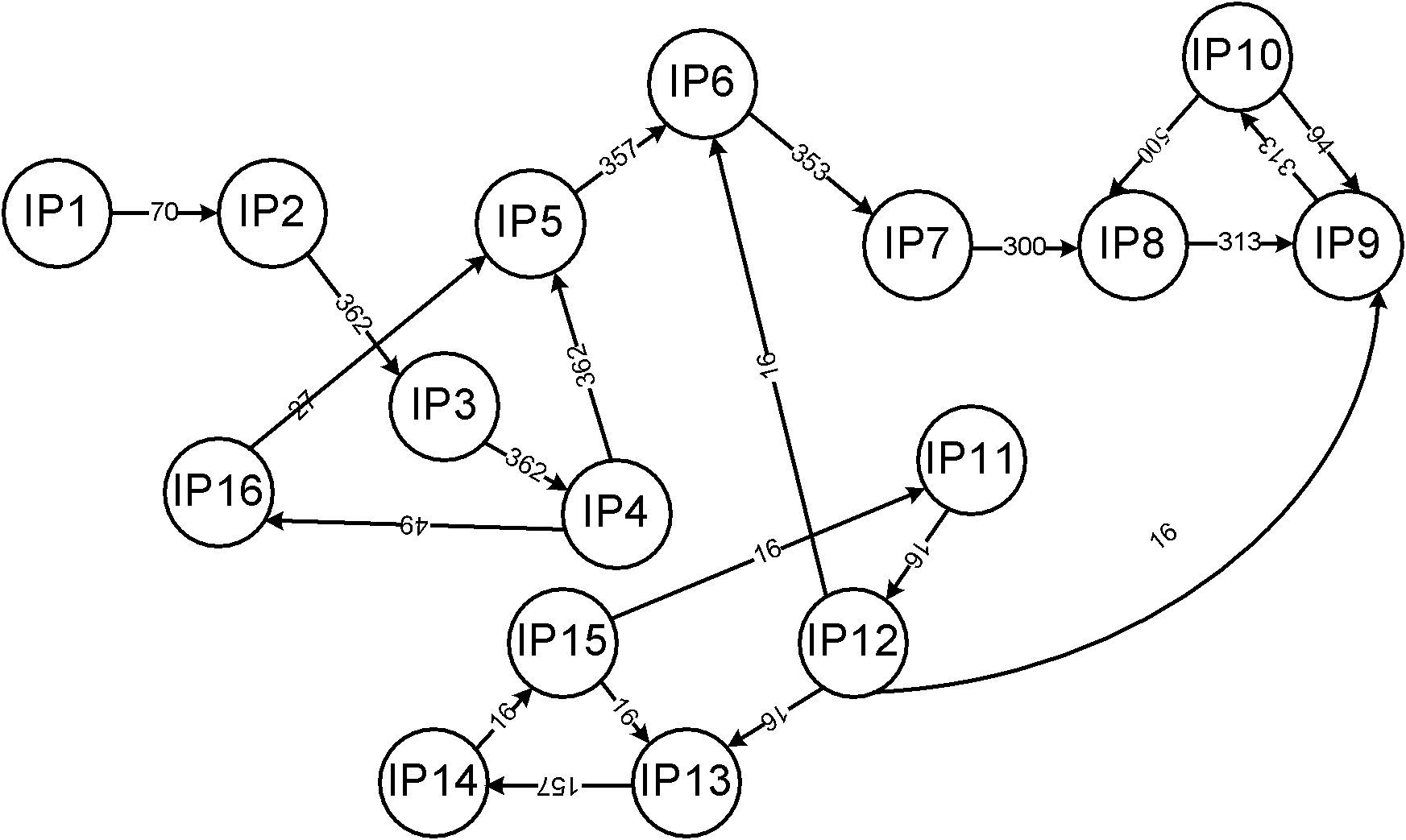

[0026] the following to figure 1 The illustrated 16-core video object plane decoding VOPD communication core map is used as an example to describe the present invention in detail.

[0027] For convenience of description, the present invention numbers each IP core in the communication core diagram of video object plane decoding VOPD: IP1, IP2, ..., IP16, and the order of numbering does not affect the mapping position of the IP core. The communication core diagram of video object plane decoding VOPD and the number of each IP core are as follows figure 1 shown. figure 1 In , each vertex represents an IP core, and the number on the vertex represents the number of the IP core. If there is an edge between two vertices, it means that there is a communication relationship between the two IP cores. The weight of the edge represents It controls the communication traffic between these two IP cores.

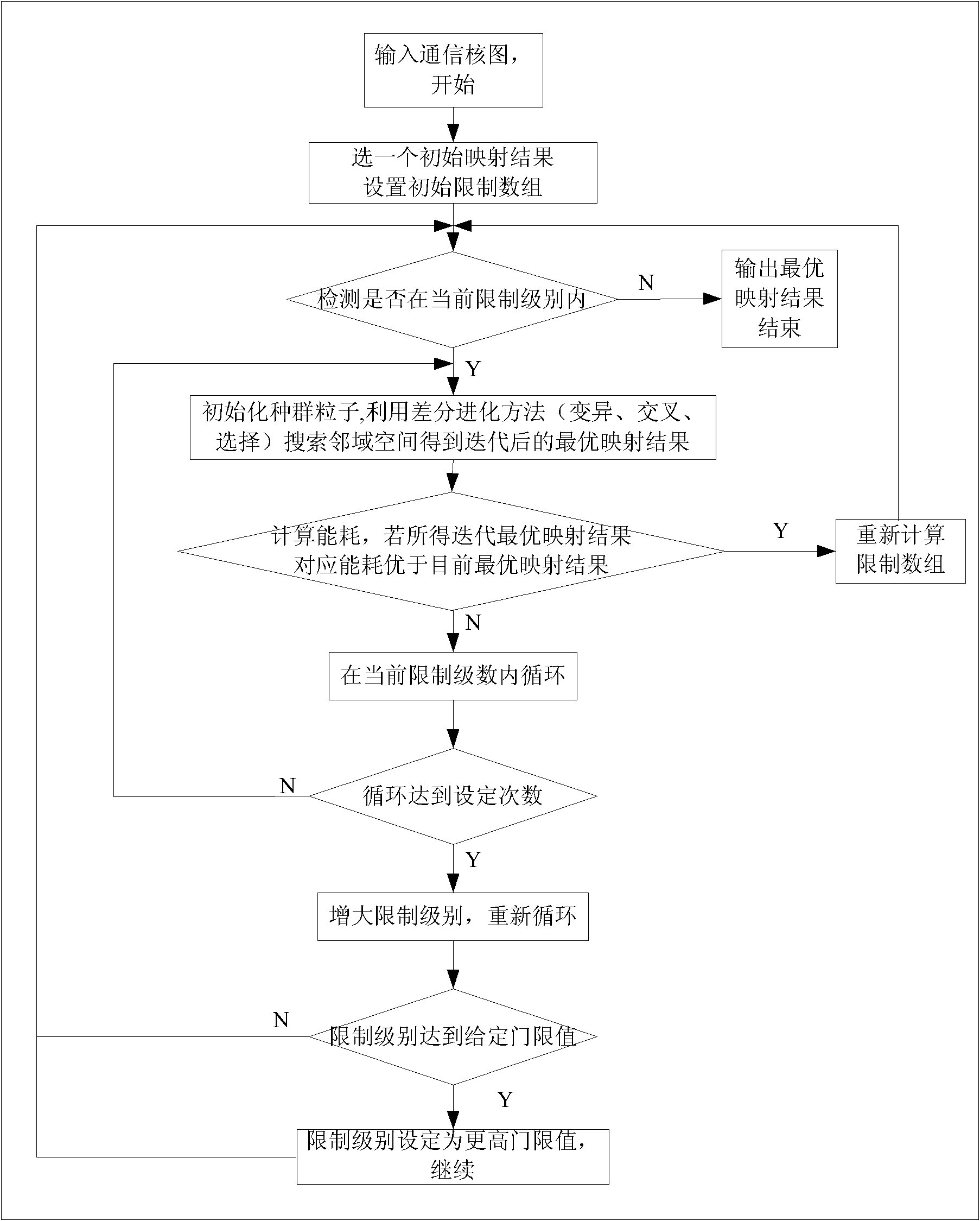

[0028] refer to figure 2 , the specific implementation steps of the present inventi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More