Method and system for accelerating concurrent working of ARM processors

An ARM processor and bus technology, applied in the field of big data search, can solve the problems of acceleration and low work efficiency, and achieve the effects of high performance, improved work efficiency, and efficient backup

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

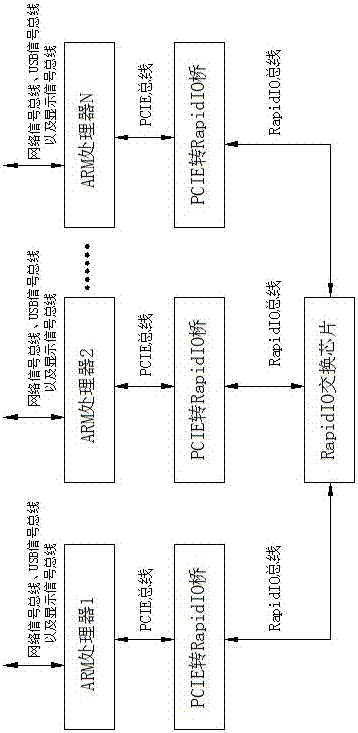

[0023] as attached figure 1 Shown, the ARM processor parallel working method based on RapidIO of the present invention converts the PCIE bus of each ARM processor into a RapidIO bus, and carries out data communication through the RapidIO bus between the ARM processors.

[0024] Specifically include the following steps:

[0025] (1) Each ARM processor is connected to a PCIE-to-RapidIO bridge, and the PCIE bus of the ARM processor is converted to a RapidIO bus through the PCIE-to-RapidIO bridge;

[0026] (2) A RapidIO switch chip is set between the PCIE-to-RapidIO bridges, each PCIE-to-RapidIO bridge is connected to the RapidIO switch chip, through the cooperation of the PCIE-to-RapidIO bridge and the RapidIO switch chip, the data between the ARM processors is transmitted through the RapidIO bus communication.

[0027] Among them, the PCIE-to-RapidIO bridge is used to convert the PCIE bus of the ARM processor into a RapidIO bus. Commonly used PCIE-to-RapidIO bridges are TSI620...

Embodiment 2

[0038] The system for accelerating the parallel work of ARM processors of the present invention includes a RapidIO switching chip, a plurality of ARM processors, and a plurality of PCIE-to-RapidIO bridges, each ARM processor corresponds to a PCIE-to-RapidIO bridge, and each ARM processor passes through The PCIE bus is connected to the corresponding PCIE-to-RapidIO bridge, and each PCIE-to-RapidIO bridge is connected to the RapidIO switch chip through the RapidIO bus.

[0039]Among them, the PCIE-to-RapidIO bridge is used to convert the PCIE bus of the corresponding ARM processor into a RapidIO bus, each PCIE-to-RapidIO bridge is connected to a RapidIO switch chip, and the RapidIO switch chip is used to realize the interconnection of multiple PCIE-to-RapidIO bridges , so that with the cooperation of the PCIE-to-RapidIO bridge and the RapidIO switch chip, multiple processors can perform data communication through the RapidIO bus. Commonly used PCIE-to-RapidIO bridges such as TSI...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More