Power-on reset containing circuit applied to IO interface of digital chip

A digital chip, electrical reset technology, applied in the direction of adjusting electrical variables, control/regulating systems, instruments, etc., can solve the problems of high cost, many latch chip pins, complex peripheral circuits, etc., to achieve low cost, simple circuit, The effect of flexible time adjustment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

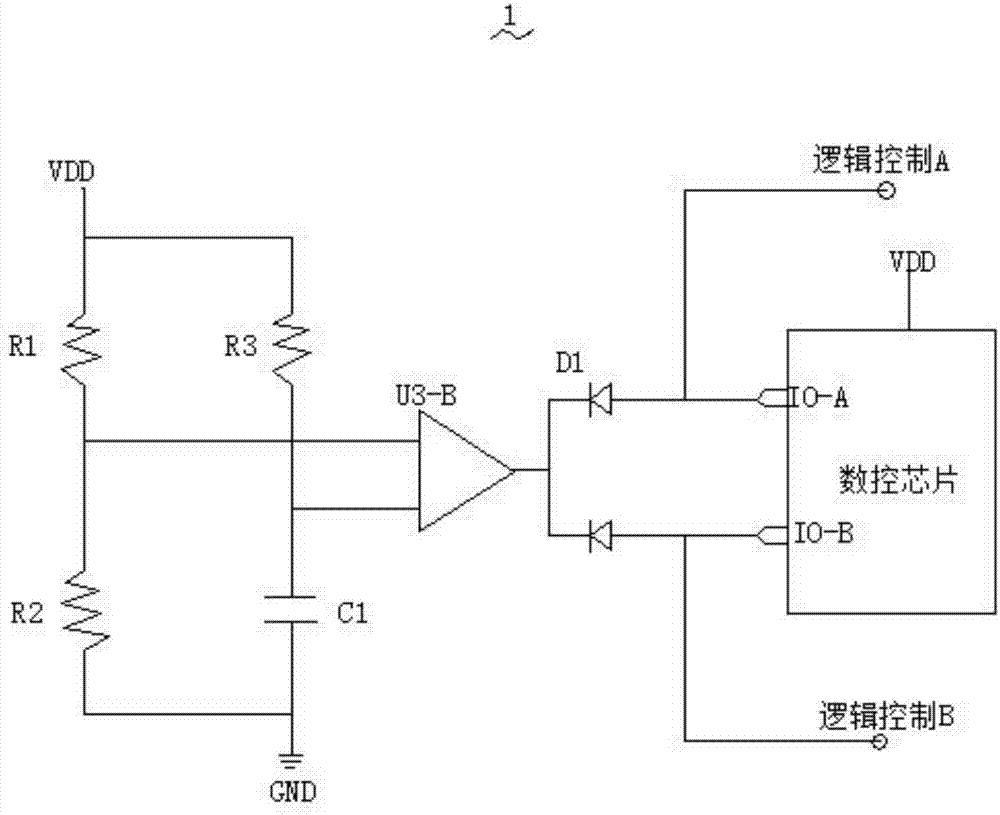

[0013] see figure 1 A power-on reset pinning circuit 1 applied to the IO port of a digital chip of the present invention includes an R-R voltage divider circuit, an R-C charging circuit and a comparison circuit; the R-R voltage divider circuit includes a first resistor R1 and a second resistor R2 connected in series ; The R-C charging circuit includes a third resistor R3 and a first capacitor C1 connected in series; the comparison circuit includes a comparator and a diode circuit connected to the output of the comparator, and the diode circuit is connected to the corresponding IO port of the digita...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More