DSP instruction simulation method based on register access conflict detection

A technology of access conflict and simulation method, applied in the direction of concurrent instruction execution, machine execution device, etc., to achieve the effect of ensuring correctness, taking into account efficiency and correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

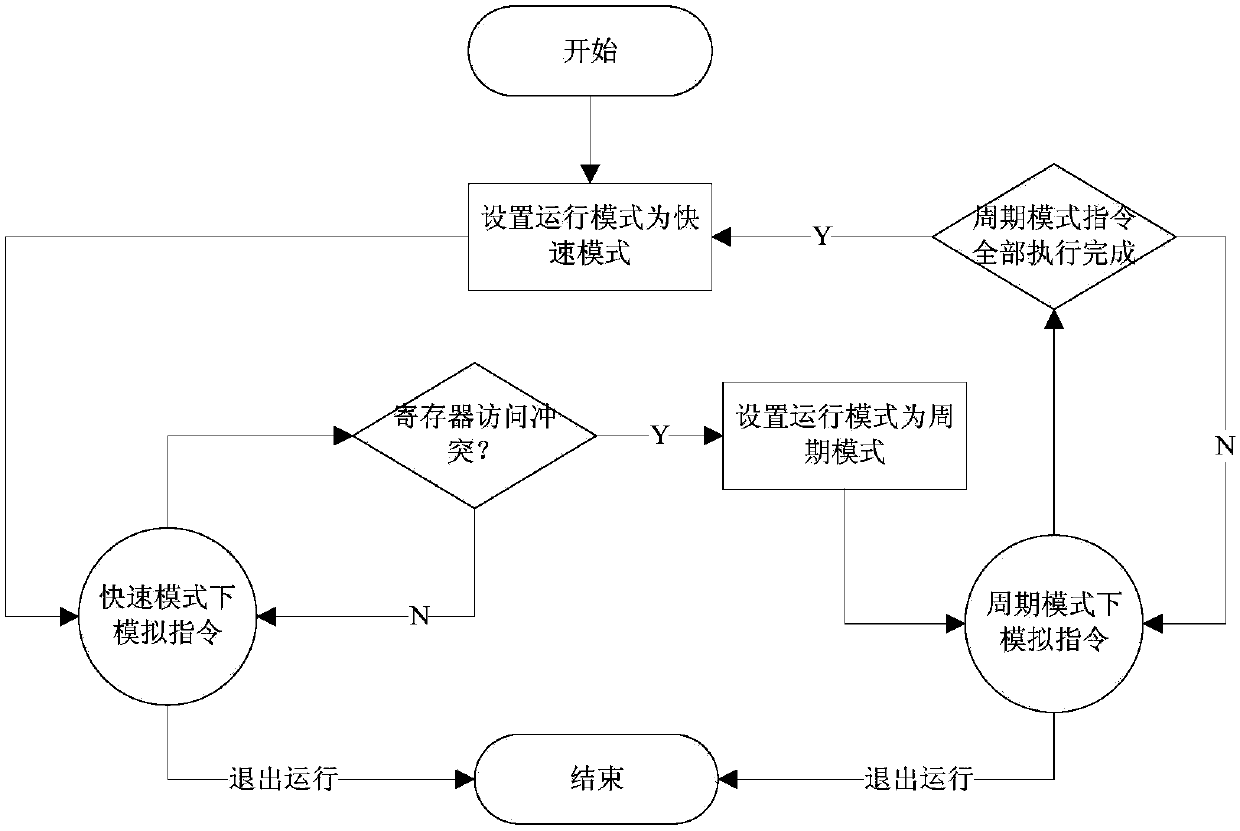

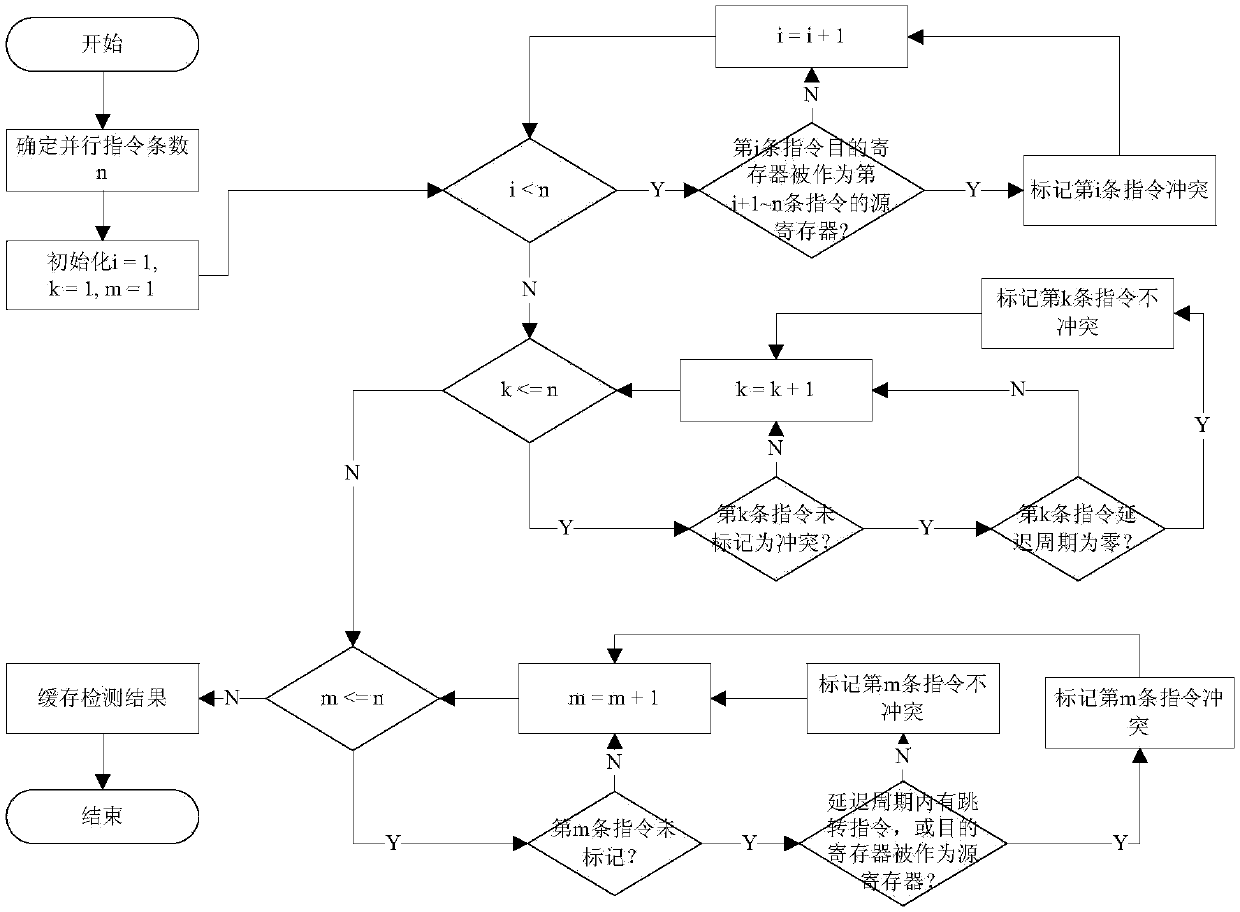

Method used

Image

Examples

Embodiment

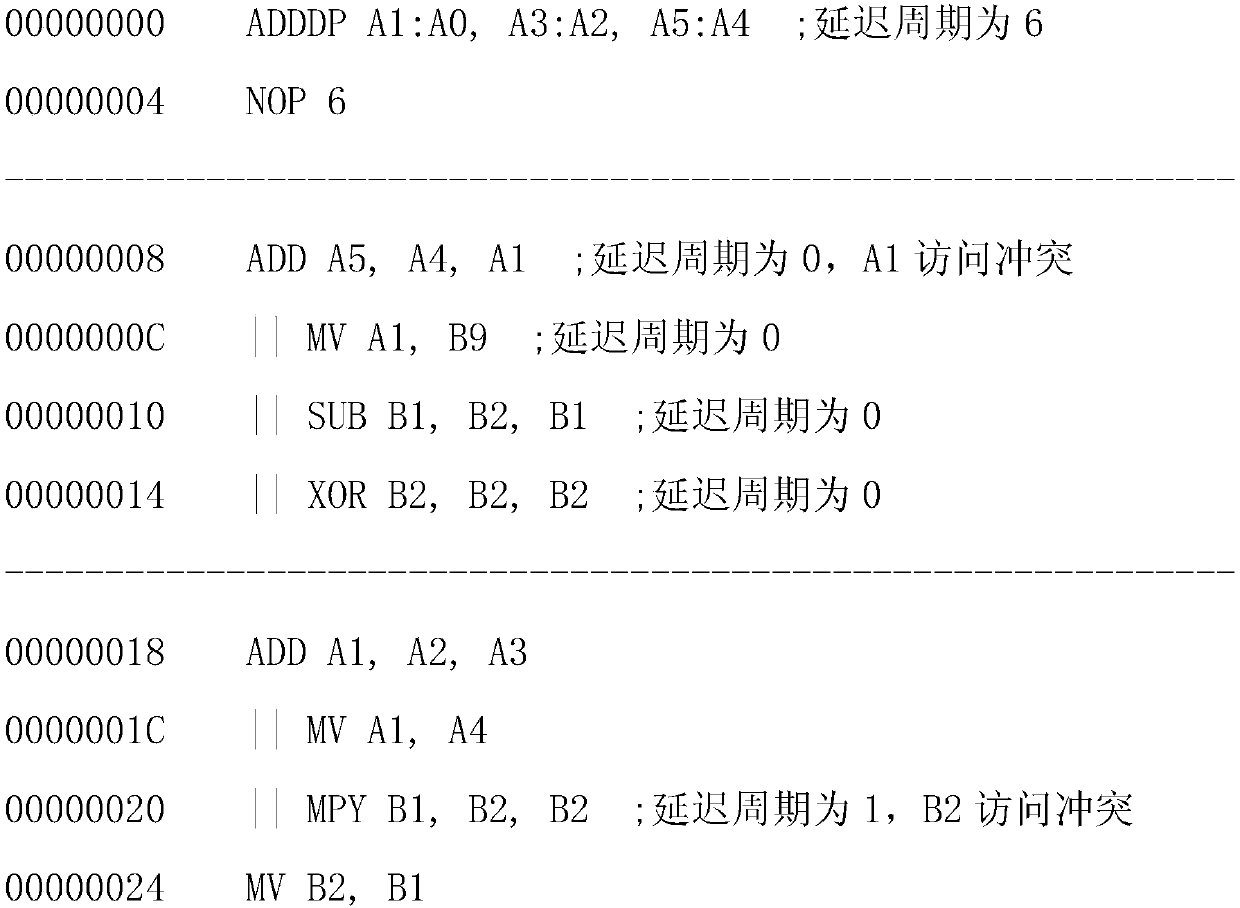

[0054] Below in conjunction with a section of TMS320C6000 DSP instruction code, illustrate the implementation steps of the present invention:

[0055]

[0056]

[0057] In this code, when the instruction is preceded by "||", it means that the address instruction is executed in parallel with the previous instruction. The pipeline characteristics of the ADDDP instruction are shown in the following table:

[0058]

[0059] Among them, E1~E7 are the seven stages of pipeline execution, and each stage occupies one cycle. The E1 stage completes the reading of the low bits of the instruction source operands src1 and src2, and the E2 stage completes the reading of the source operands src1 and src2 high bits. E3~ The E5 stage completes the operation of the ADDDP instruction, the E6 stage writes the low-order dst_l of the operation result into the destination register, and the E7 stage writes the high-order dst_h of the operation result into the destination register.

[0060] In ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap