Chip architecture reconstruction method and device

A chip and reconfiguration technology, which is applied in the field of chip architecture reconfiguration methods and devices, can solve problems such as the inability to reuse ASICs, and achieve the effects of prolonging product life cycles, shortening development cycles, and achieving convenience and flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

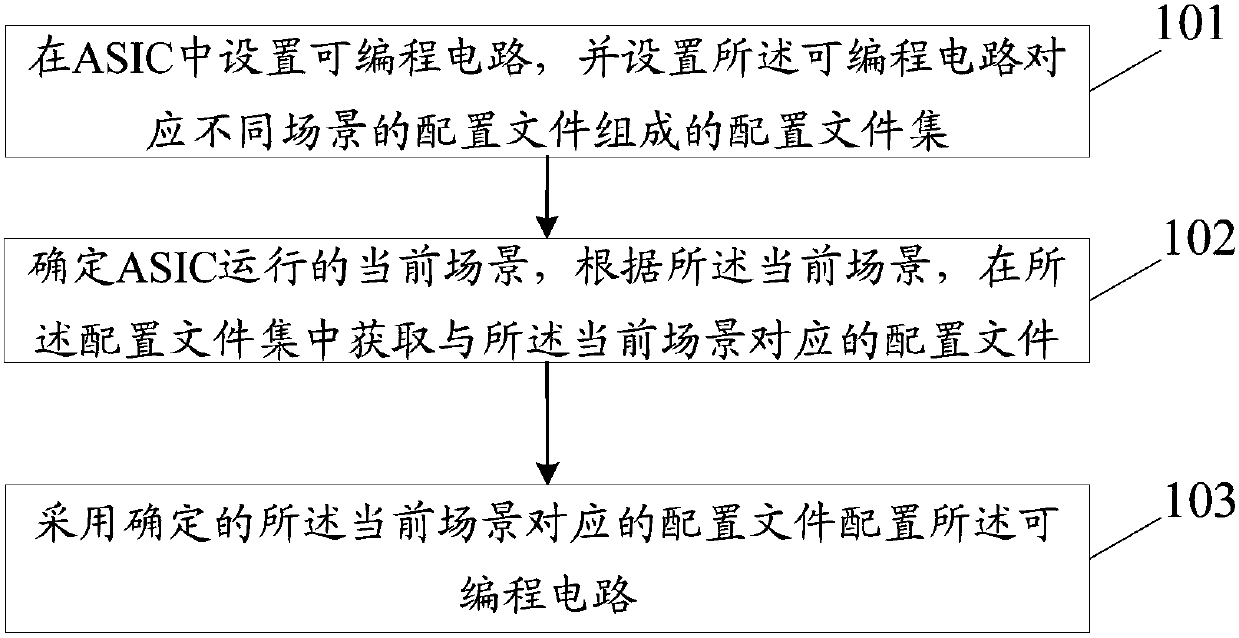

[0037] In the embodiment of the present invention, a programmable circuit is set in the ASIC, and a configuration file set composed of configuration files corresponding to different scenarios of the programmable circuit is set; the current scenario of ASIC operation is determined, and according to the current scenario, in the configuration The configuration file corresponding to the current scene is acquired in a centralized file; and the programmable circuit is configured using the determined configuration file corresponding to the current scene.

[0038] The present invention will be described in further detail below in conjunction with the examples.

[0039] The chip architecture reconfiguration method provided by the embodiment of the present invention, such as figure 1 As shown, the method includes:

[0040] Step 101: setting a programmable circuit in the ASIC, and setting a configuration file set composed of configuration files corresponding to different scenarios of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com