Arithmetic addition mask to Boolean xor mask protection circuit

A technology of turning Boolean difference and arithmetic addition, which is applied to the countermeasures of attacking encryption mechanisms, electrical components, digital transmission systems, etc., can solve the problems of high complexity of Boolean masks, large occupied area, small occupied area, etc., to improve execution Efficiency, reduced circuit area and cost, and reduced complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

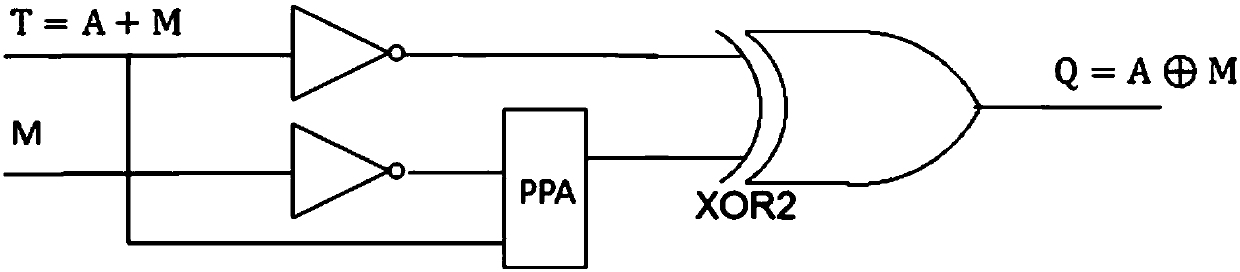

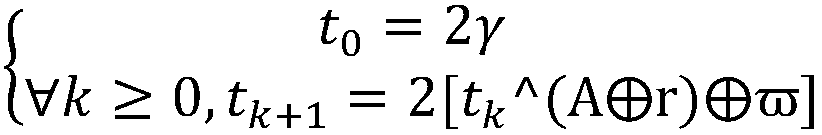

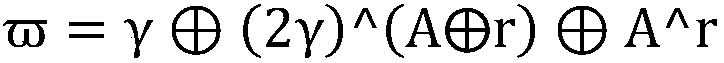

[0015] From the perspective of digital circuit design, the present invention proposes a circuit for converting arithmetic addition into a Boolean mask. A conversion circuit structure is built by using a simple gate circuit. The specific circuit structure is as follows: figure 1 shown. The specific idea is as follows: Assume that A is the sensitive data that needs to be masked, and M is the mask. When implementing a boolean mask, let When implementing an additive mask, let Q=A+M mod 2 n -1,C out For carry, there is Q=(A+M)mod 2 n -1

[0016] =(C out *2 n )+(A+M)mod 2 n )) mod 2 n -1

[0017] =(C out +(A+M)mod 2 n )) mod 2 n -1

[0018] =(A+M)+C out mod 2 n

[0019] A, M, T, Q are all n-bit data, expressed as

[0020] A=(a n-1 a n-2 ...a 1 a 0 )

[0021] M=(m n-1 m n-2 ... m 1 m 0 )

[0022] T=(t n-1 t n-2 ...t 1 t 0 )

[0023] Q=(q n-1 q n-2 ....q 1 q 0 )

[0024] where a i ,m i ,t i ,q i ∈GF(2), i=0,1,...n-1, C out for carry

[0025...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More