Semiconductor device and manufacturing method

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as complex processes, and achieve the effect of simplifying the process flow and reducing production costs

Active Publication Date: 2018-04-17

SEMICON MFG INT (SHANGHAI) CORP +1

View PDF5 Cites 1 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

In the existing process, in order to form the metal silicide barrier layer, the insulating layer must

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Login to View More

Login to View More PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Login to View More

Abstract

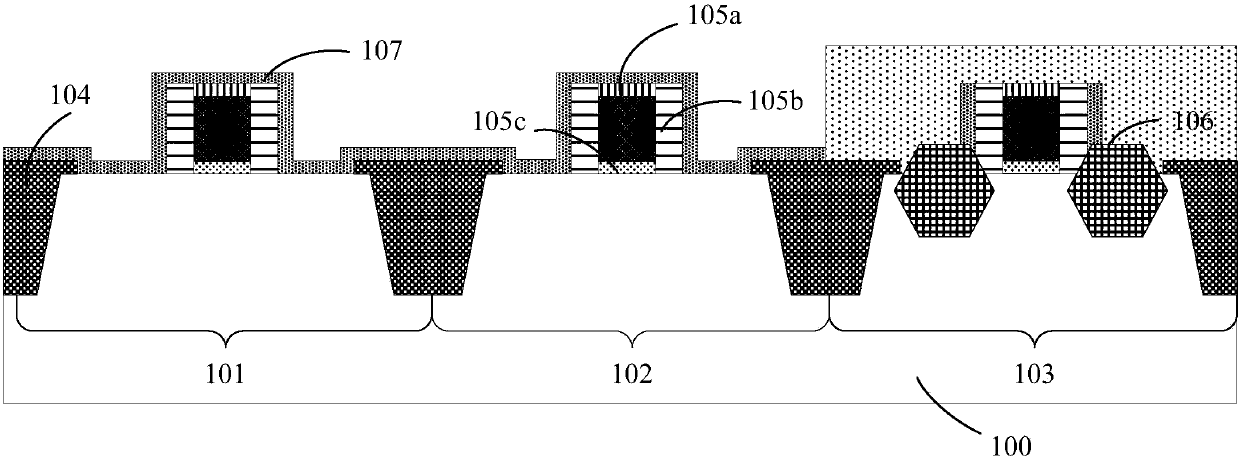

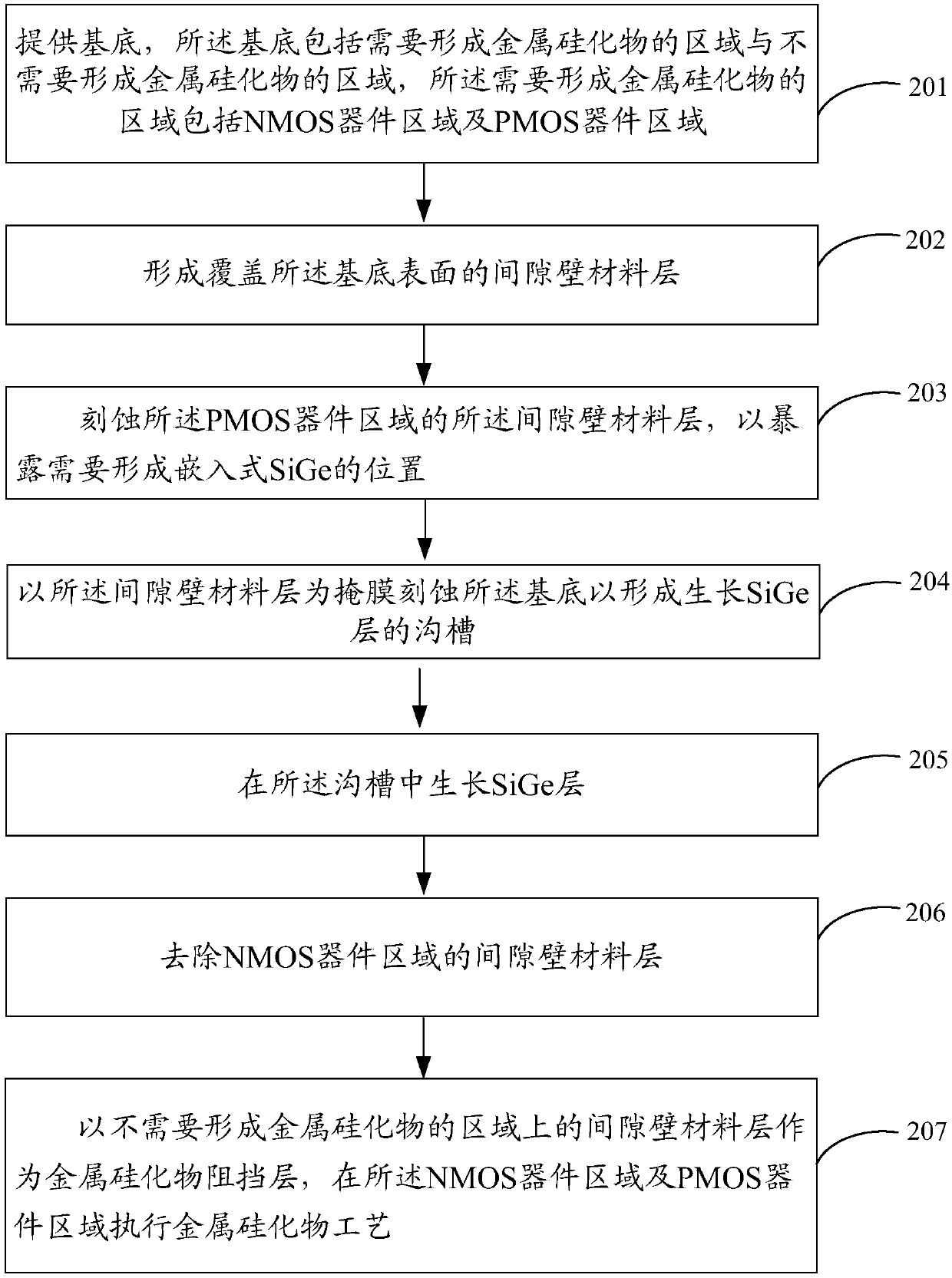

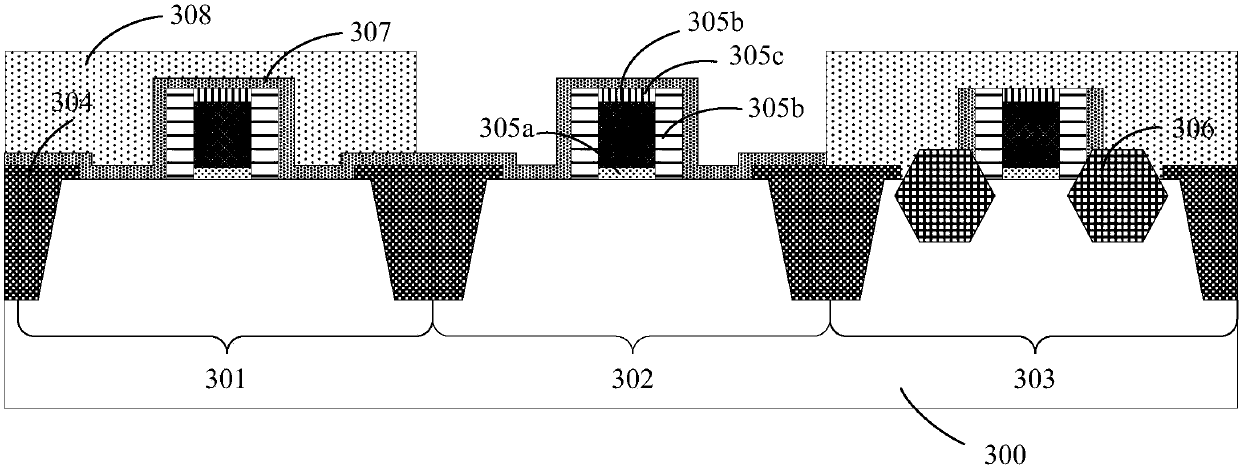

The invention provides a semiconductor device and a manufacturing method therefor. The method comprises the steps: providing a substrate, wherein the substrate comprises a region where metal silicideneeds to be formed, and a region where no metal silicide needs to be formed, and the where metal silicide needs to be formed comprises an NMOS device region and a PMOS device region; forming a gap wall material layer covering the surface of the substrate; etching the gap wall material layer of the PMOS device region, so as to expose a position where embedded-type SiGe needs to be formed; taking the gap wall material layer as a mask to etch the substrate, so as to form a trench where a SiGe layer grows; growing the SiGe layer in the trench; removing the gap wall material layer of the NMOS device region; taking the gap wall material layer in the region where no metal silicide needs to be formed as a metal silicide blocking layer, and executing the metal silicide technology in the NMOS deviceregion and the PMOS device region. According to the invention, the manufacturing method can simplify the technological flow, and reduce the production cost.

Description

technical field [0001] The invention relates to a semiconductor manufacturing process, in particular to a semiconductor device and a manufacturing method thereof. Background technique [0002] Embedded silicon germanium source-drain technology (embedded SiGe, eSiGe) is a strained silicon technology used to improve the performance of PMOS. It increases the hole mobility of PMOS by generating uniaxial compressive stress in the channel, thereby improving the current driving capability of the transistor, and is the core technology in the high-performance process of the 45nm and below technology generation. The principle is to etch a trench on Si as the source-drain region, and selectively epitaxially grow a SiGe layer in the trench, using the mismatch between the SiGe lattice constant and Si, so that the Si along the channel direction is compressed to generate pressure. stress, thereby increasing the hole mobility in the channel Si. Generally, after forming the SiGe layer and ...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More IPC IPC(8): H01L29/78H01L21/02H01L29/66

CPCH01L21/02532H01L29/66477H01L29/7848

Inventor 赵鹏施森华

Owner SEMICON MFG INT (SHANGHAI) CORP

Who we serve

- R&D Engineer

- R&D Manager

- IP Professional

Why Patsnap Eureka

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com