Automatic cell placement and optimization method for semi-custom back-end design of integrated circuits

A technology of integrated circuits and optimization methods, applied in CAD circuit design, computer-aided design, calculation, etc., can solve problems such as too long iteration time and poor design quality, so as to avoid invalid work, reduce the number of design iterations, and improve design quality effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The invention discloses an automatic unit placement and optimization method for integrated circuit semi-customized back-end design. The specific implementation of the invention will be further described below in combination with preferred embodiments.

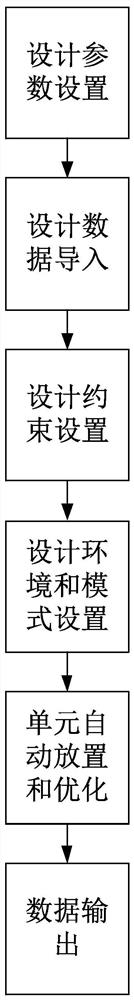

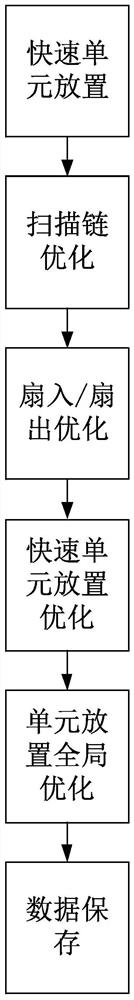

[0029] see attached figure 1 , figure 1 The specific flow of the automatic unit placement and optimization method for the integrated circuit semi-custom back-end design is shown. Preferably, the automatic unit placement and optimization method for semi-custom back-end design of integrated circuits includes the following steps:

[0030] Step S1: the back-end design tool defines the design parameters of the design environment model;

[0031] Step S2: The back-end design tool imports design constraint information according to unit placement requirements;

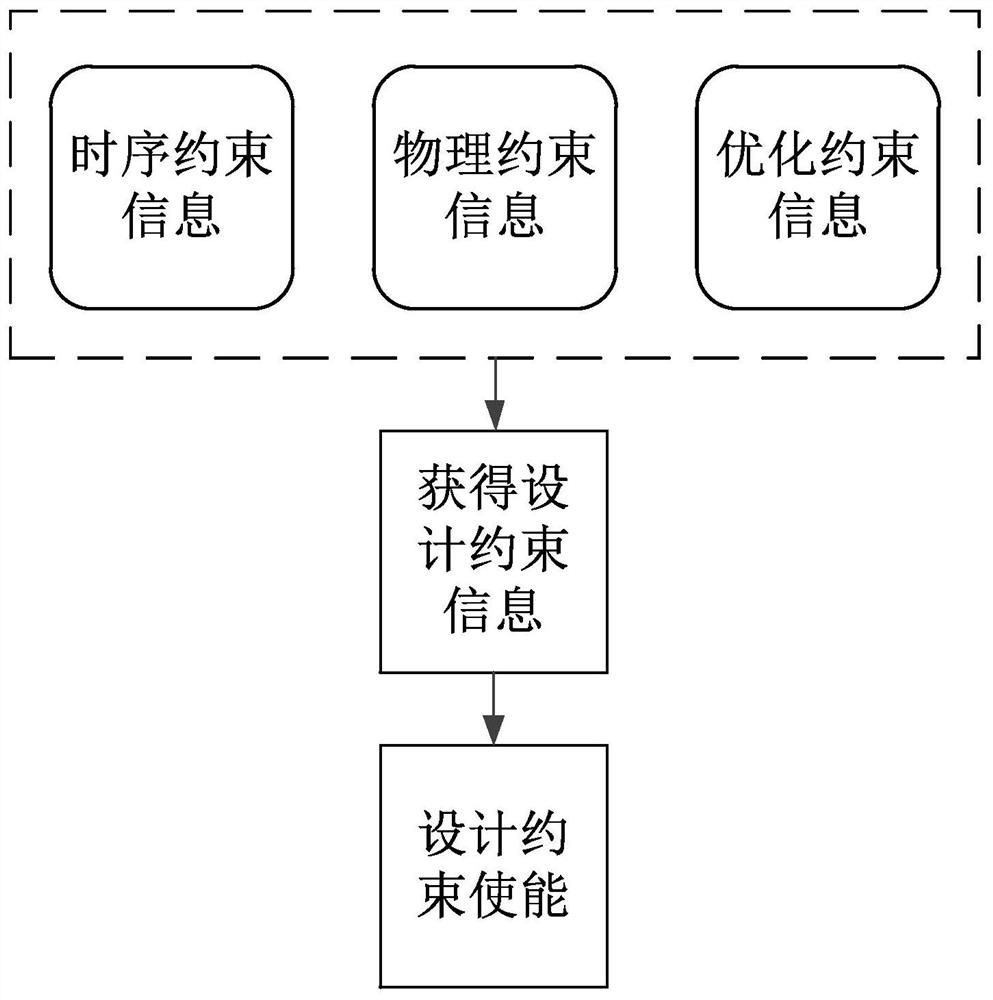

[0032] Step S3: The design constraint information module of the back-end design tool converts the above-mentioned design constraint information into the design constra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More