Pixel circuit and driving method thereof as well as display device

A technology of pixel circuits and driving transistors, which can be used in static indicators, instruments, etc., to solve problems such as afterimages of display panels

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

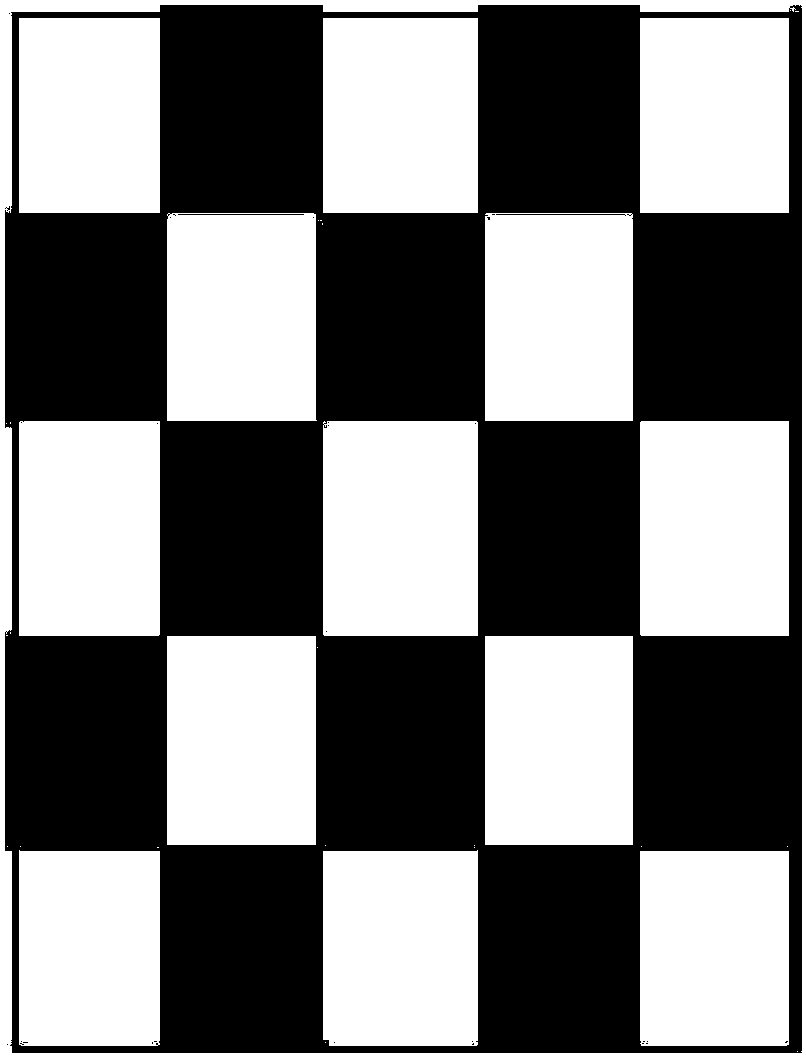

[0091] In the pixel circuit provided by the embodiment of the present invention, such as image 3 As shown, the gate of the first switch transistor M1 is connected to the reset control terminal Comp, and the gate of the fifth switch transistor M5 is connected to the second light emission control terminal EM2; the drive transistor DT, the first switch transistor M1, the second switch transistor M2 and the third switch transistor M3 are P-type transistors, and the fourth switch transistor M4 and the fifth switch transistor M5 are N-type transistors. The corresponding input timing is as Figure 12 shown.

[0092] In the T1 phase (reset phase), Gate2=1, Comp=0, EM1=0, EM2=1. The first switch transistor M1 , the third switch transistor M3 and the fifth switch transistor M5 are turned on, and the second switch transistor M2 and the fourth switch transistor M4 are turned off. The voltage of the first node N1 is Vint, and the voltage of the second node N2 is Vint-Vth.

[0093] In ...

example 2

[0096] In the pixel circuit provided by the embodiment of the present invention, such as Figure 4 As shown, the gate of the first switch transistor M1 is connected to the reset control terminal Comp, and the gate of the fifth switch transistor M5 is connected to the second light emission control terminal EM2; the drive transistor DT, the second switch transistor M2, the fourth switch transistor M4 and the fifth switch transistor M5 are P-type transistors, and the first switch transistor M1 and the third switch transistor M3 are N-type transistors. The corresponding input timing is as Figure 13 shown.

[0097] In the T1 phase (reset phase), Gate2=1, Comp=1, EM1=1, EM2=0. The first switch transistor M1 , the third switch transistor M3 and the fifth switch transistor M5 are turned on, and the second switch transistor M2 and the fourth switch transistor M4 are turned off. The voltage of the first node N1 is Vint, and the voltage of the second node N2 is Vint-Vth.

[0098] In...

example 3

[0101] In the pixel circuit provided by the embodiment of the present invention, such as Figure 5 As shown, the gate of the first switching transistor M1 is connected to the reset control terminal Comp, and the gate of the fifth switching transistor M5 is connected to the second scanning signal terminal Gate2;

[0102] The driving transistor DT, the second switching transistor M2 and the fourth switching transistor M4 are P-type transistors, and the first switching transistor M1 , the third switching transistor M3 and the fifth switching transistor M5 are N-type transistors. The corresponding input timing is as Figure 14 shown.

[0103] In the T1 phase (reset phase), Gate2=1, Comp=1, and EM1=1. The first switch transistor M1 , the third switch transistor M3 and the fifth switch transistor M5 are turned on, and the second switch transistor M2 and the fourth switch transistor M4 are turned off. The voltage of the first node N1 is Vint, and the voltage of the second node N2 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More