Configuring coarse-grained reconfigurable arrays (CGRAs) for dataflow instruction block execution in block-based dataflow instruction set architectures (ISAs)

A technology of instruction set architecture and data flow, applied in the direction of concurrent instruction execution, data flow computer, architecture with a single central processing unit, etc., can solve the problem that the program cannot be executed by the computer processor.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Referring now to the figures, several exemplary aspects of the invention are described. The word "exemplary" is used herein to mean "serving as an example, instance, or illustration." Any aspect described herein as "exemplary" is not necessarily to be construed as preferred or advantageous over other aspects.

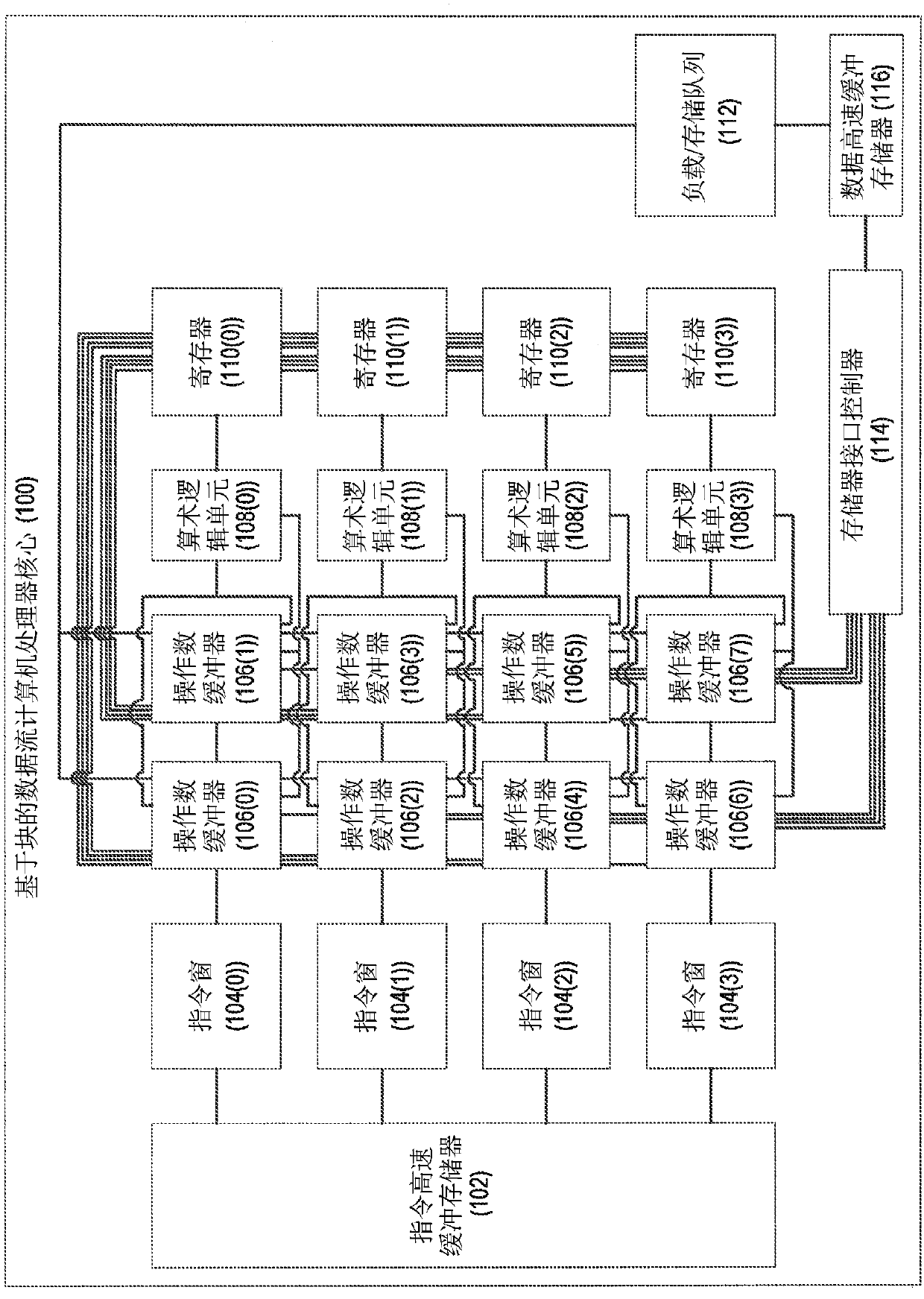

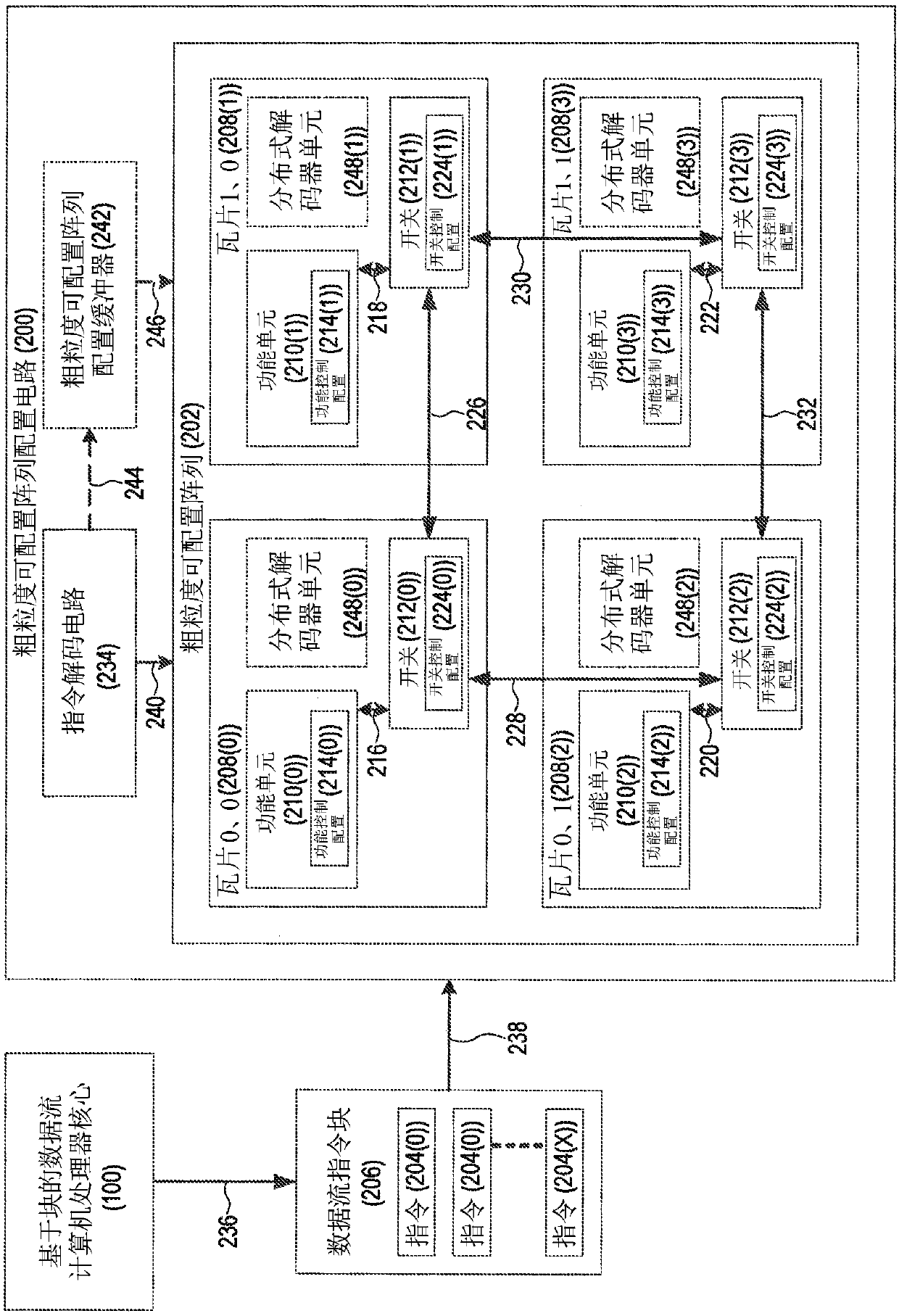

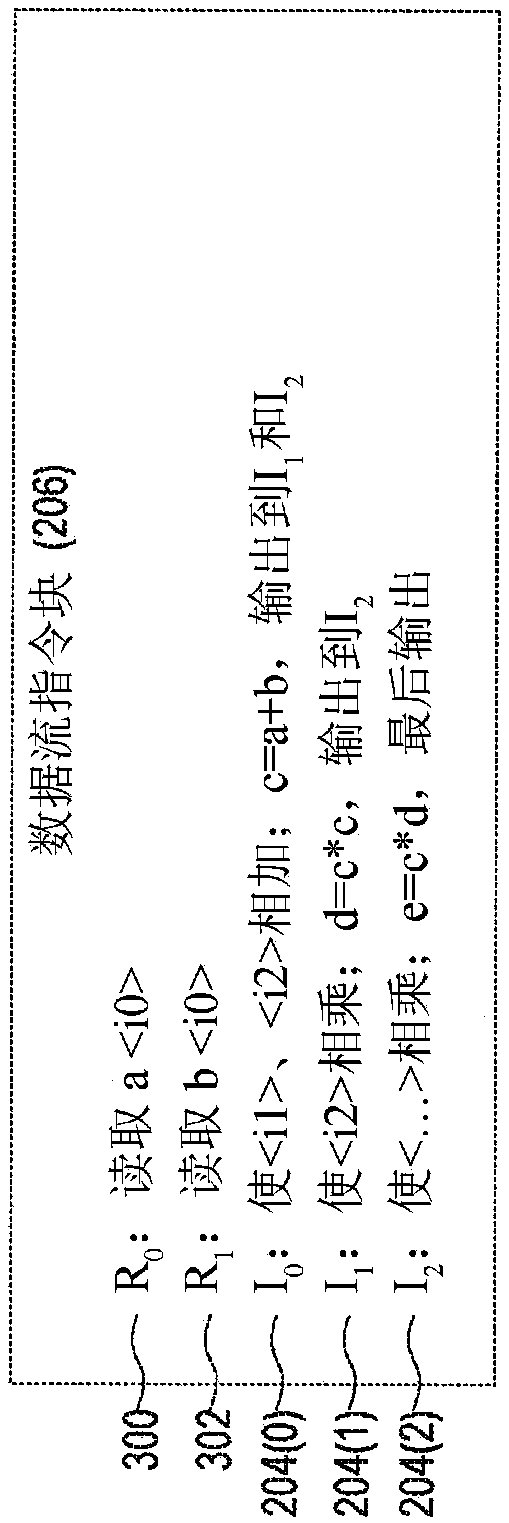

[0018] Aspects disclosed in the detailed description include configuring a coarse-grained configurable array (CGRA) in a block-based dataflow instruction set architecture (ISA) for dataflow instruction block execution. In one aspect, the CGRA configuration circuit is provided in a block-based dataflow ISA. The CGRA configuration circuit is configured to dynamically configure the CGRA to provide the functionality of the data flow instruction block. A CGRA includes an array of tiles, each of which provides functional units and switches. The instruction decoding circuitry of the CGRA configuration circuit maps each data flow instruction within a data flow instruc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More