Pipeline multiplexer loop architecture for decision feedback equalizer circuits

A decision feedback equalization, multiplexer technology, applied in instruments, electrical components, static memory, etc., can solve the problems of limited speed and large final size of parallel architectures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention generally relates to circuits, methods and apparatus for decision feedback equalization. In some examples, embodiments of the invention may result in smaller, faster and / or simpler multiplexer ring architectures. In some examples, application of the multiplexer ring architecture described herein may allow for greater parallelization, higher clock speeds, and / or higher throughput in parallel processing decision feedback circuits.

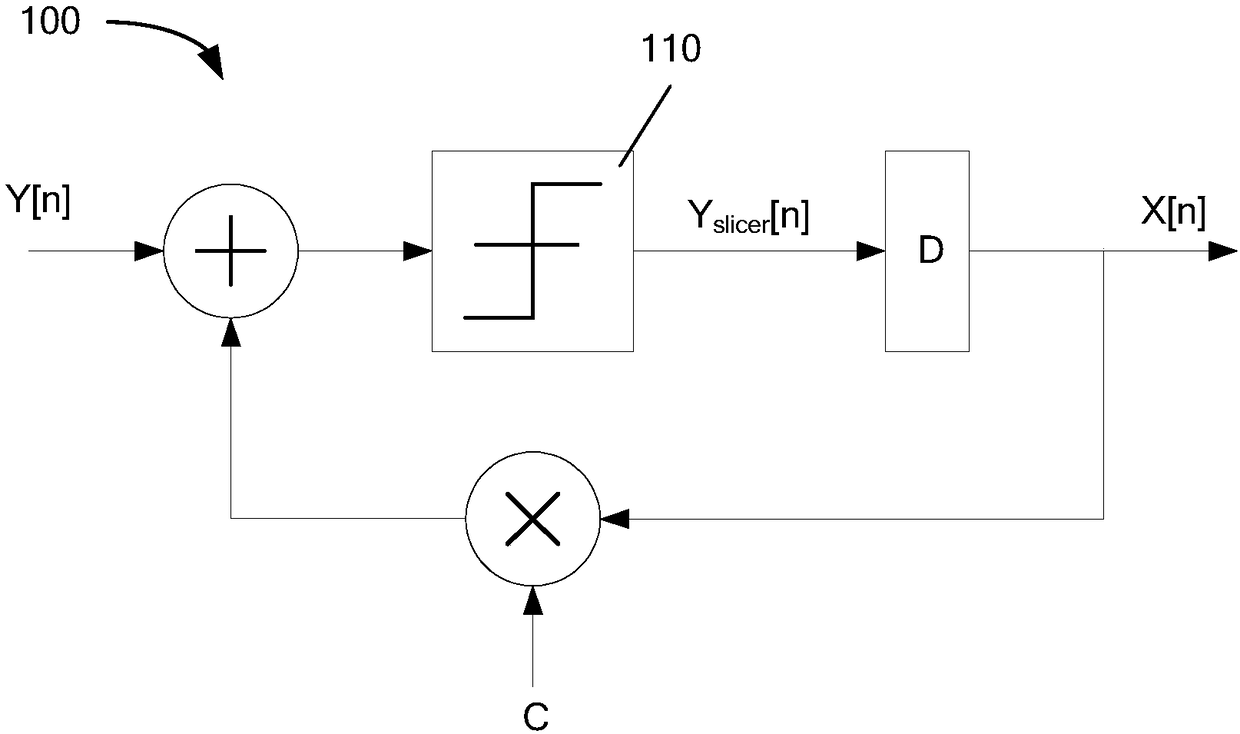

[0022] Figure 1A An example circuit 100 is shown showing a series-connected single-tap (1-tap) decision feedback equalizer (DFE) filter with a feedback loop, where the output X[n] is based on the previous output value X[n- 1] multiplied by the quantized value of the input Y[n] adjusted by the tap coefficient C. In this example, the quantizer 110 (also sometimes referred to as a slicer) is a 2-stage quantizer.

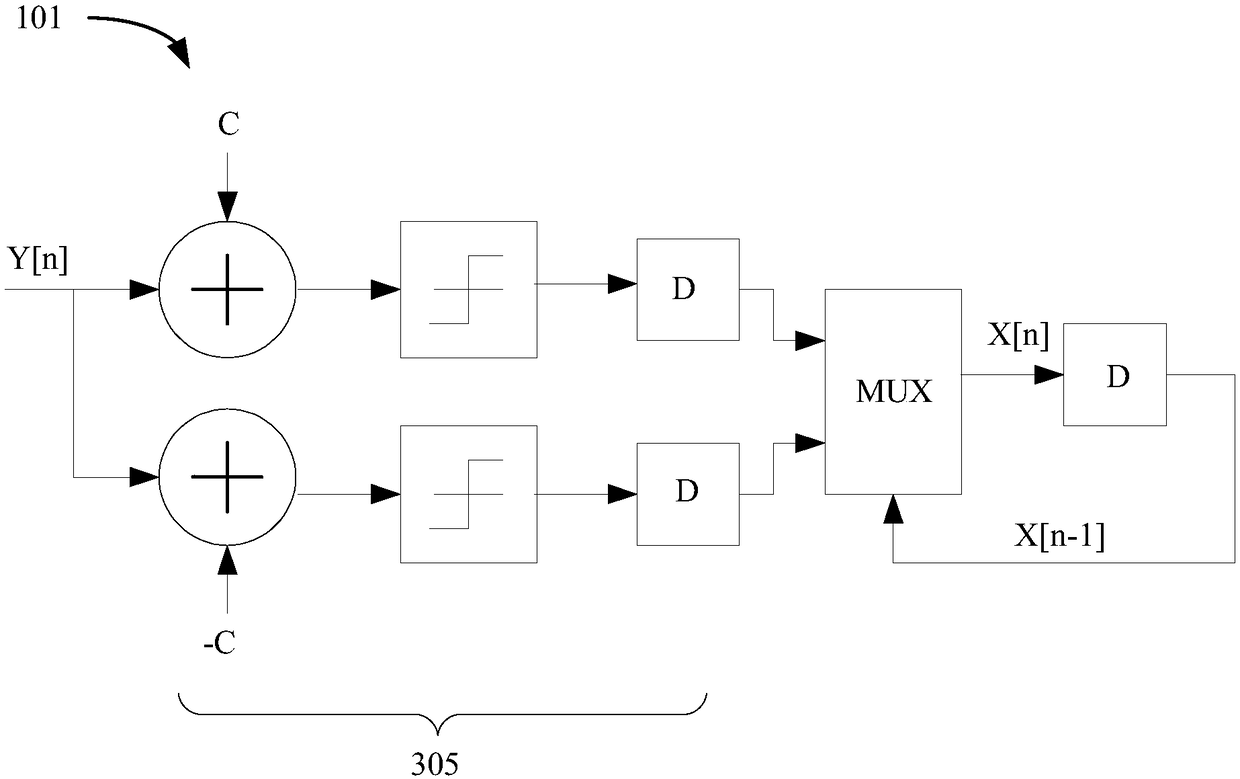

[0023] Figure 1B An example circuit 101 is shown where Figure 1A The circuit 100 adjusts the input value b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com