High-end fault-tolerant computer node interconnection system and realization method

A high-end fault-tolerant, computer technology, applied in the computing field to improve access efficiency, reduce communication delay, and reduce costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

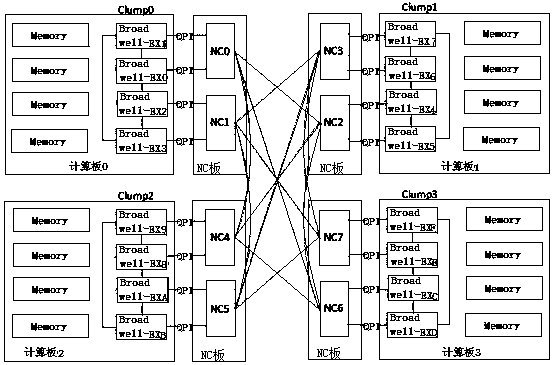

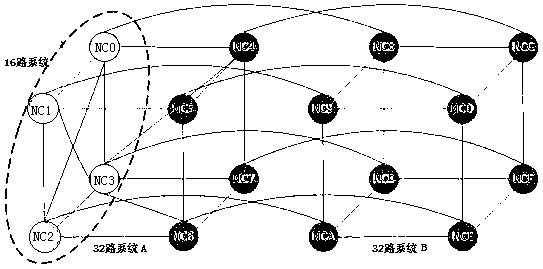

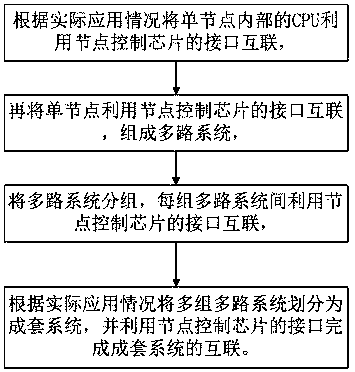

[0018] The invention provides a method for realizing the interconnection of high-end fault-tolerant computer nodes. According to the actual application situation, the CPU inside the single node is interconnected by the interface of the node control chip, and then the single node is interconnected by the interface of the node control chip to form a multi-channel system. Multi-channel systems are grouped, and each group of multi-channel systems is interconnected using the interface of the node control chip. According to the actual application situation, multiple groups of multi-channel systems are divided into complete systems, and the interface of the node control chip is used to complete the interconnection of the complete system.

[0019] At the same time, a high-end fault-tolerant computer node interconnection system corresponding to the above method is provided. According to the actual application situation, the CPU inside the single node is interconnected by the interface of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com