System level chip evaluation device and method

A system-level chip and chip technology, applied in the direction of measurement devices, automated test systems, measurement electronics, etc., can solve problems such as one-sided testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

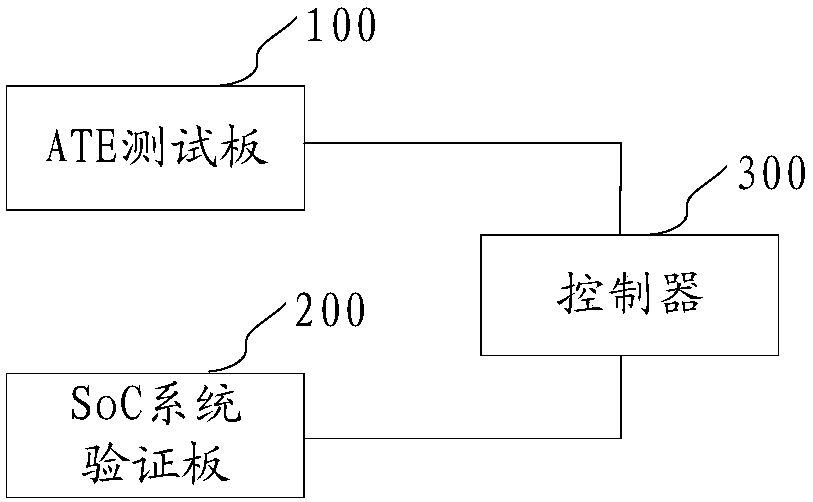

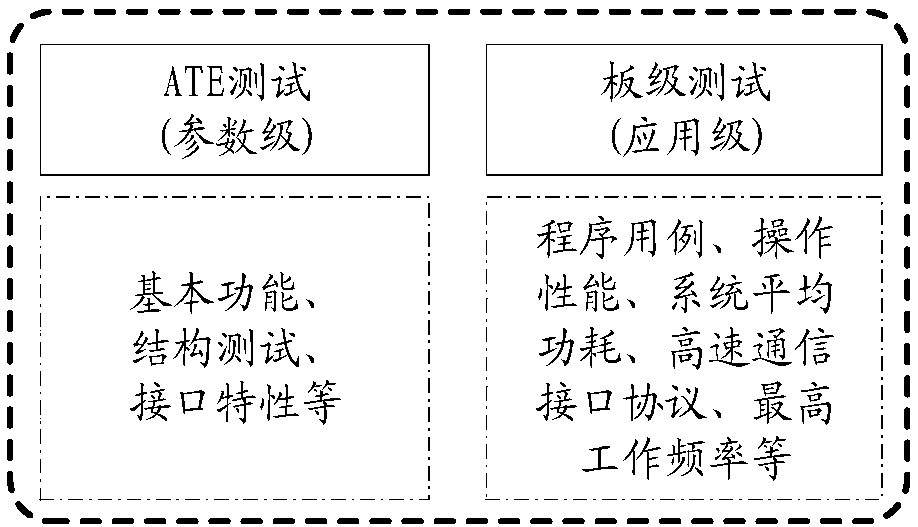

[0030] A system-level chip evaluation device, such as figure 1 As shown, including ATE test board 100, SoC system verification board 200 and controller 300, ATE test board 100 and SoC system verification board 200 are connected with controller 300 respectively; Controller 300 controls ATE test board 100 to obtain the system-on-chip under test Control the SoC system verification board 200 to obtain the application-level data of the system-level chip under test, and obtain the evaluation result of the system-level chip under test according to the parameter-level data and application-level data of the system-level chip under test.

[0031] The ATE test board 100 is used to acquire parameter-level data of the SoC under test. Parameter-level data refers to the data obtained by testing parameters related to SoC chip interface characteristics, including DC parameters, AC parameters, etc., and specific tests are completed under different voltage, current, frequency and load conditions...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More