Single bimetallic plate encapsulation structure and encapsulation method thereof

A bimetallic plate and packaging structure technology, which is applied in the manufacture of electric solid-state devices, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of complicated manufacturing process, high production cost, complicated manufacturing procedure, etc., and achieve simple process and economical manufacturing The effect of cost, yield and stability improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

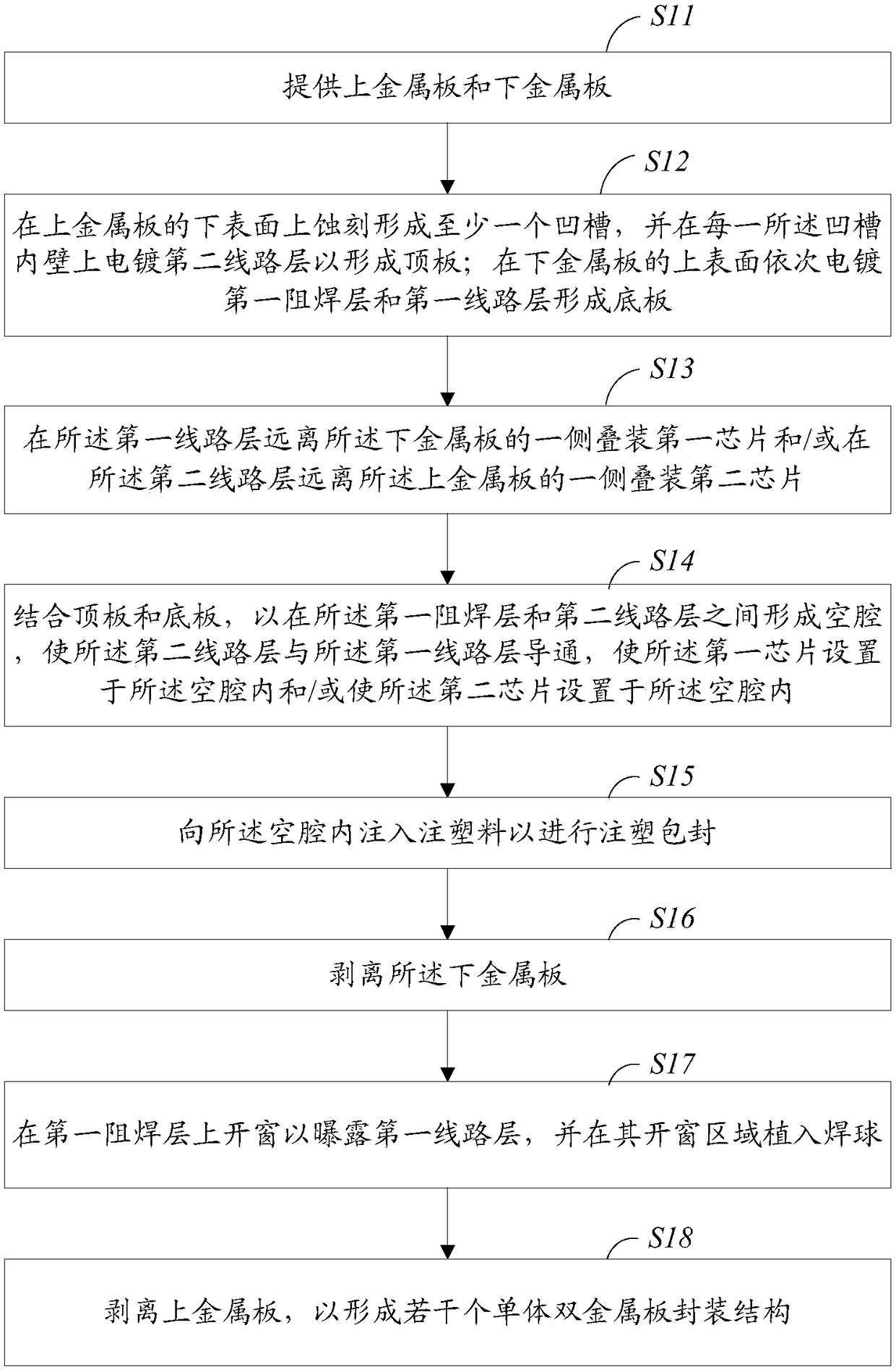

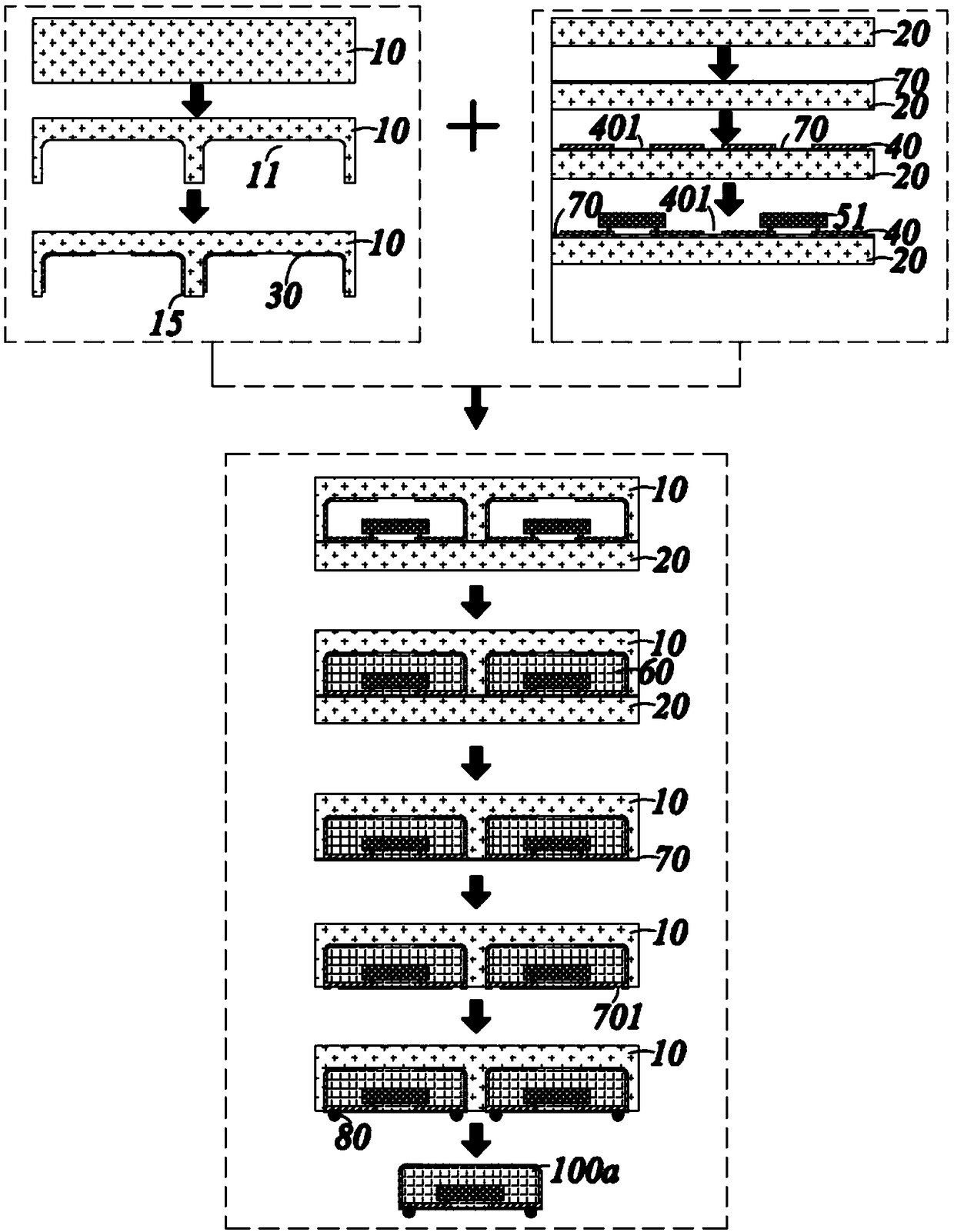

Method used

Image

Examples

Embodiment Construction

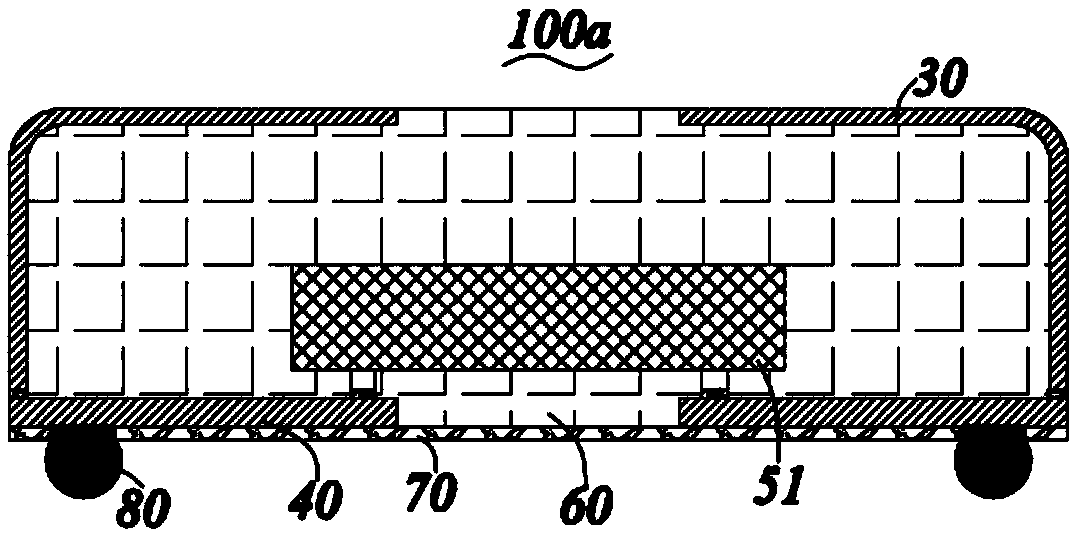

[0054] The present invention will be described in detail below in conjunction with the specific embodiments shown in the drawings. However, these embodiments do not limit the present invention, and the structural, method, or functional changes made by those skilled in the art based on these embodiments are all included in the protection scope of the present invention.

[0055] It should be noted that the terms such as "upper" and "lower" used herein to indicate relative positions in space are for the purpose of facilitating the description to describe one unit or feature as shown in the drawings relative to another unit or feature. Relationship. The term of the relative position in space may be intended to include different orientations of the package structure in use or operation other than the orientation shown in the figure. For example, if the device in the figure is turned over, the unit described as being located on the other unit or feature "the lower surface will be loca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com