High radix subset code multiplier architecture

A technology of multipliers and subsets, applied in the direction of instruments, electrical digital data processing, digital data processing components, etc., can solve the problems of not so efficient, expensive soft multipliers, consuming integrated circuit area, power, routing and/or Packaging resources and other issues to achieve the effects of reduced power consumption, low latency, and improved routability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] While one or more specific embodiments are described below, in an attempt to provide a concise description of these embodiments, not all features of an actual implementation are described in the specification. It should be appreciated that in the development of any such actual implementation, as in any engineering or design project, several implementation-specific decisions may be made to achieve the developer's specific goals, such as compliance with system-related and business-related constraints, This may vary by implementation. Moreover, it should be appreciated that such a development effort might be complex and time consuming, but would nevertheless be a routine undertaking of design, manufacture, and fabrication for those of ordinary skill having the benefit of this disclosure.

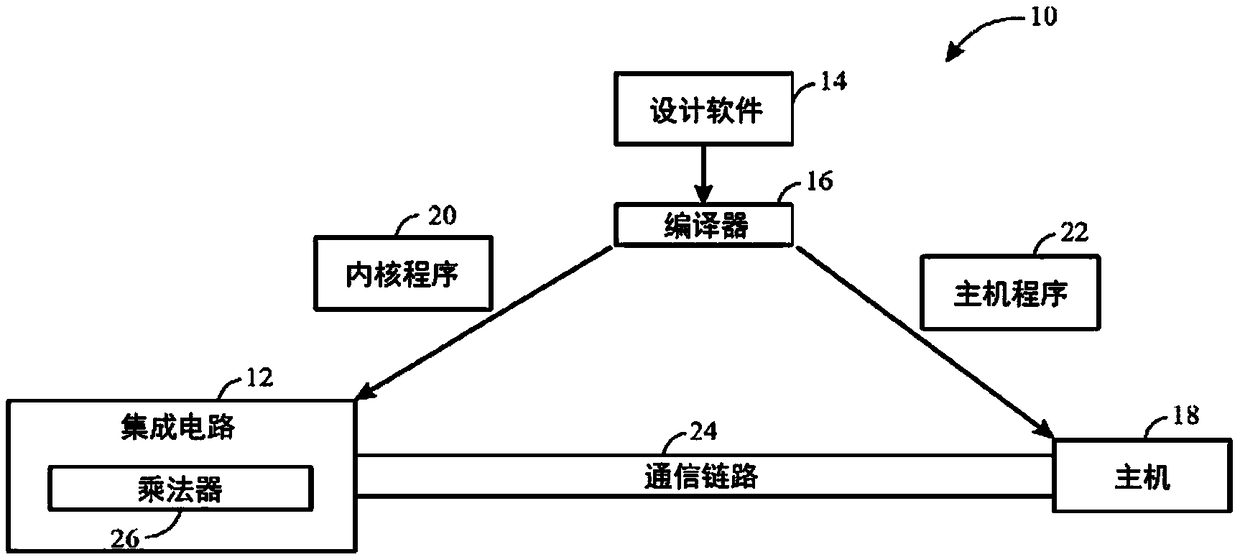

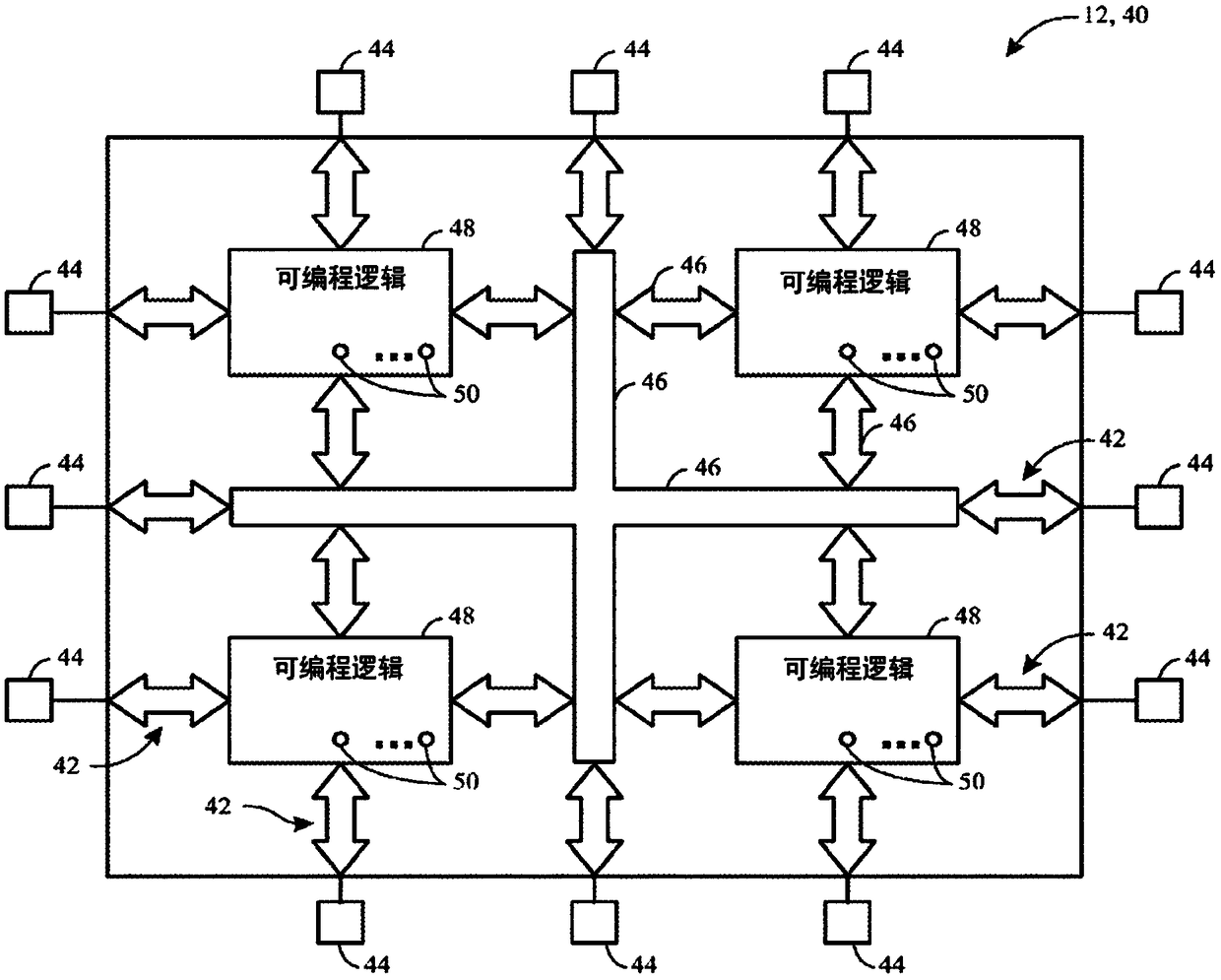

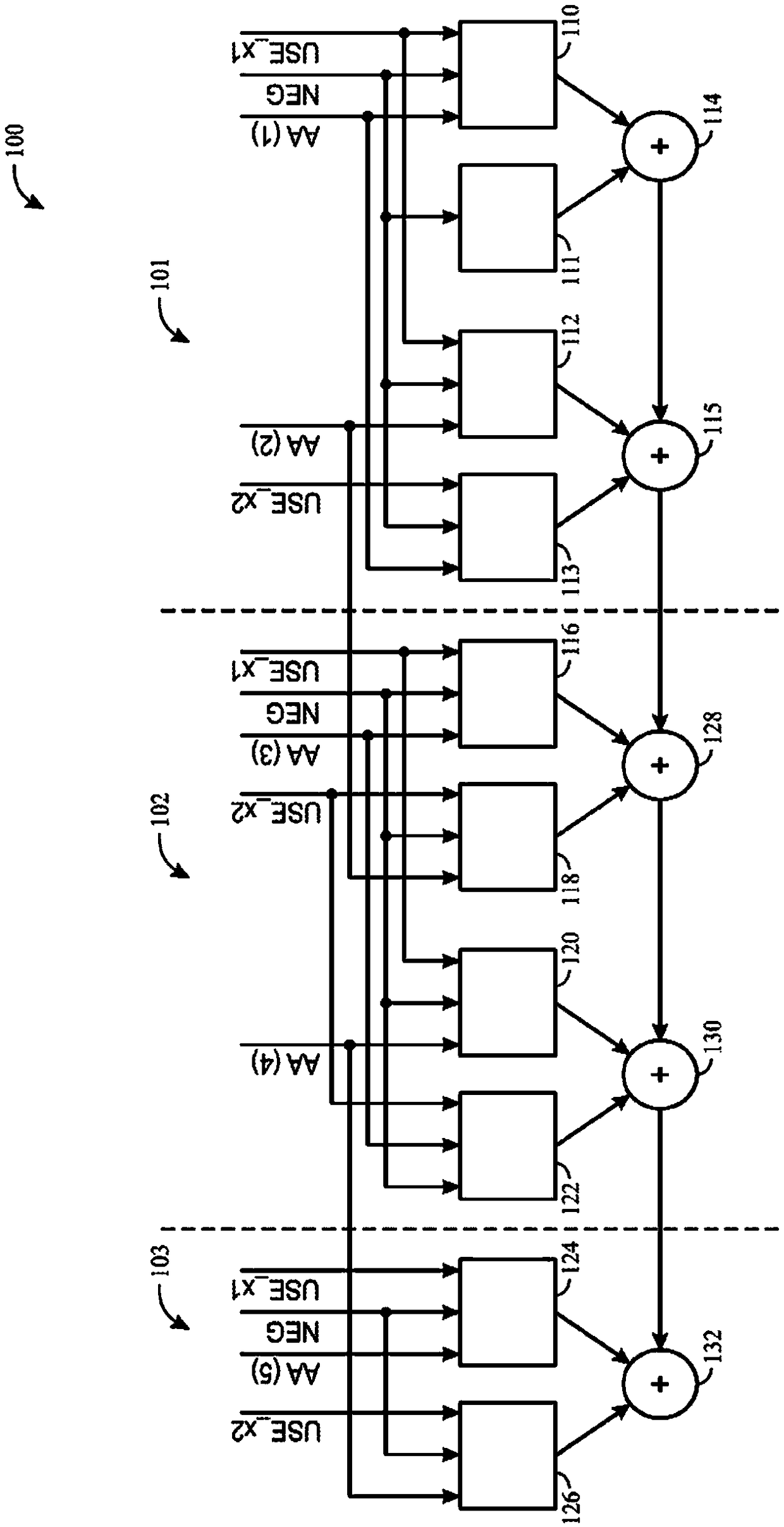

[0020] As described in further detail below, embodiments of the present disclosure generally relate to circuits for enhancing soft multipliers implemented on integrated circuits (ICs). ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More