Bus interface system

A technology of bus interface and signal interface, which is applied in the field of AXI bus interface system, can solve the problems of non-convergence of timing, lengthening of AXI bus, increase of transmission delay, etc., and achieve the effect of optimizing AXI bus timing and correct function

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The present invention will be described in detail below in conjunction with various embodiments shown in the drawings. However, these embodiments do not limit the present invention, and any structural, method, or functional changes made by those skilled in the art according to these embodiments are included in the protection scope of the present invention.

[0015] It should be understood that although the terms first, second, etc. may be used herein to describe various elements or structures, these described objects should not be limited by these terms. These terms are only used to distinguish these described objects from one another. For example, the first shift register module can be called the second shift register module, and similarly the second shift register module can also be called the first shift register module, which does not depart from the protection scope of the present application.

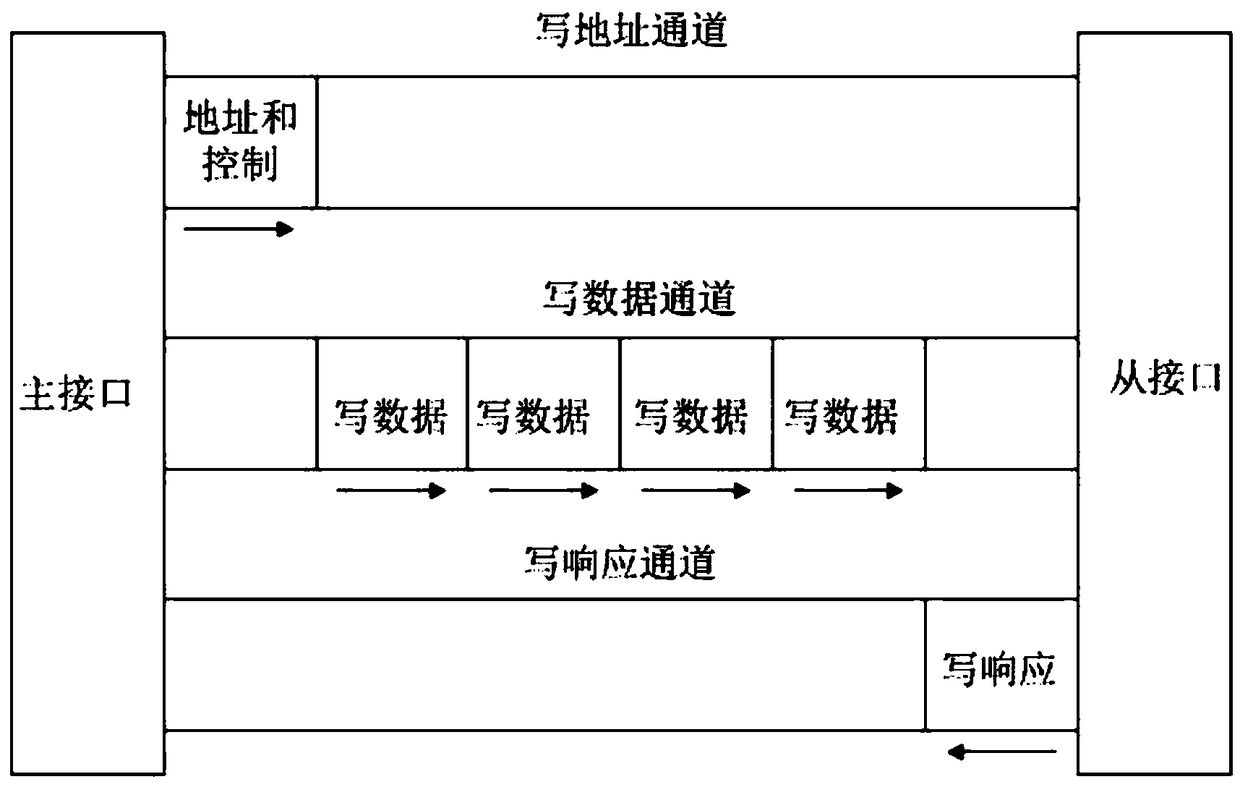

[0016] In the AXI bus protocol, such as figure 1 with figure 2 As ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More