Flash memory structure and corresponding programming, erasing and reading methods

A flash memory, erasing voltage technology, applied in the semiconductor field, can solve the problems of small process window, small erasing saturation process window, small capacitive coupling coefficient, etc., and achieve the effect of avoiding erasing saturation and avoiding the reduction of process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

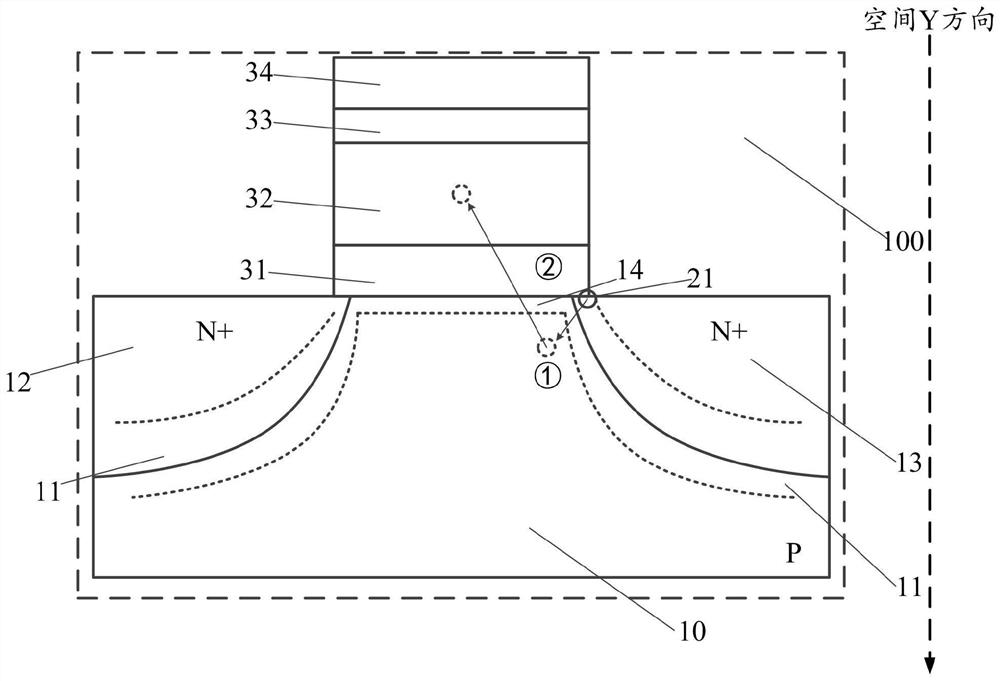

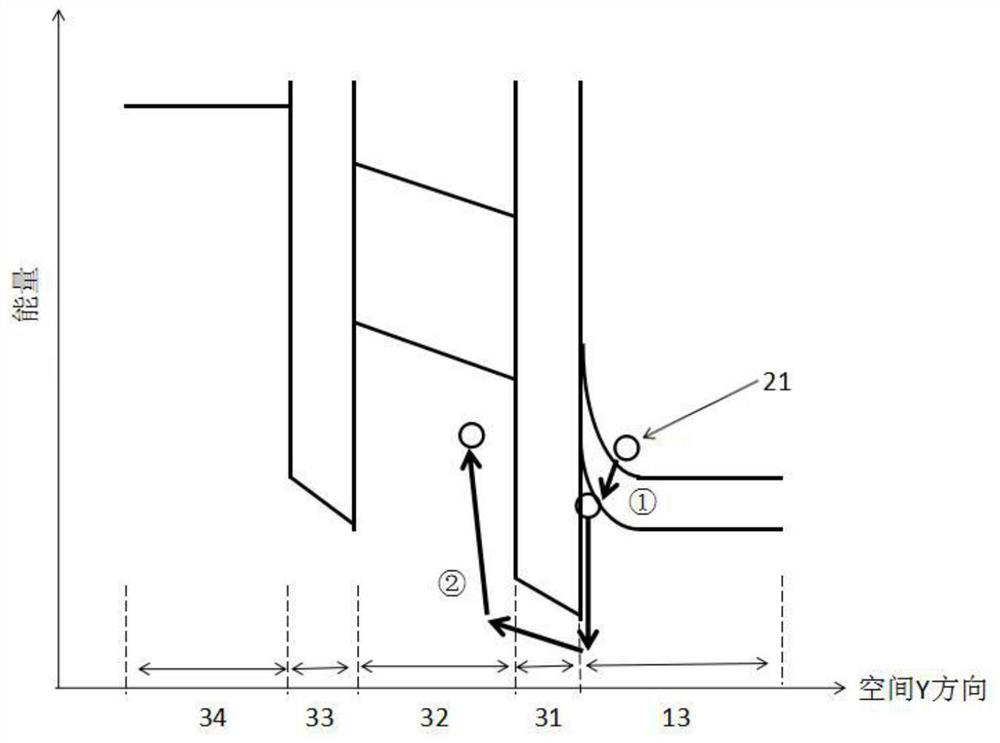

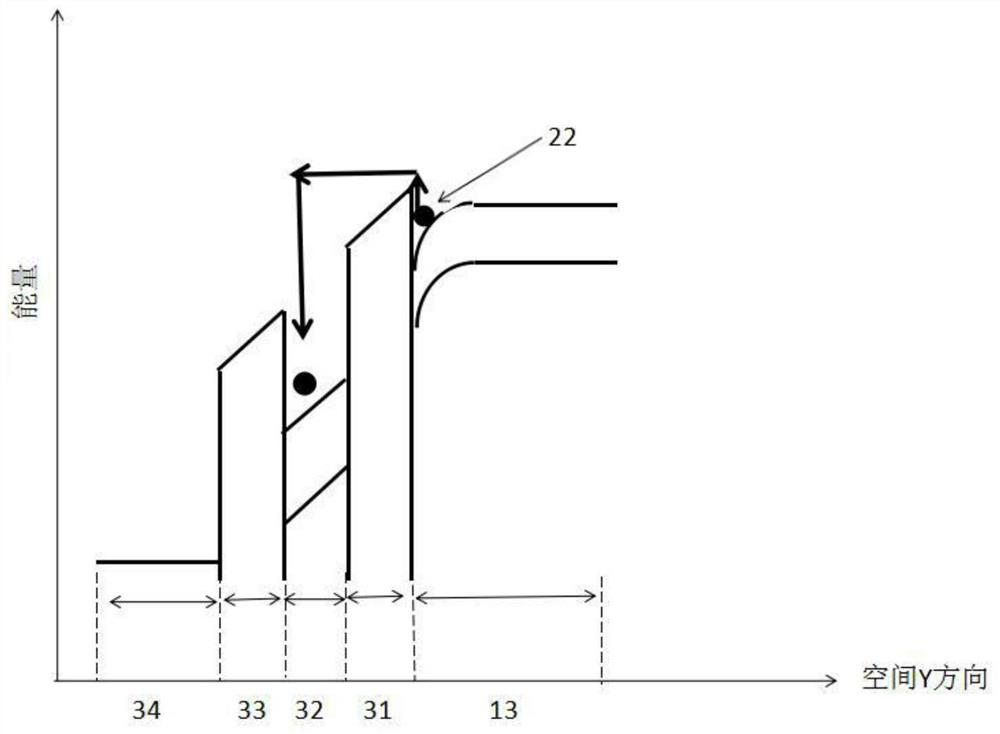

[0028] The present invention will be described in more detail below with reference to schematic diagrams and examples. The advantages and features of the present invention will be more apparent from the following description. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

[0029] In the following description, it will be understood that when a layer (or film), region, pattern or structure is referred to as being "on" a substrate, layer (or film), region and / or pattern, it can be directly on another layer or substrate, and / or intervening layers may also be present. Further, it will be understood that when a layer is referred to as being 'under' another layer, it can be directly under, and / or one or more intervening layers may also be present. In addition, designations regarding 'on' and 'under' each layer ma...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More