Design method of multi-mode HEVC video encoder based on two-chip DSP

A technology of a video encoder and a design method, which is applied in the field of multimedia encoding to achieve the effects of parallelizing work, reducing resource occupancy, and reducing the time occupied by core resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

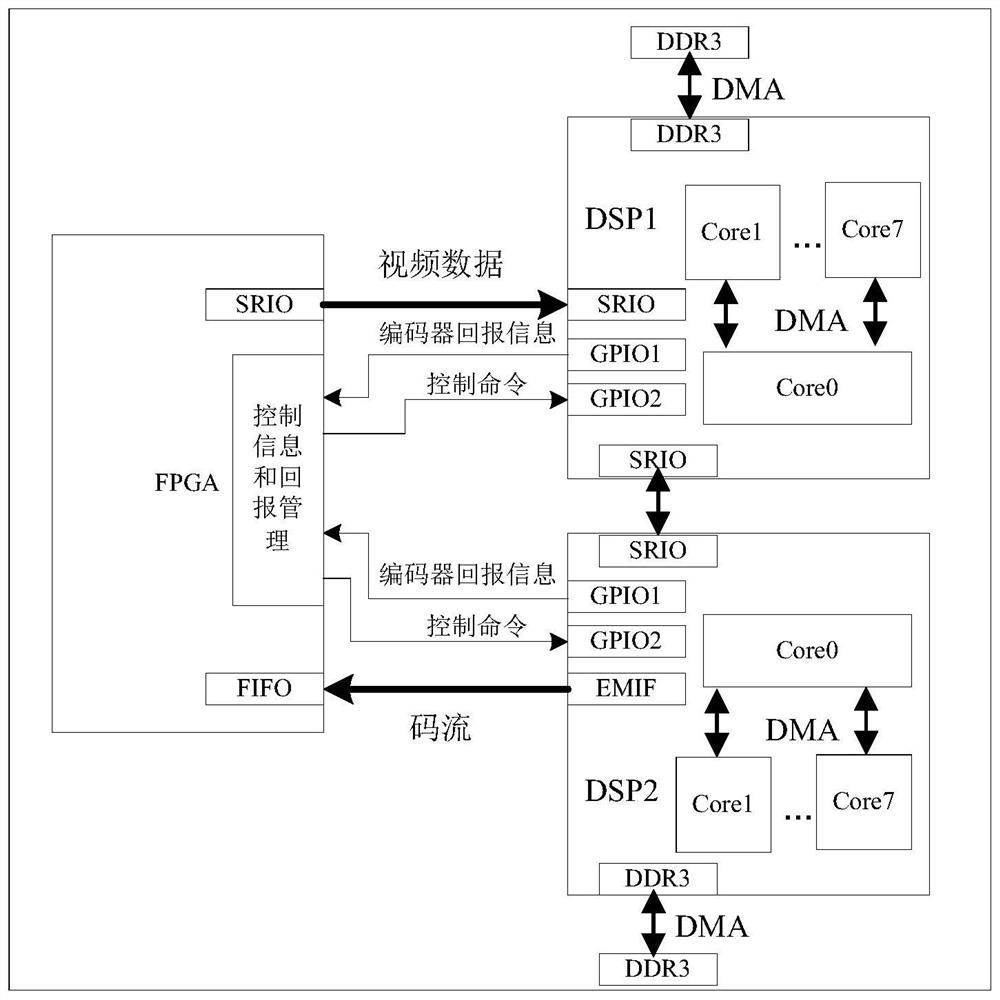

[0050] In order to improve the encoding speed of the HEVC video encoder and meet the real-time compression encoding requirements of multi-mode video, the present invention proposes a design method for a multi-mode HEVC video encoder based on two-chip DSP. In this method, a HEVC parallel encoding framework based on dual-chip multi-core DSP is firstly designed to make full use of the computing resources of dual-chip multi-core DSP. Secondly, an efficient dual-chip DSP data communication mechanism is designed to realize high-speed transmission of multi-mode coded data between chips and inside chips through SRIO, DMA and EMIF. Finally, a self-checking mechanism of a double-chip DSP encoder is designed. Realize the detection of the abnormal operation of the encoder. The following is a detailed description.

[0051] A kind of multi-mode HEVC video...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More