Deep trench isolation structure of cmos image sensor and its manufacturing method

A deep trench isolation, image sensor technology, applied in semiconductor devices, electric solid state devices, radiation control devices, etc., can solve the problems of low potential well capacity, inability to extend, isolation, etc., to increase the area and reduce the width. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0063]Some embodiments are listed below and described in detail with the accompanying drawings, but the provided embodiments are not intended to limit the scope of the present invention. In addition, the drawings are for illustration purposes only and are not drawn to original scale. In order to facilitate understanding, the same elements in the following description will be described with the same symbols. In addition, terms such as "comprising", "including", and "having" used in the text are all open terms; that is, including but not limited to. Moreover, the directional terms mentioned in the text, such as: "up", "down", etc., are only used to refer to the directions of the drawings. Accordingly, the directional terms used are for the purpose of description, not limitation of the invention.

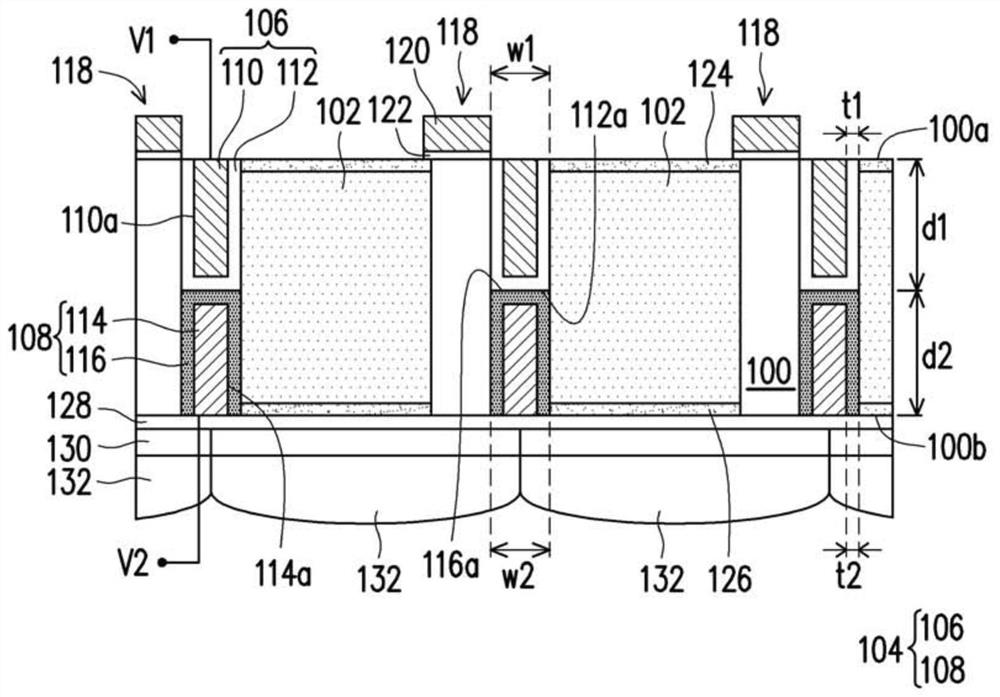

[0064] figure 1 is a schematic cross-sectional view of a CMOS image sensor (CIS) including a deep trench isolation structure (DTI) according to the first embodiment of the present i...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com