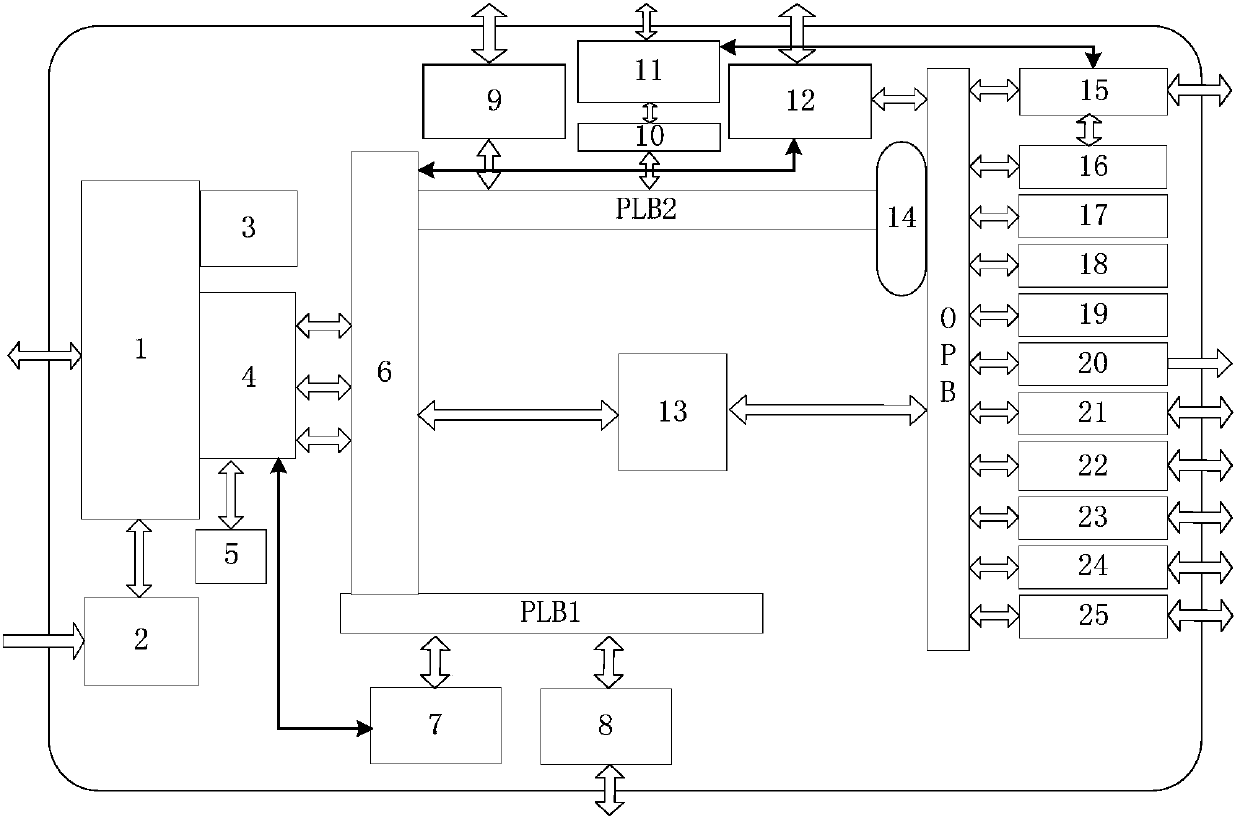

Circuit of multi-bus reconfigurable processor chip

A processor, multi-bus technology, applied in electrical program control, program control in sequence/logic controllers, etc., to achieve low power consumption, high-performance data processing capabilities, and meet the needs of miniaturization.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be further described below in conjunction with accompanying drawing and embodiment:

[0017] see figure 1 The multi-bus reconfigurable processor chip circuit structure of the present invention includes a processor core, an interrupt controller, a floating-point processing unit, a secondary Cache controller, an SRAM memory, a PLB arbiter, an SRAM controller, an SDRAM controller, and a 1553B protocol Processor, FPGA core interface, FPGA core, Ethernet interface, DMA controller, PLB to OPB bridge, FPGA core loading circuit, EBC memory interface, watchdog, timer, real-time clock, pulse width modulation, LVDS interface, 429 Bus controller, serial port controller, IIC interface and general input and output modules. The processor core is directly connected to the interrupt controller, the floating-point processing unit, and the secondary cache controller. The secondary cache controller is directly connected to the SRAM memory and the PLB arbiter. Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com