Chip scale package structures

A wafer-level chip and size packaging technology, which is applied to semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problem of rising overall chip costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

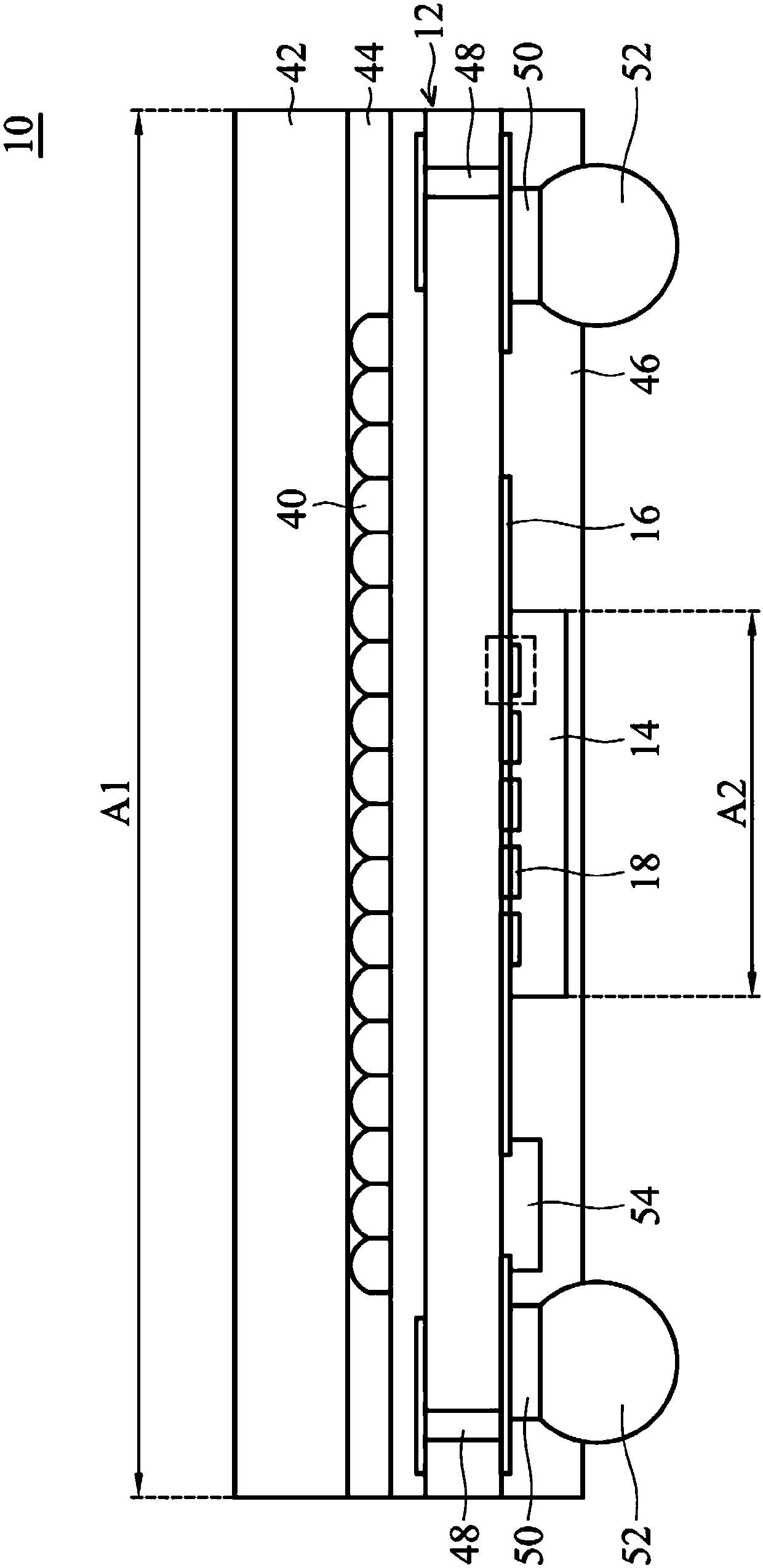

[0056] See figure 1 According to an embodiment of the present invention, a wafer level chip scale package (WLCSP) structure 10 is disclosed. figure 1 It is a schematic cross-sectional view of a wafer level chip scale package (WLCSP) structure 10.

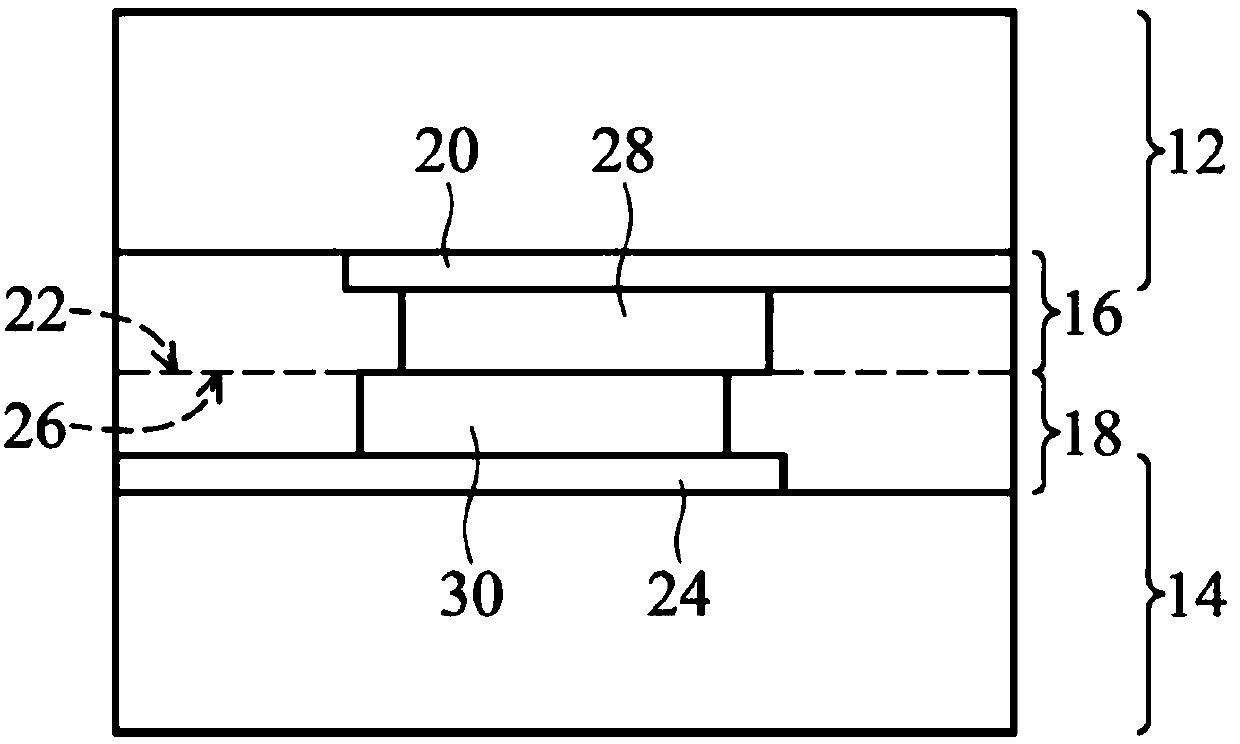

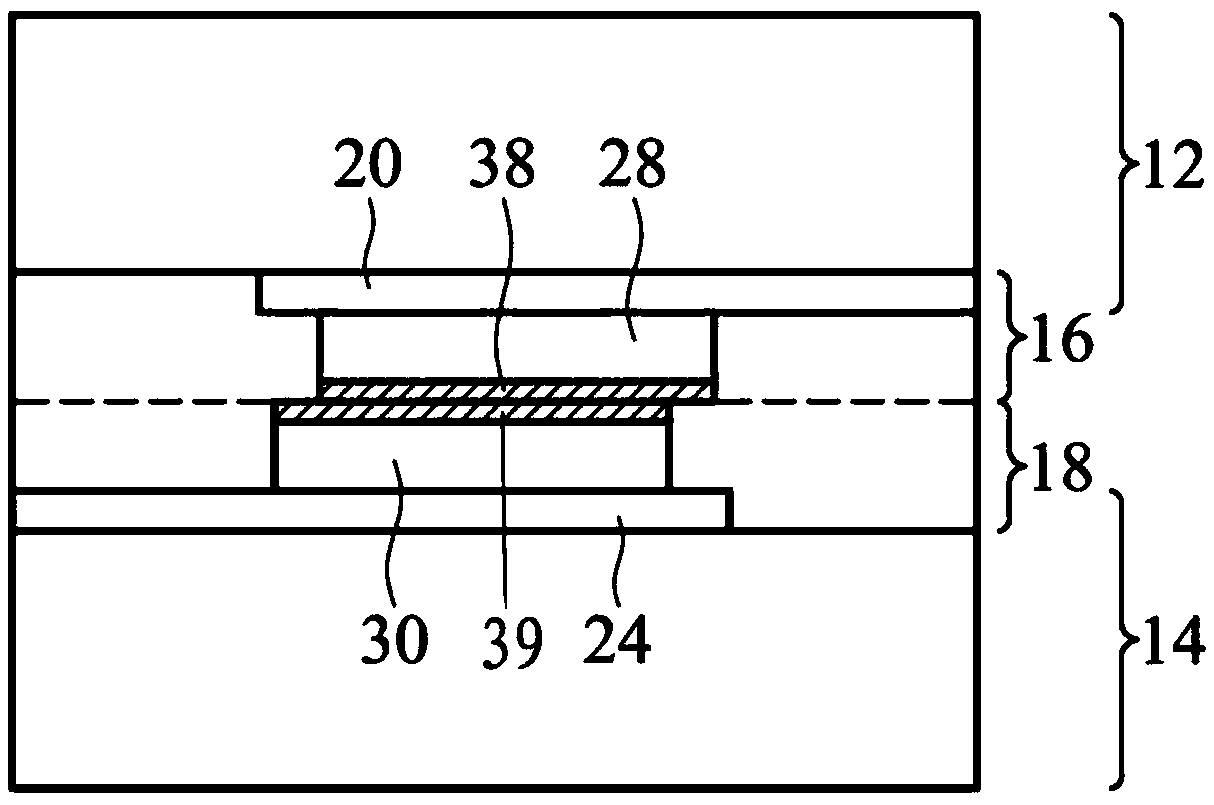

[0057] In this embodiment, the wafer level chip scale package (WLCSP) structure 10 includes an image sensor chip 12 and a chip 14. The image sensor chip 12 includes a first redistribution layer 16. The chip 14 includes a second redistribution layer 18. The area A2 of the chip 14 is smaller than the area A1 of the image sensor chip 12. The internal structure of the first redistribution layer 16 and the second redistribution layer 18 and the bonding state between the image sensor chip 12 and the chip 14 (in the dotted frame in the figure) will be described in detail later.

[0058] In some embodiments, the image sensor chip 12 can also be replaced by other sensor chips, such as an acoustic wave sensor chip, a temperature sensor chip, a h...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com