Information processing system, semiconductor integrated circuit, and information processing method

An information processing system and integrated circuit technology, which is applied in the field of information processing systems, can solve the problems of not waiting, limiting the high-speed cluster, etc., and achieve the effect of high-speed processing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example

[0023] (First embodiment)

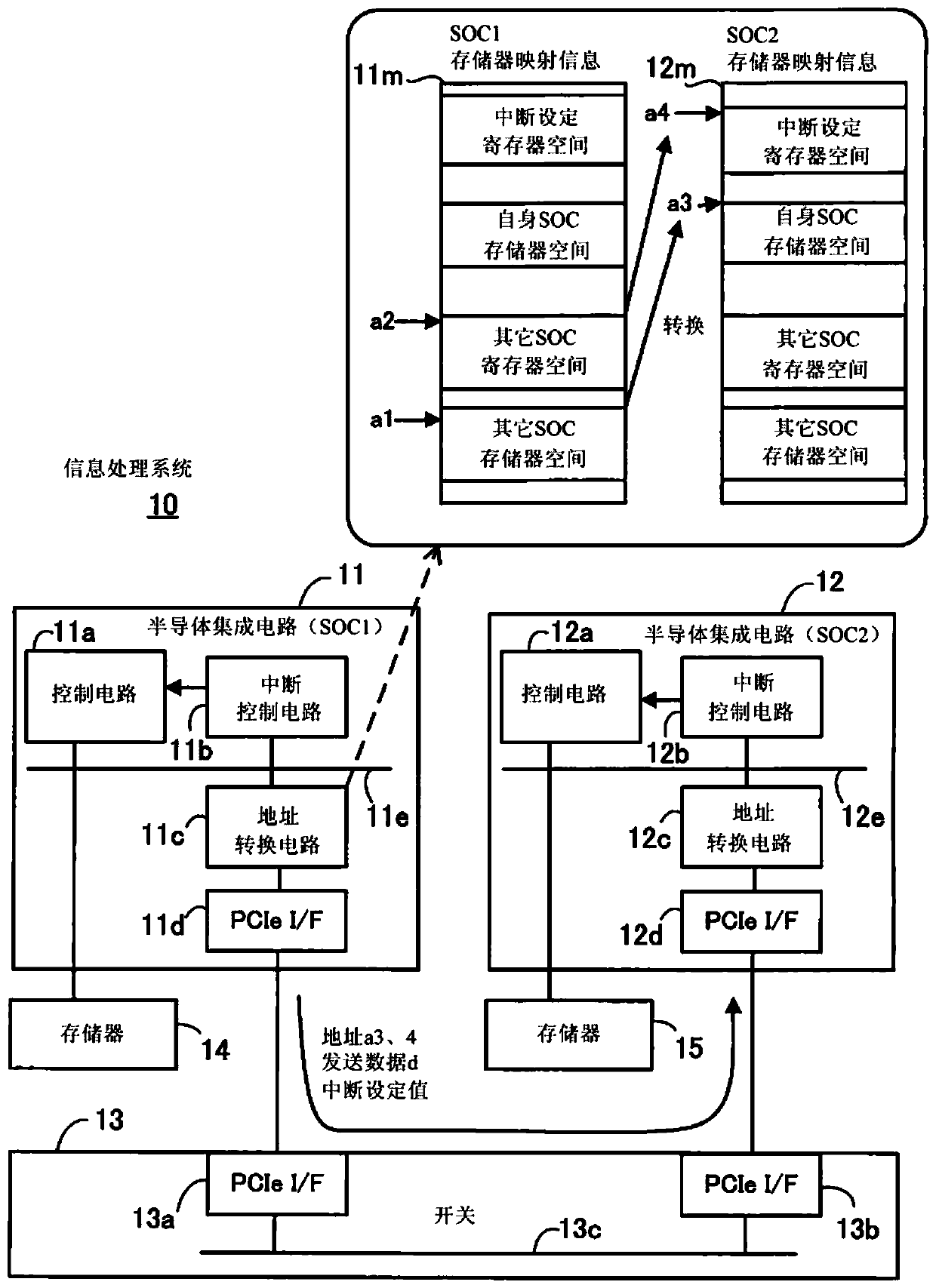

[0024] figure 1 It is a diagram showing an example of the information processing system of the first embodiment.

[0025] The information processing system 10 has semiconductor integrated circuits 11 and 12, switches 13, and memories 14, 15.

[0026] The semiconductor integrated circuits 11 and 12 and the switch 13 are each, for example, a one-chip SoC. in figure 1 In order to simplify the description, two semiconductor integrated circuits 11 and 12 and one switch 13 are shown, but the number is not limited to this. An example of an information processing system having three or more semiconductor integrated circuits and two or more switches will be described later.

[0027] The semiconductor integrated circuit 11 has a control circuit 11a, an interrupt control circuit 11b, an address conversion circuit 11c, a PCIe interface (I / F) 11d, and a system bus 11e. In addition, a memory 14 is connected to the semiconductor integrated circuit 11.

[0028] The contro...

Example

[0055] (Second embodiment)

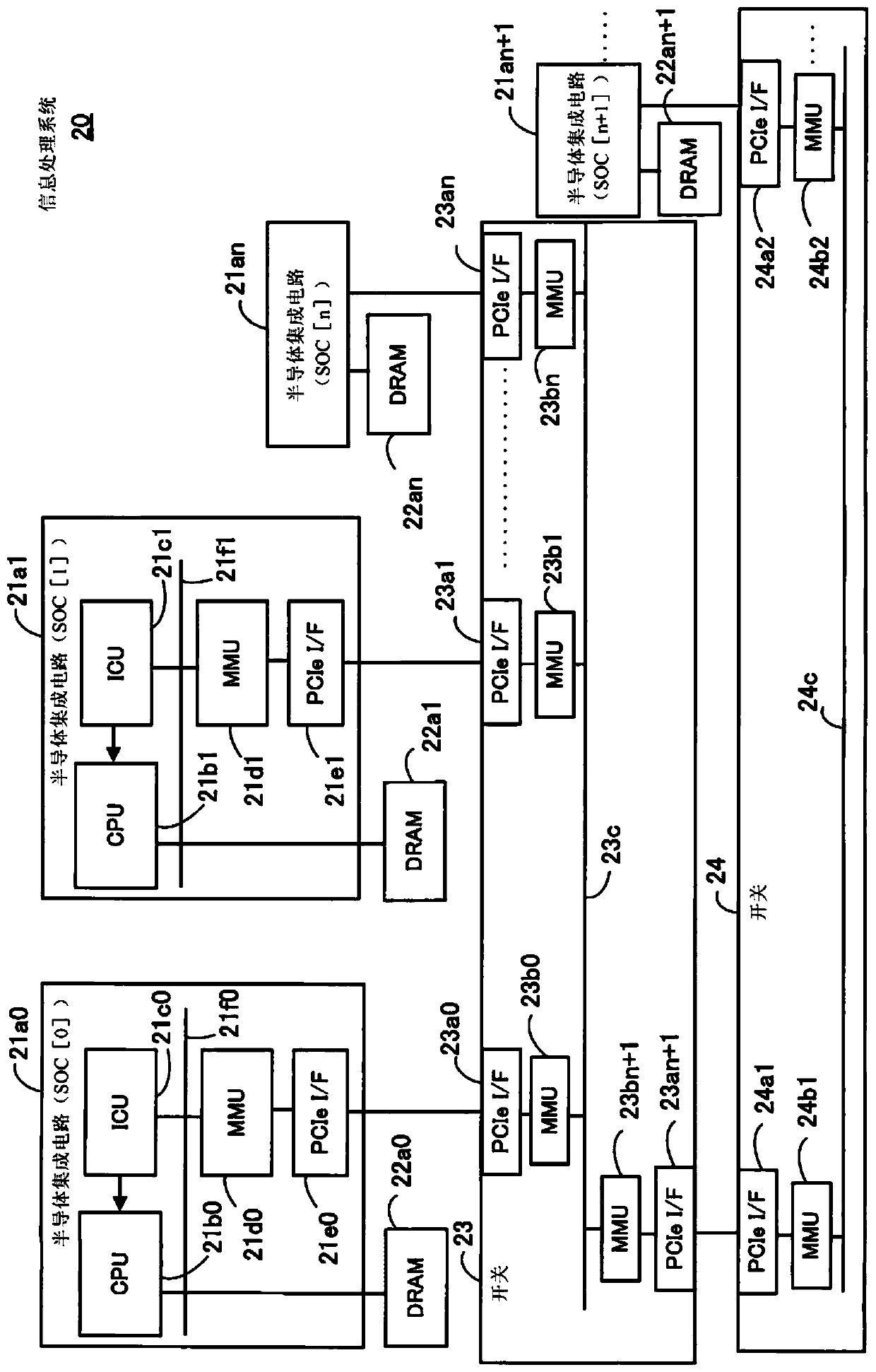

[0056] figure 2 It is a diagram showing an example of the information processing system of the second embodiment.

[0057] The information processing system 20 includes a plurality of semiconductor integrated circuits including semiconductor integrated circuits 21a0, 21a1, 21an, 21an+1, and a plurality of DRAMs including DRAM 22a0, 22a1, 22an, 22an+1. There are also two-stage switches 23 and 24.

[0058] The semiconductor integrated circuit 21a0 has a CPU 21b0, an ICU (Interrupt Controller Unit) 21c0, an MMU (Memory Management Unit) 21d0, a PCIe interface 21e0, and a system bus 21f0. In addition, the semiconductor integrated circuit 21a0 is connected to the DRAM 22a0.

[0059] CPU21b0 is figure 1 An example of the control circuit 11a shown controls each part of the semiconductor integrated circuit 21a0 via the system bus 21f0.

[0060] ICU21c0 is figure 1 The illustrated example of the interrupt control circuit 11b notifies the CPU 21b0 of the occurrence ...

Example

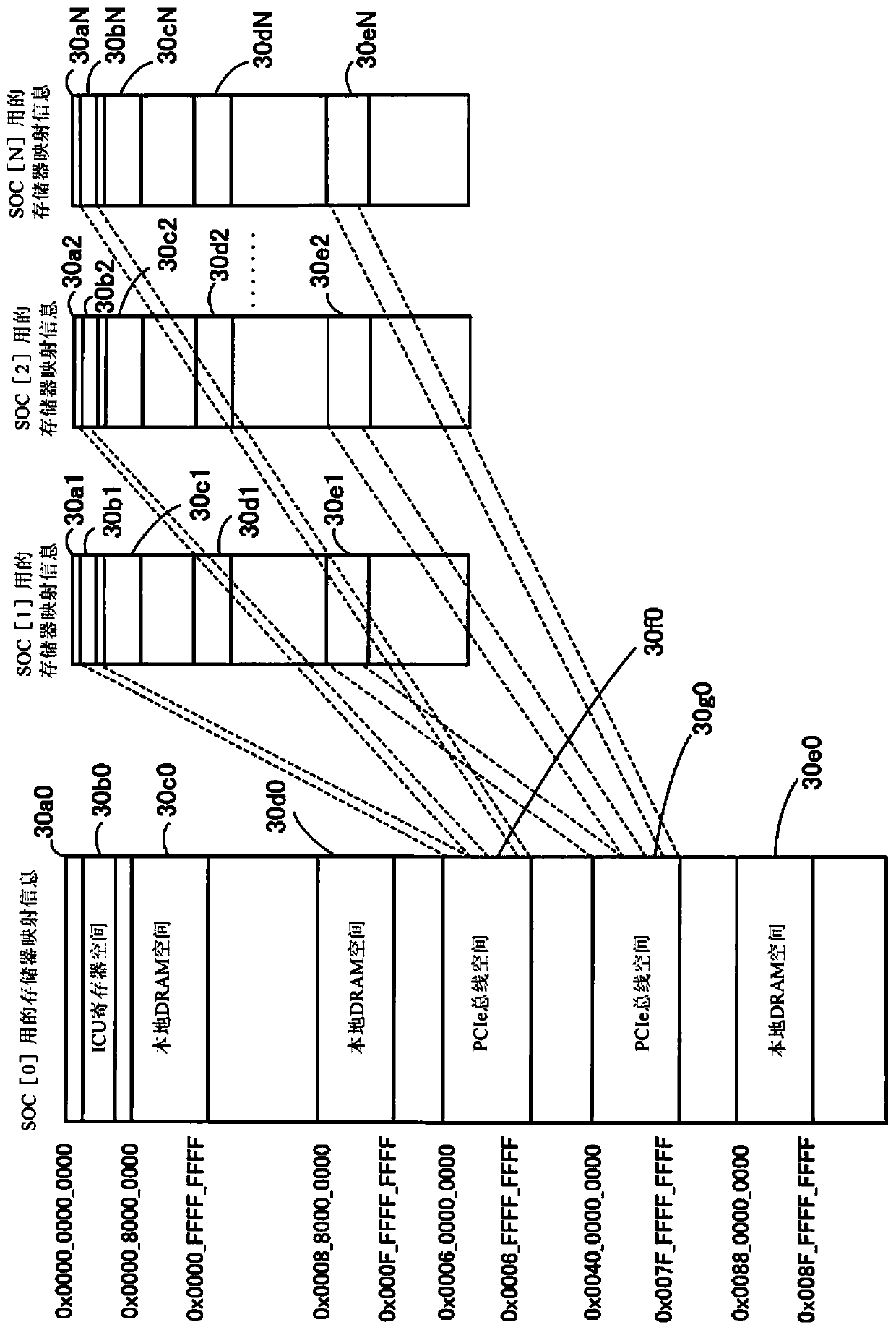

[0125] (Third embodiment)

[0126] Figure 8 It is a diagram showing an example of the information processing system of the third embodiment. in Figure 8 In, for and figure 2 The same elements of the information processing system 20 of the second embodiment shown are denoted by the same reference numerals. In the following, N semiconductor integrated circuits including semiconductor integrated circuits 41a0 to 41an+1 are referred to as SOC[0] to SOC[N]. For example, the semiconductor integrated circuit 41a0 is referred to as SOC[0], and the semiconductor integrated circuit 41a1 is referred to as SOC[1].

[0127] In the information processing system 40 of the third embodiment, two or more of SOC[0] to SOC[N] are connected to memories different from DRAM. in Figure 8 In the example, the memory 42a0 is connected to SOC[0], the memory 42an is connected to SOC[n], and the memory 42an+1 is connected to SOC[n+1].

[0128] The memories 42a0 to 42an+1 are information storage devices eac...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap