A display verification method

A verification method and display technology, which can be applied to static indicators, instruments, etc., can solve problems such as failure to find distortion, affecting pixel structure conversion pixel grayscale algorithm verification of display panels, and data distortion.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The technical solutions in the embodiments of the present application will be clearly and completely described below in conjunction with the drawings in the embodiments of the present application. Apparently, the described embodiments are only some of the embodiments of this application, not all of them. Based on the embodiments in this application, all other embodiments obtained by those skilled in the art without making creative efforts belong to the scope of protection of this application.

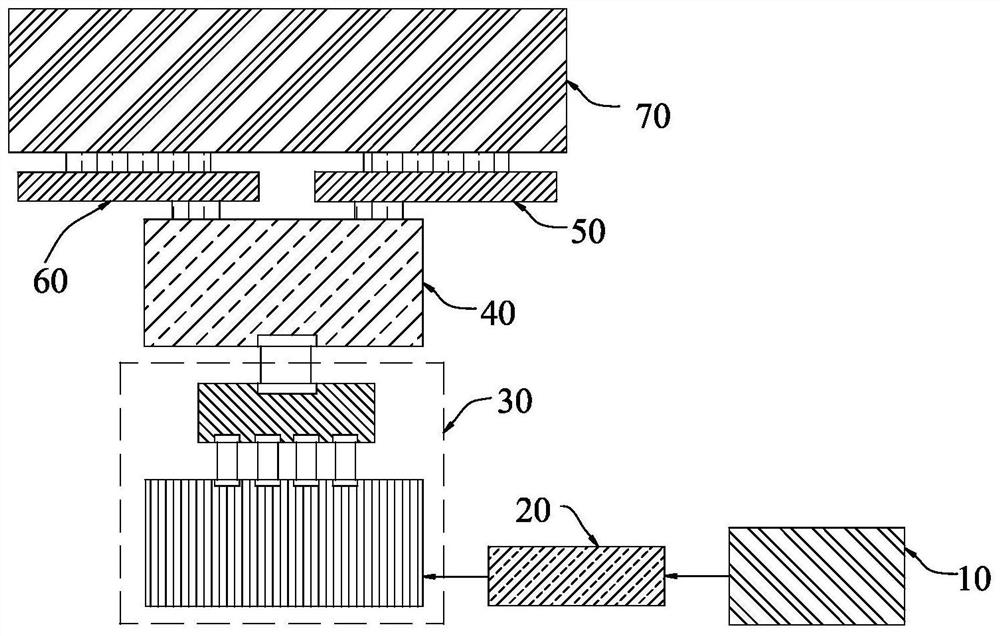

[0024] Please refer to figure 1 , which shows a schematic structural diagram of a display verification device provided according to an embodiment of the present invention, the display verification device includes a PC (Personal Computer, personal computer) 10, a conversion circuit 20, an FPGA (field programmable gate array, field programmable logic gate Array) platform 30, timing control circuit 40, scan driving circuit 50, data driving circuit 60 and display panel 70. The scan...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More