Method and system for adding reverse exposure assist feature

A technology of auxiliary graphics and reverse exposure, which is applied in the photo-engraving process of optics, pattern surface, and originals for opto-mechanical processing. window and other issues, to reduce risks and improve the effect of process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0044] The present invention provides the first embodiment of the method for adding reverse exposure auxiliary graphics for the linear test layout of semiconductor chips, including the following steps:

[0045] S1, filter out the area where the reverse exposure auxiliary graphics are added at the edge of the test layout through logical operations;

[0046] S2, according to the distance between the edge lines of the test layout, the reverse exposure auxiliary graphic addition area is divided into different reverse exposure auxiliary graphic addition types;

[0047] S3, determining the parameter range for adding reverse exposure auxiliary graphics according to the established process window OPC model;

[0048] S4, obtaining the process fluctuation bandwidth value (PV-band) obtained after adding reverse exposure auxiliary graphics based on the process window OPC model as the process window size evaluation standard;

[0049] S5, add reverse exposure auxiliary graphics of differen...

no. 2 example

[0051] The present invention provides the second embodiment of the reverse exposure auxiliary pattern adding method for the linear test layout of the semiconductor chip, comprising the following steps:

[0052] S1, screen out the area with the line width of the edge line greater than or equal to N times the line width of its adjacent lines on the edge of the test layout through logical operation as the area to add the reverse exposure auxiliary graphics, N>1.

[0053] S2, according to the distance between the edge lines of the test layout, the reverse exposure auxiliary graphic addition area is divided into different reverse exposure auxiliary graphic addition types;

[0054] S3, determining the parameter range for adding reverse exposure auxiliary graphics according to the established process window OPC model;

[0055] S4, obtaining the process fluctuation bandwidth value (PV-band) obtained after adding reverse exposure auxiliary graphics based on the process window OPC model...

no. 3 example

[0057] The present invention provides the third embodiment of the reverse exposure auxiliary pattern adding method for the linear test layout of the semiconductor chip, comprising the following steps:

[0058] S1, screen the edge of the test layout through logical operations, and select the area where the line width of the edge line is greater than or equal to 2.5 times the line width of its adjacent line as the area to add the reverse exposure auxiliary graphics.

[0059] S2, according to the distance between the edge lines of the test layout, the addition type is divided in the following way;

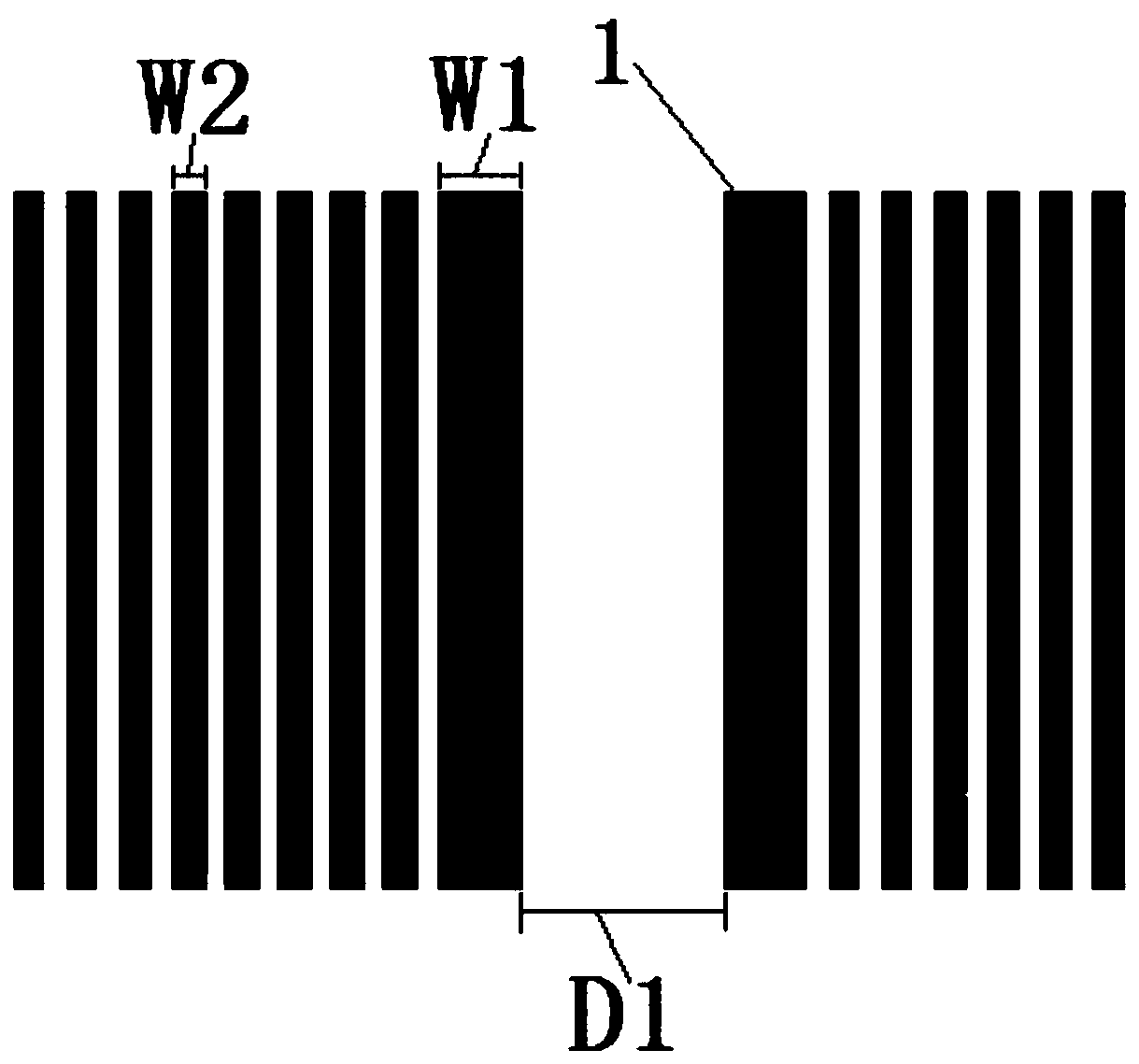

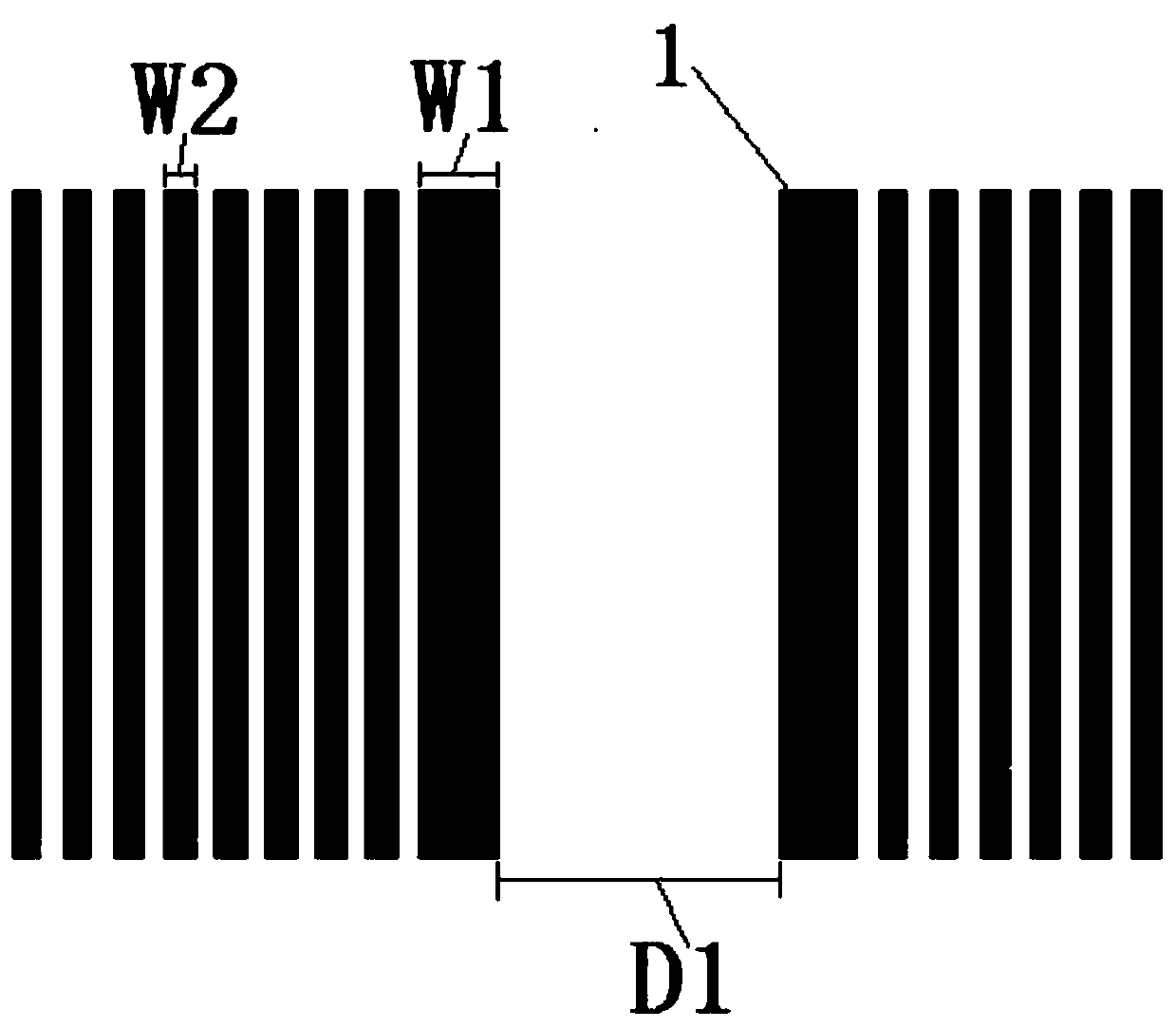

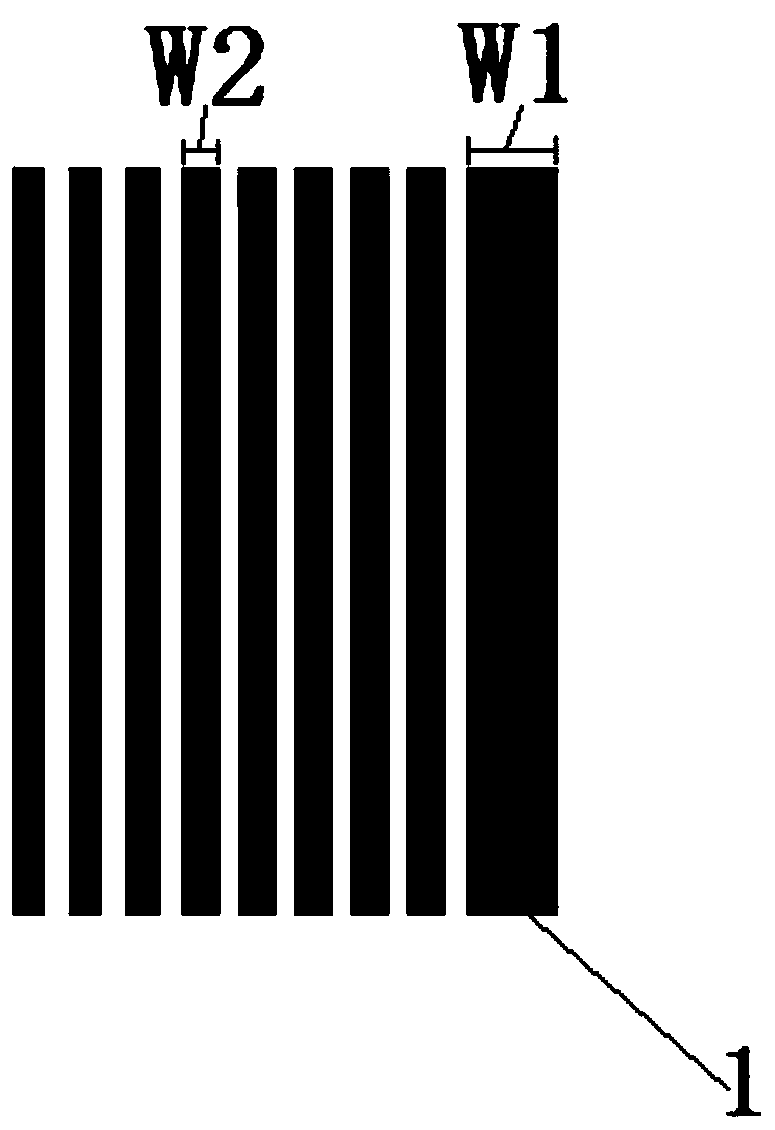

[0060] D1≤(A×W1), then the addition area of the reverse exposure auxiliary figure is divided into the first type of addition type;

[0061] (A×W1)

[0062] (B×W1)≤D1, then the addition area of the reverse exposure auxiliary figure is divided into the thir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More