A method for quickly estimating the copper thickness of pcb via holes

A technology for PCB board and surface copper thickness, which is applied to printed circuits, instruments, measuring devices, etc. It can solve the problems of limited test probe size, inability to test copper thickness in holes, and inability to test copper thickness in via holes, etc., to ensure production Quality, the effect of controlling production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

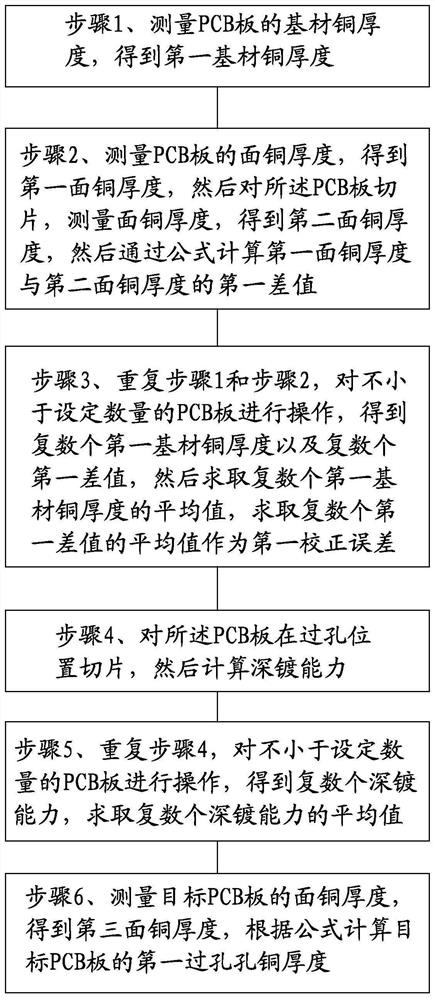

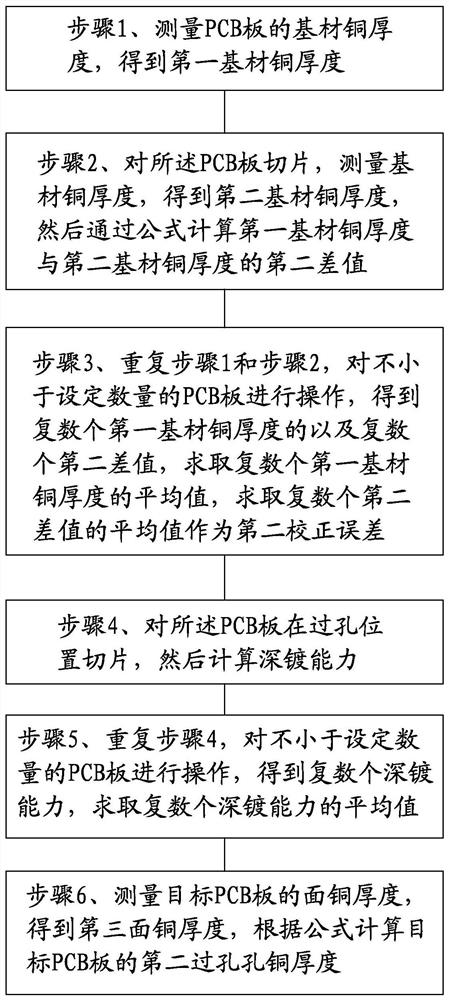

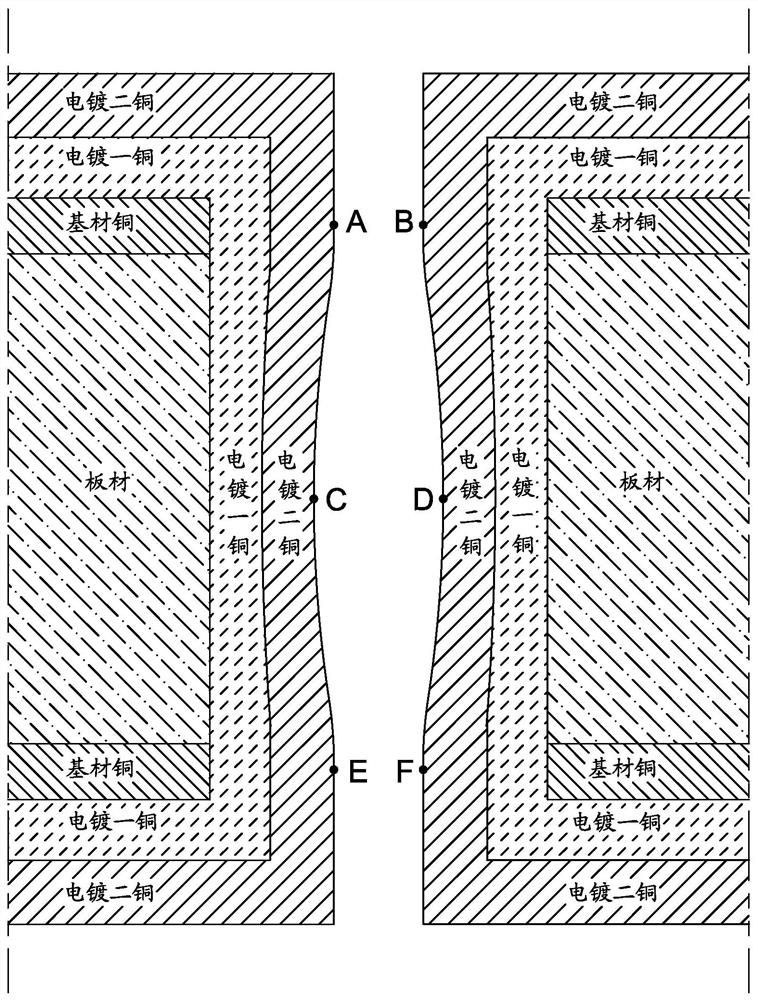

[0052] Please refer to figure 1 , image 3 and Figure 4 , one of the embodiments of the present invention, a method for quickly estimating the copper thickness of a PCB via hole, comprising the following steps:

[0053] A method for rapidly estimating the copper thickness of PCB via holes, comprising the following steps:

[0054] Step 1. Measure the substrate copper thickness of the PCB board at a copper surface position not less than a set area (such as 10mm×10mm) by a surface copper tester to obtain the first substrate copper thickness;

[0055] Step 2. Measure the surface copper thickness of the PCB board at a copper surface position not smaller than the set area (such as 10mm×10mm) by a surface copper tester to obtain the first surface copper thickness, and then use the slicing technology to measure the surface copper thickness of the PCB board on the same surface. Slice the position of the copper surface, measure the copper thickness of the surface, and obtain the cop...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More