A high voltage p-channel hfet device

A channel and device technology, applied in the field of p-channel HFET devices, can solve the problems of limited breakdown voltage increase and difficult process, and achieve the effects of small on-resistance, parasitic capacitance of the withstand voltage structure, and high breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

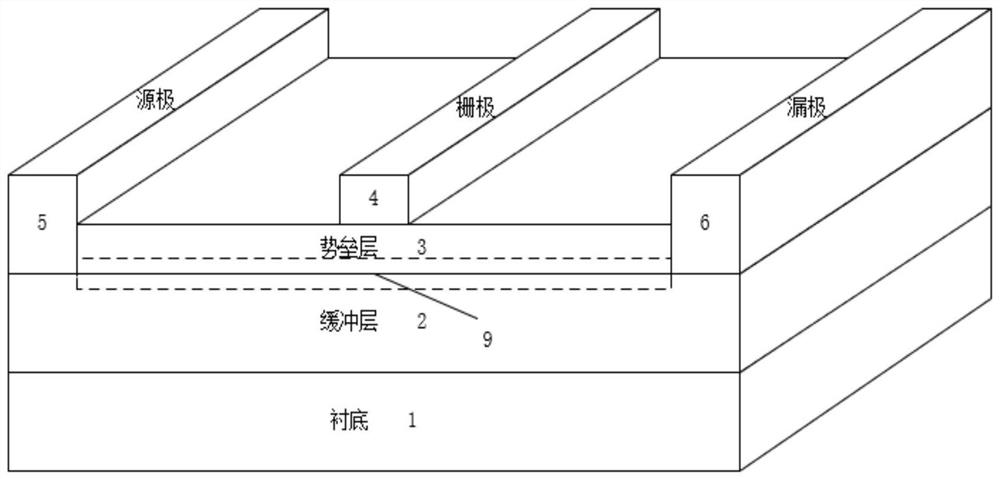

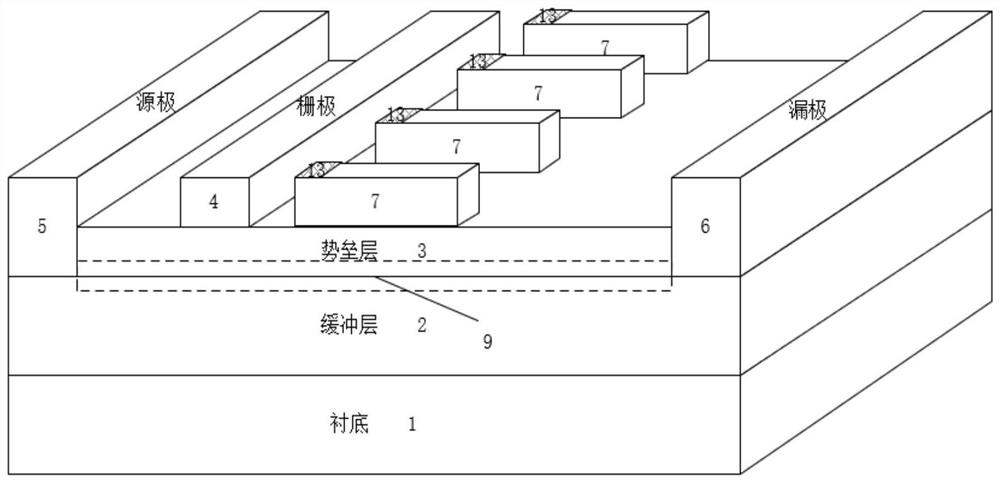

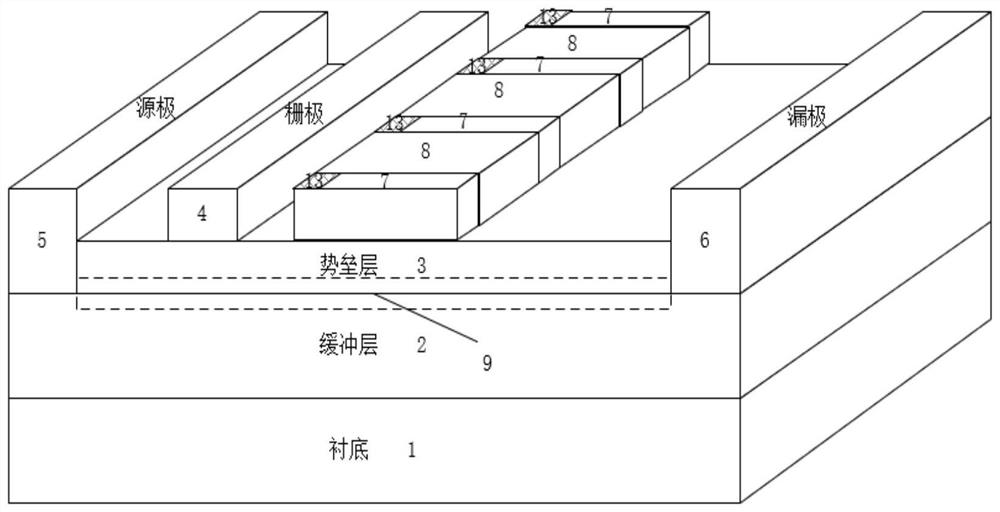

[0043] The present invention provides a p-channel HFET device with a comb finger-shaped n-type surface withstand voltage structure connected to the source, including a substrate 1, a buffer layer 2, a barrier layer 3, a gate 4, a source 5 and a drain electrode 6, a buffer layer 2 and a barrier layer 3 are sequentially arranged on the substrate 1, and a two-dimensional conductive channel 9 is formed at the interface between the barrier layer 3 and the buffer layer 2; the source electrode 5 and the drain electrode 6 are respectively arranged on the HFET device Both sides form an ohmic contact with the two-dimensional conductive channel 9; a gate 4 is arranged between the source 5 and the drain 6, and the gate 4 is located on the barrier layer 3 to form a Schottky contact with the barrier layer 3; The area between the gate 4 and the drain 6 on the barrier layer 3 is provided with a plurality of n-type semiconductor blocks 7 distributed in a finger shape, and each n-type semiconduc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More