SIFT algorithm hardware acceleration method based on DSP platform

An algorithm and platform technology, applied in the field of hardware acceleration of SIFT algorithm based on DSP platform, can solve the problem that the overall calculation speed of the DSP kernel algorithm has not made obvious breakthroughs, and the performance of the dual data channel of the DSP kernel hardware multiplier has not been fully utilized. Speed, convenient programming effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

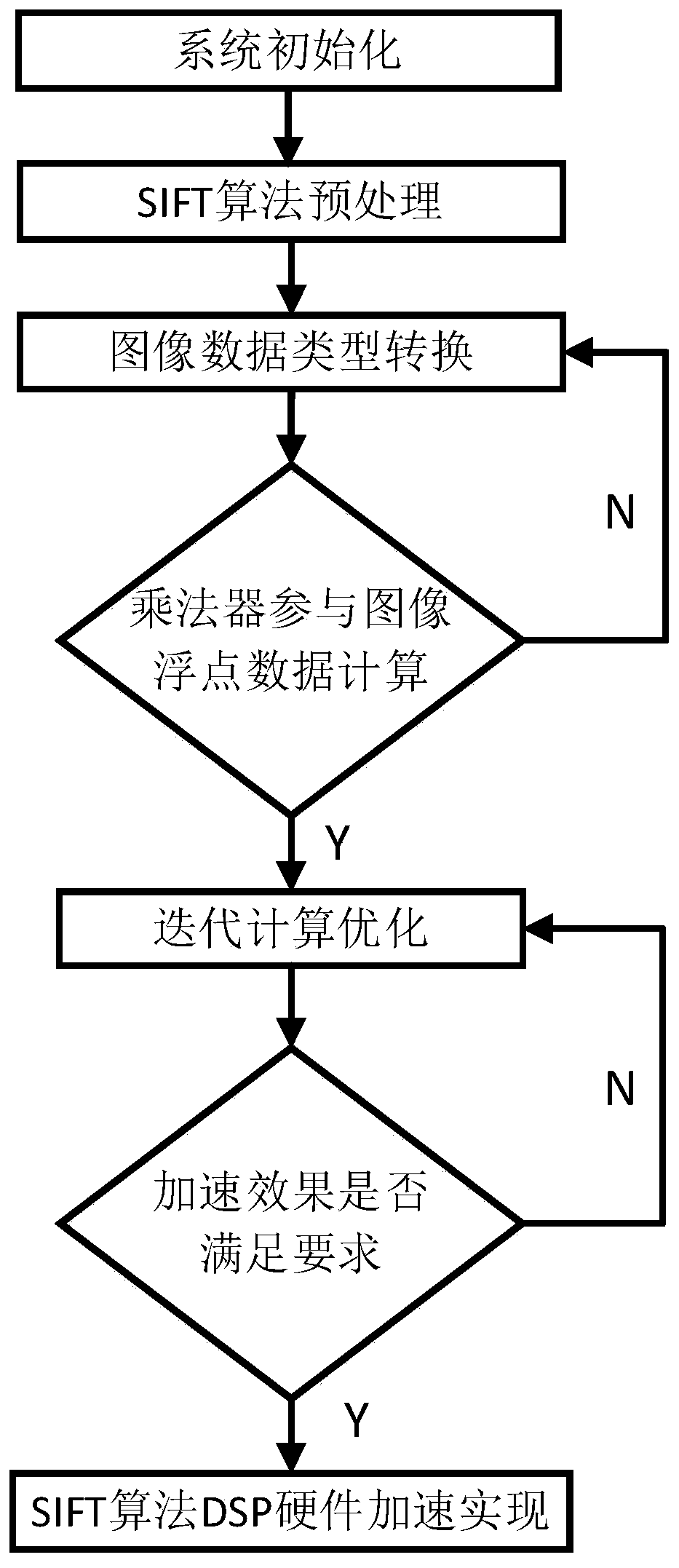

[0016] The DSP platform-based SIFT algorithm hardware acceleration method of the present invention comprises the following steps:

[0017] 1. After the system is initialized, recompile the algorithm into a C language program, so that the preprocessed algorithm program can run on the DSP platform, including the following steps:

[0018] 1) Constrain the interface functions in the SIFT algorithm running on non-DSP platforms.

[0019] 2) Recompile the library functions in the program after step 1) based on C language.

[0020] The SIFT algorithm of the non-DSP platform uses a large number of platform library functions, which are very inefficient to run on the DSP platform and occupy a lot of resources. Therefore, it is necessary to recompile the C language function library of the non-DSP platform.

[0021] 3) Calculation and restoration of the SSE acc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More