Semiconductor process method and semiconductor structure

A technology of semiconductor and process, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

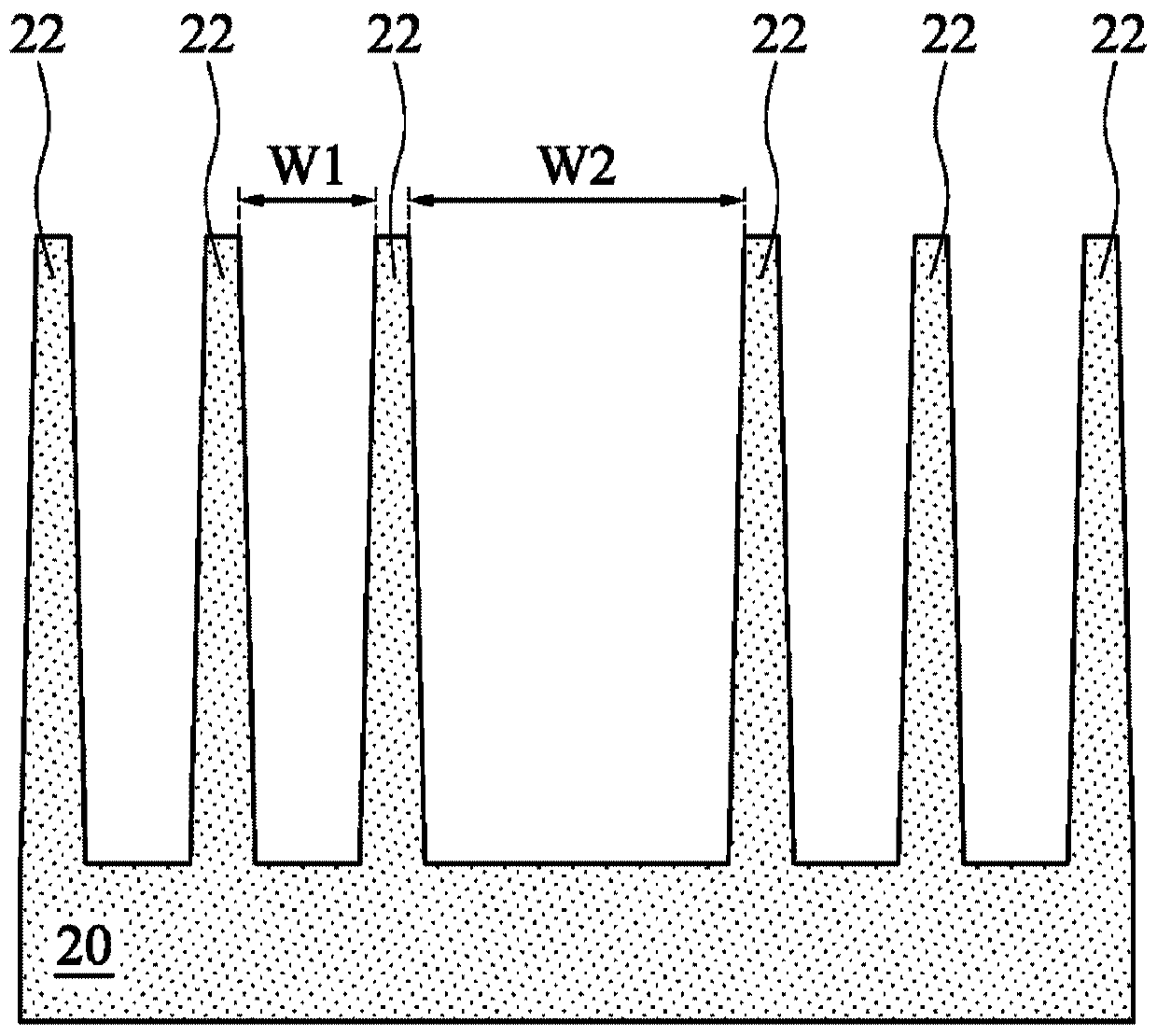

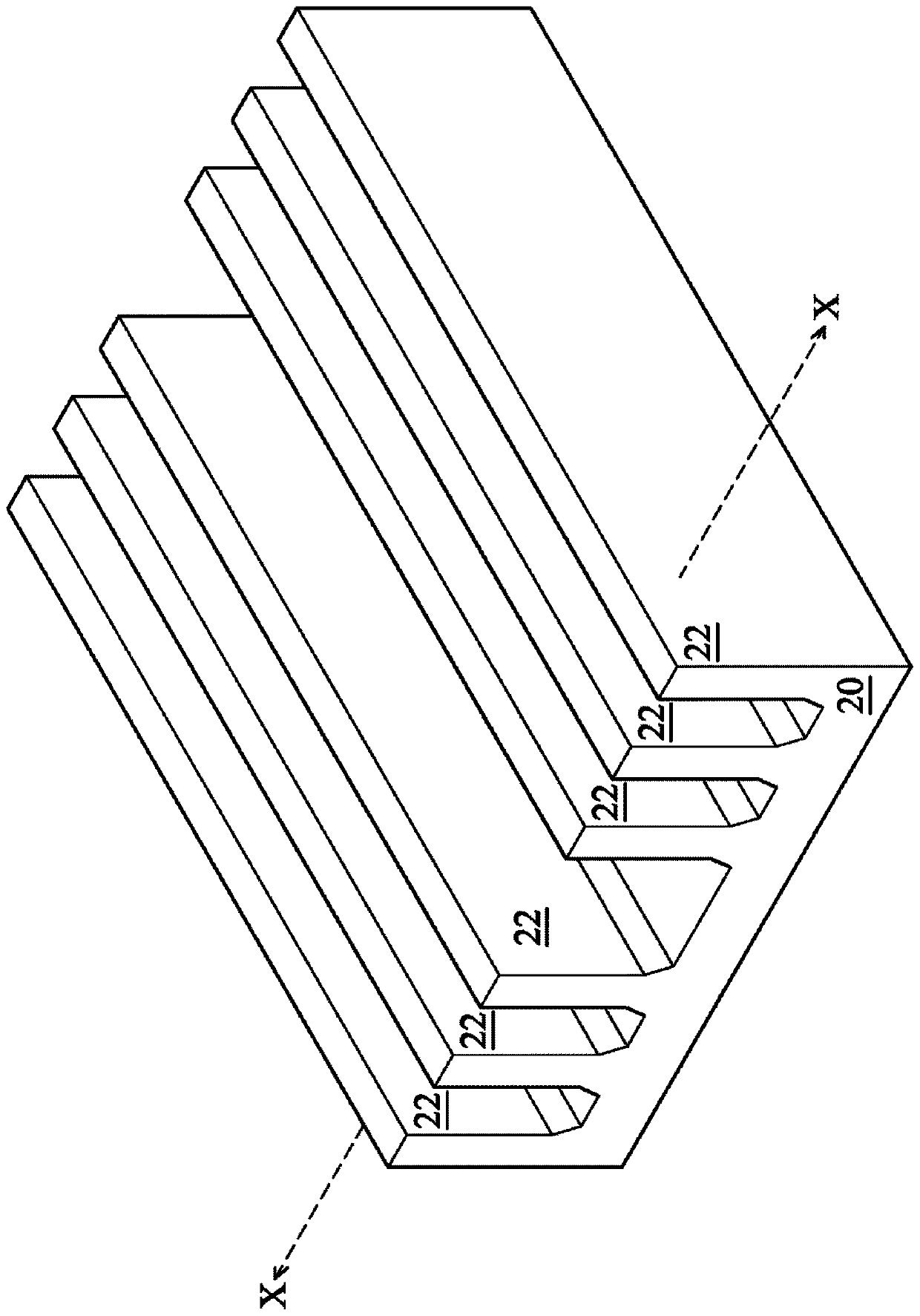

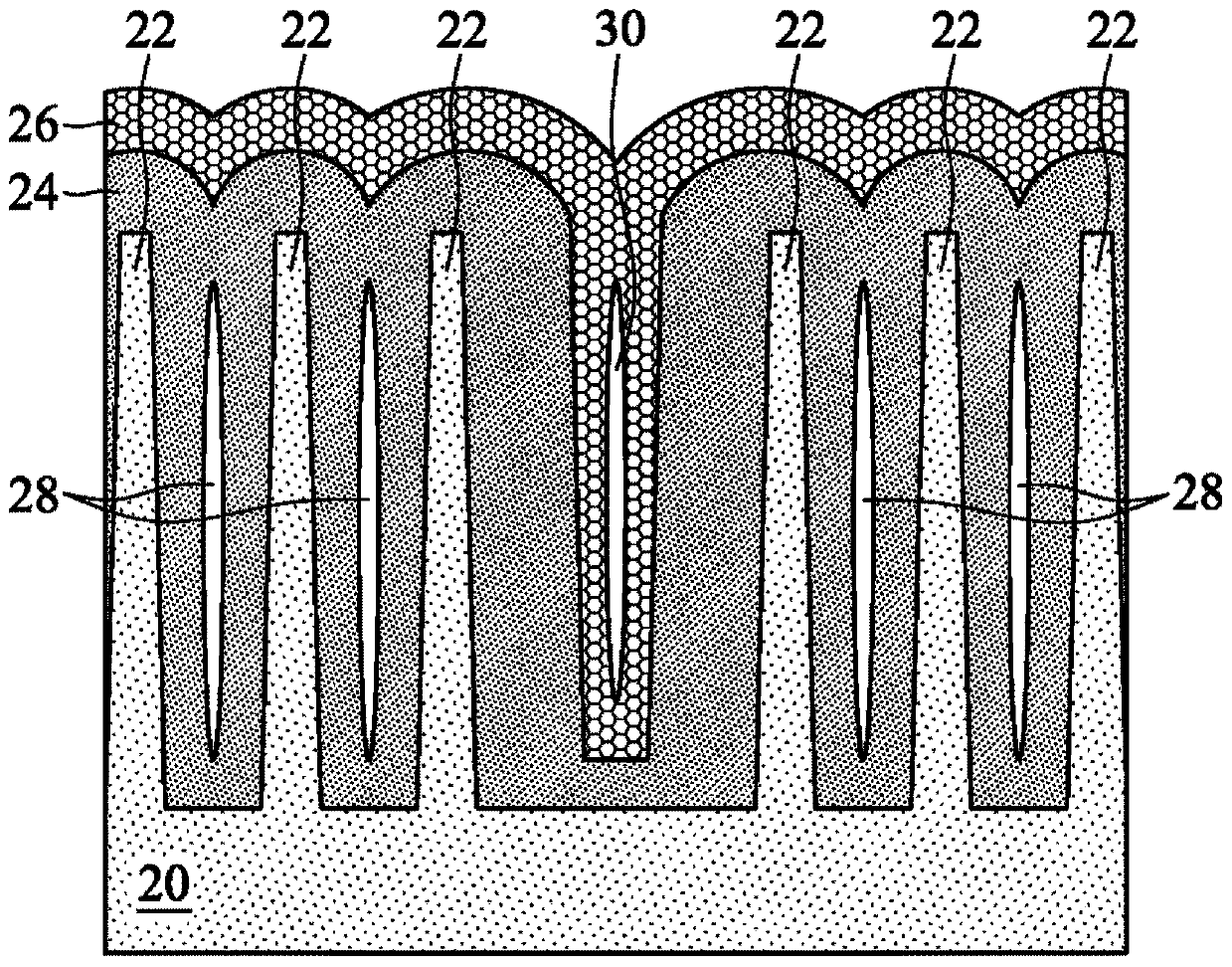

[0076] Example 1 is a method of semiconductor processing comprising conformally depositing a first dielectric material in a first trench in a substrate and in a second trench in the substrate, wherein the The merged lateral growth front of the first dielectric material in the first trench forms a seam in the first trench; treating the first dielectric material and the second trench in the first trench said first dielectric material in a trench, said first dielectric material in said first trench has a first upper surface, said first dielectric material in said second trench has a second upper surface, The treatment causes species to diffuse on the first upper surface and the second upper surface, in the seam, and into the first dielectric material in the first trench and into the in the first dielectric material in the second trench; and after the treating, etching the first dielectric material in the first trench and the first dielectric material in the second trench A diele...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com