Instruction correlation verification method and device, electronic equipment and storage medium

A technology of electronic equipment and verification methods, which is applied in the fields of electrical digital data processing, instrumentation, and calculation, and can solve the problems of low guidance value and insufficient knowledge of various situations of graphics processor instructions.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

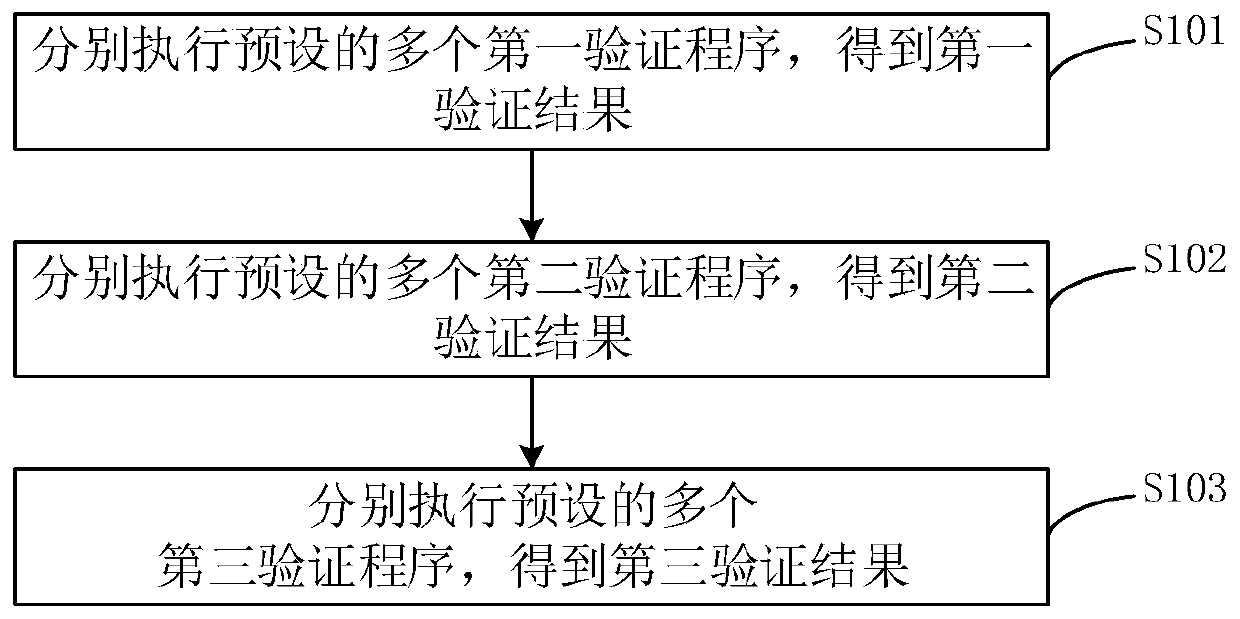

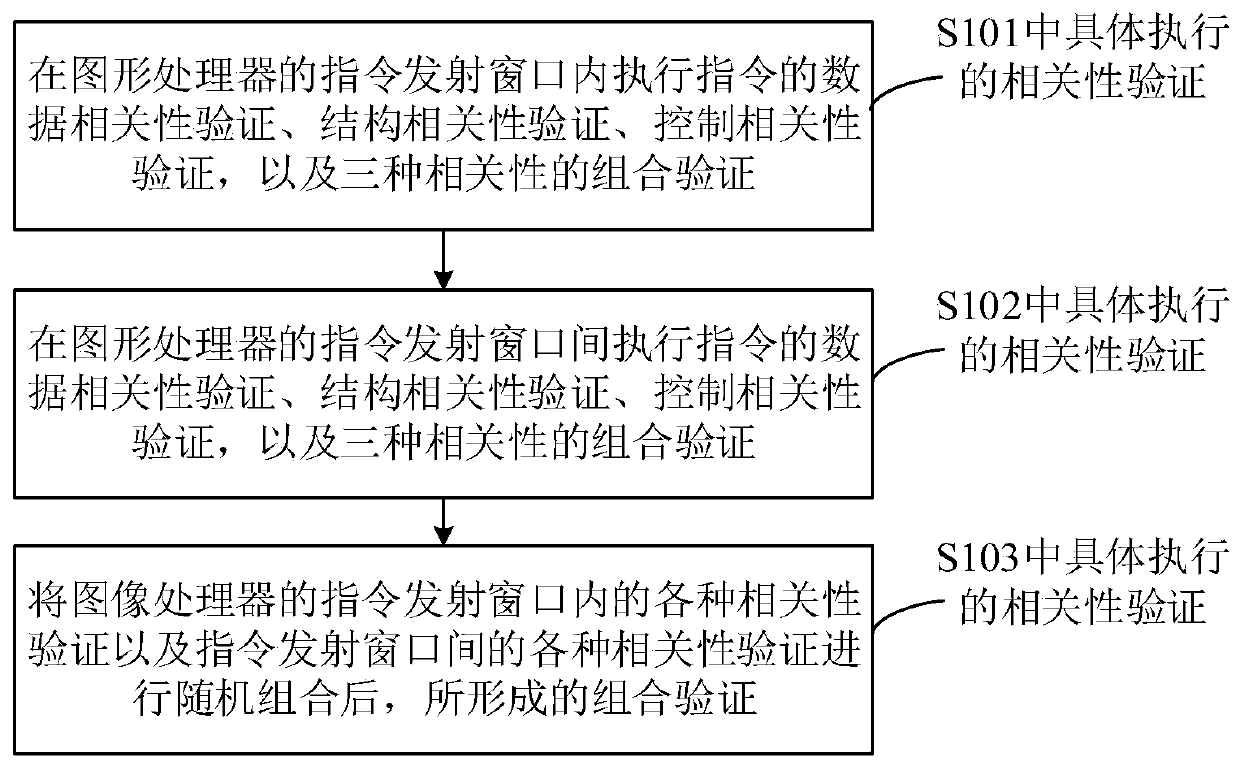

[0063] See figure 1 , figure 1 It is a schematic flowchart of a method for verifying the relevance of instructions provided by an embodiment of the present invention, and the method may include the following steps:

[0064] Step S101: Execute a plurality of preset first verification programs respectively to obtain a first verification result.

[0065] Wherein, any first verification program is composed of one or more stimulus test programs selected from a plurality of preset stimulus test programs; each stimulus test program includes a set of data-related, structure-related or control-related instructions, And the total number of instructions contained in the stimulus test program constituting any first verification program is not greater than the number of instruction issuance indicated by the size of the instruction issuance window of the graphics processor.

[0066] It can be understood that, for each first verification program, if the first verification program consists ...

Embodiment 2

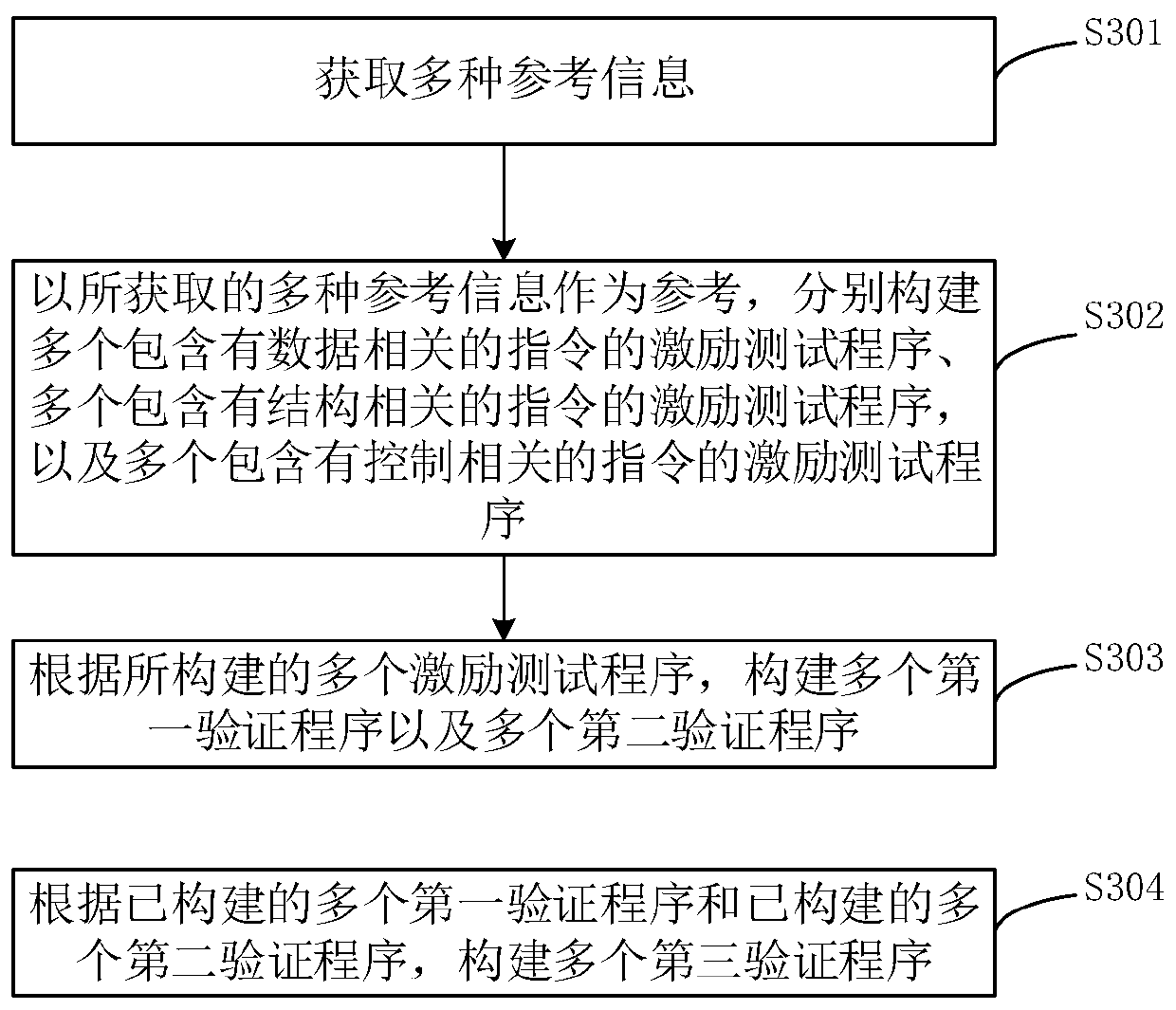

[0089] In order to clarify the scheme, the construction method of multiple preset first verification programs, multiple second verification programs, and multiple third verification programs will be exemplarily described below. like image 3 As shown, the construction method may include the following steps:

[0090] Step S301: Obtain various kinds of reference information.

[0091] Among them, the various reference information may include: the register read and write path of the graphics processor, the types of each instruction execution unit included in the graphics processor, the number of each type of instruction execution unit, and the processing pipeline of each type of instruction execution unit structure, the instruction execution cycle of each type of instruction execution unit, and the read and write operation types of each type of instruction execution unit read and write instructions.

[0092] In this step, there are many specific implementation manners for acquir...

Embodiment 3

[0142] Corresponding to the above instruction dependency verification method, an embodiment of the present invention also provides an instruction dependency verification device, such as Image 6 As shown, the device may include:

[0143] The first execution module 601 is configured to respectively execute a plurality of preset first verification programs to obtain a first verification result; wherein, any one of the first verification programs is selected from a plurality of preset stimulus test programs or a plurality of stimulus test programs; each of the stimulus test programs includes a set of data-related, structure-related or control-related instructions, and the total number of instructions contained in the stimulus test programs that constitute any first verification program is not The number of instruction issuances indicated by the size of the instruction issuance window greater than the graphics processor;

[0144] The second execution module 602 is configured to r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More