Digital chip function verifying method and system

A technology for digital chips and functional verification, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as low verification accuracy, achieve comprehensive verification, and improve accuracy and reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further specifically described below in conjunction with the accompanying drawings.

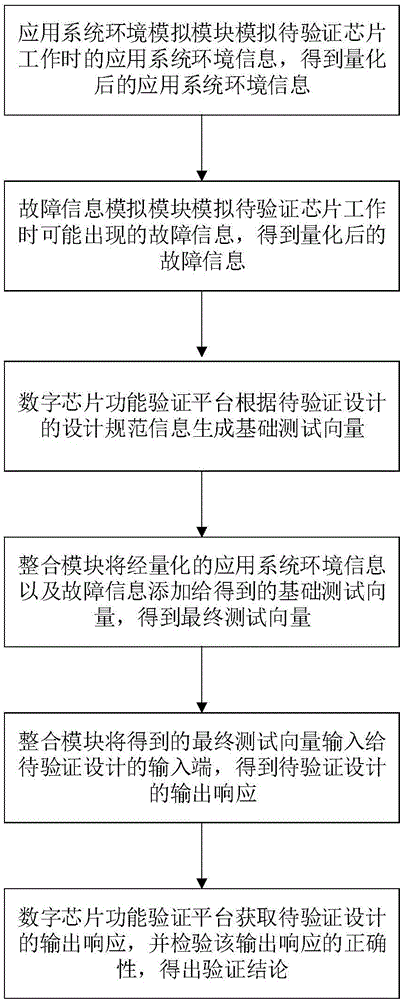

[0032] Refer to attached figure 1 :

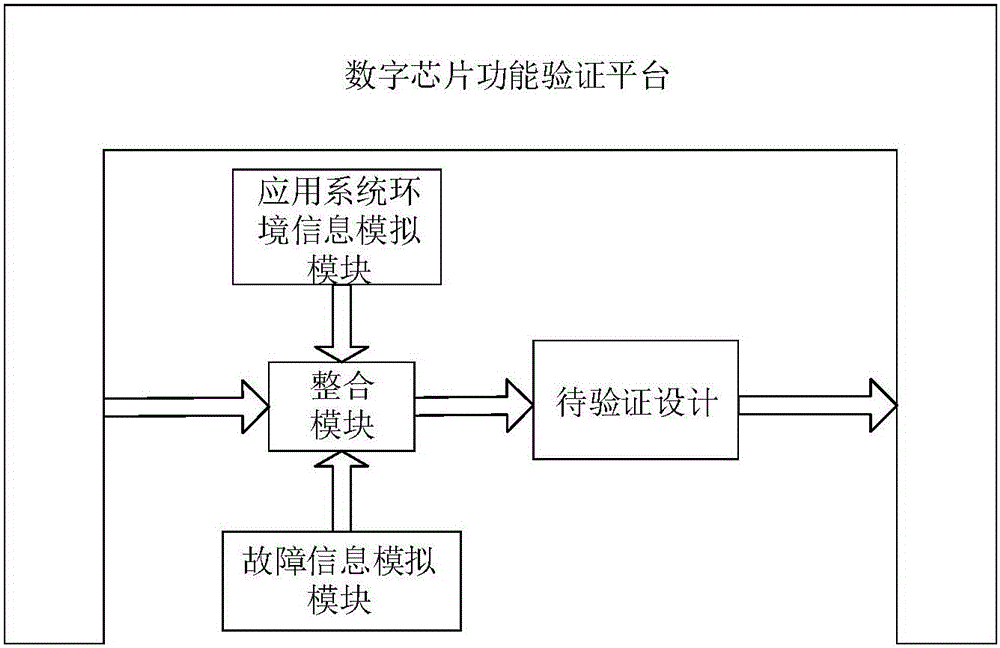

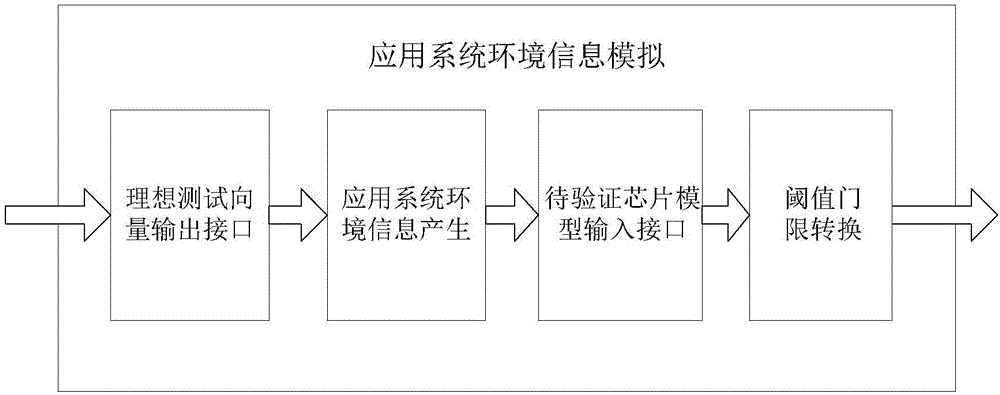

[0033] The digital chip function verification method of the present invention simulates its real system environment and the impact of fault information on the ideal stimulus received by the interface through certain methods and software simulations, and integrates the signal integrity problems brought about by the system environment information and fault information Into the basic test vector, so as to verify the correctness of timing and function of the design to be verified (DUV) with the test vector containing system environment information and fault information, the specific steps are as follows:

[0034] Step 1. The application system environment simulation module simulates the application system environment information when the chip to be verified works, and obtains the quantified application system environment ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More