A debugging system and method for on-chip crash

A debugging system, electric crash technology, applied in the field of integrated circuits, can solve problems such as difficult chip debugging, high manpower and time costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

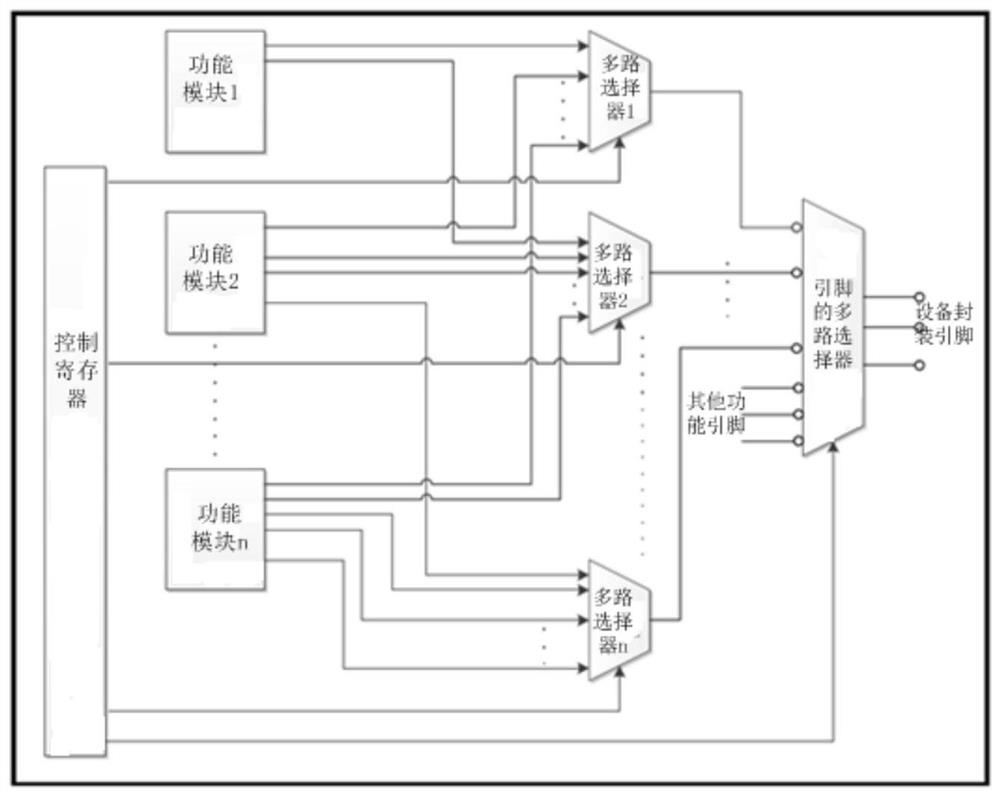

[0079] The debugging system of the on-chip electrical crash in the present invention is obviously different from the structure shown in FIG. 1, and it is not necessary to use a control

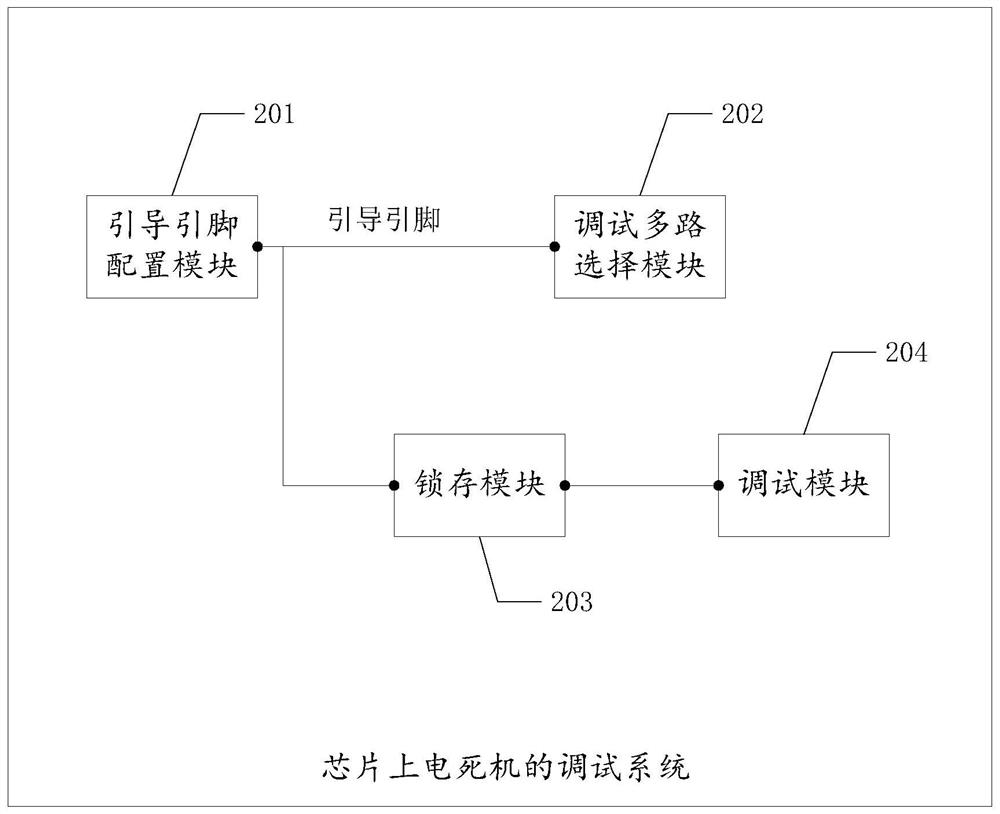

[0080] As shown in FIG. 2, an embodiment of the present invention provides a debugging system for an on-chip electrical crash, including:

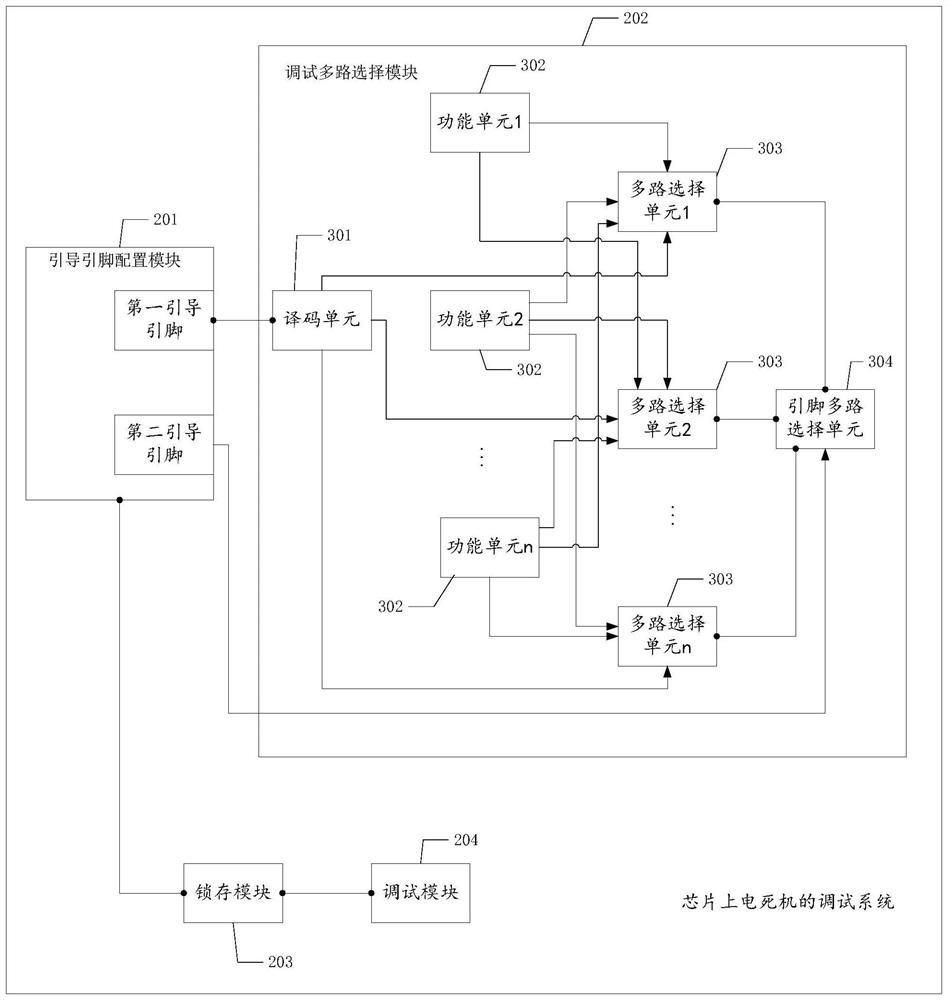

[0094] The multiplexing unit 303 is used to select the functional unit 302 according to the control signal;

[0097] Further, in conjunction with the embodiment shown in FIG. 3, as shown in FIG. 4, in some embodiments of the present invention, the debugging system

[0102] Further, in conjunction with the embodiment shown in FIG. 4, as shown in FIG. 5, in some embodiments of the present invention, the debugging system

[0107] The reset module 501 is also used to release the reset state when the chip is in the normal working mode.

[0109] Further, in conjunction with the embodiment shown in FIG. 5, as shown in FIG. 6, in some embodiments of the present inventi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More