Approximate multiplier design method, approximate multiplier and FIR filter

A multiplier and logic design technology, applied in the field of low-power digital signal processing circuit design, can solve problems such as the inability to ensure the calculation accuracy of the approximate compressor and the number of resources occupied, and the modification of calculation logic without theoretical basis and error constraints, etc., to achieve The effect of ensuring calculation accuracy and resource utilization efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the purpose, technical solution and advantages of the present application clearer, the present application will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present application, and are not intended to limit the present application.

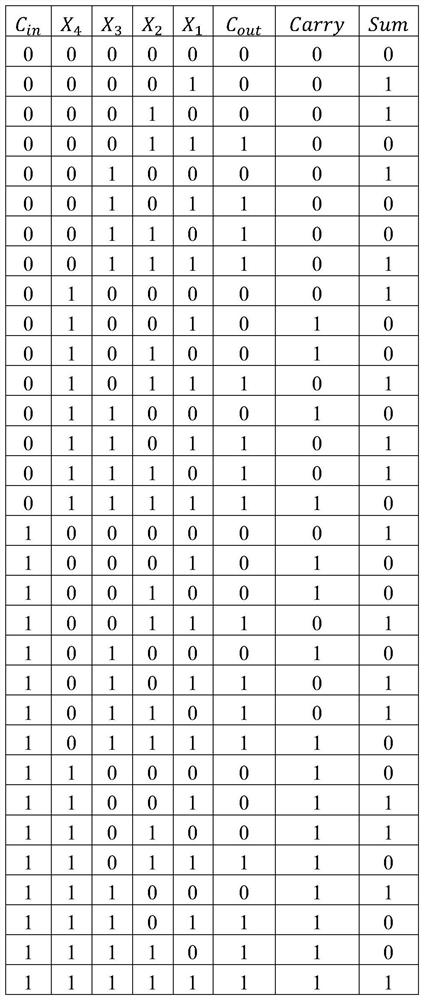

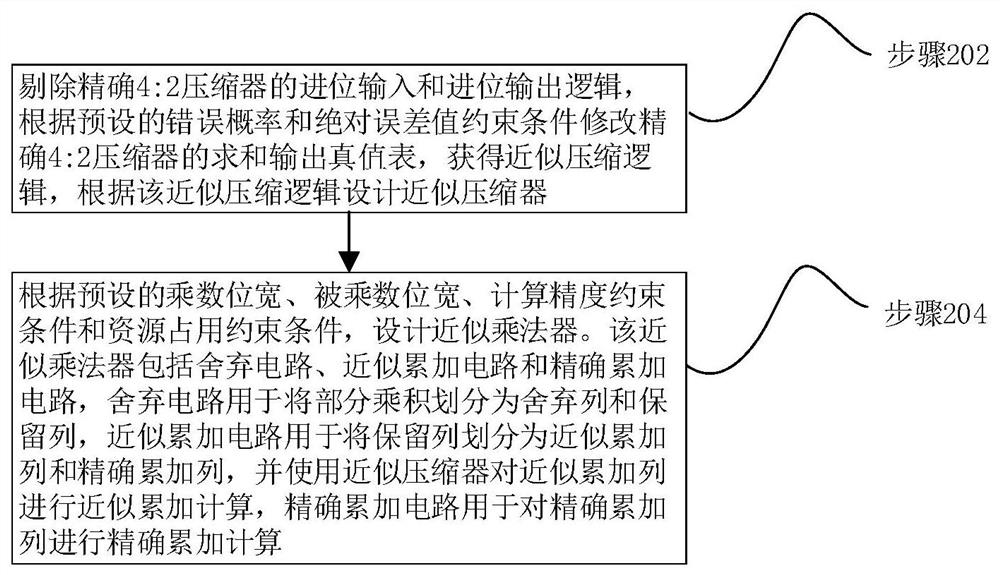

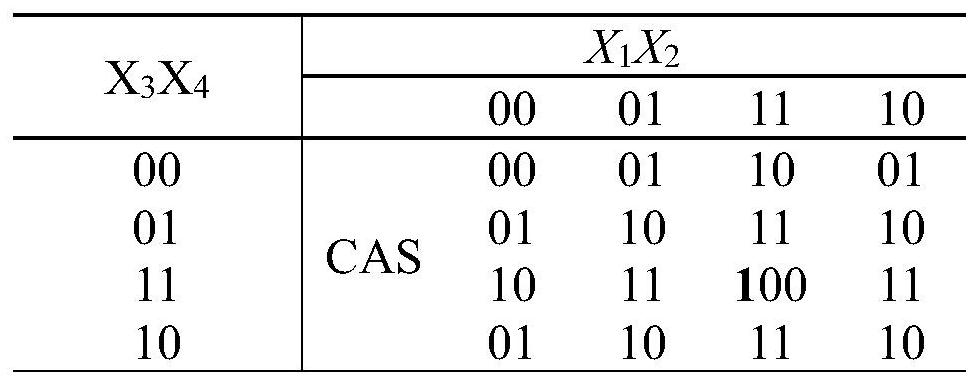

[0040] A commonly used accurate 4:2 compressor in the prior art is implemented by cascading two accurate full adders, the inputs of which include four marked X 1 ~X 4 a partial product input and a carry input (C in ), whose output includes a carry out (C out ), a false output (Carry) signal and a summation signal (Sum), the truth table of which is as follows figure 1shown. Among them, the carry input is connected to the carry output of other circuits, and the carry output is connected to the carry input of other circuits, that is, the precise 4:2 compressor needs to wa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More