Digital channel group delay equalizer and implementation method and device thereof

A technology of delay equalization and implementation method, applied in the field of communication, can solve the problems of difficult engineering use, difficult design and debugging, and low clock rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

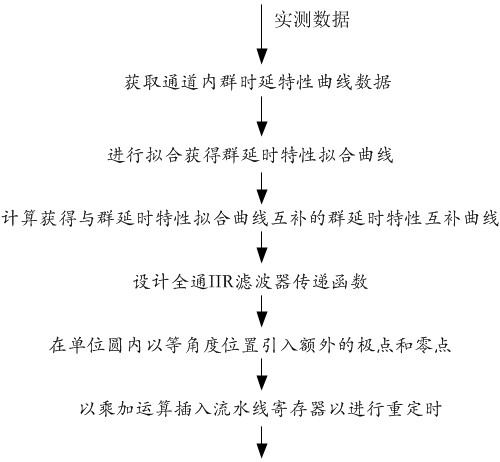

[0047] Such as figure 1 As shown in FIG. 1 , it is a flow chart of the implementation method of the digital channel group delay equalizer provided in this example.

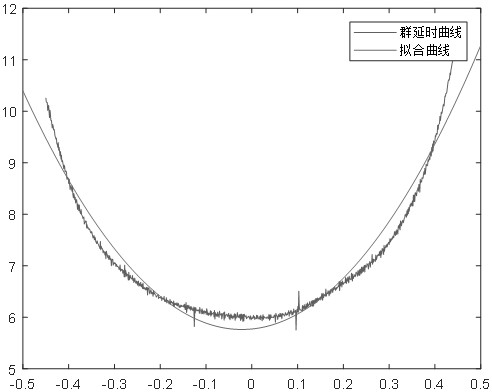

[0048] Step 1: Use the instrument to accurately measure the group delay characteristic curve in the upper passband of the channel, such as figure 2 Shown is the group delay characteristic curve of the channel in a certain passband. Generally, the group delay in the middle of the effective transmission frequency band is small, and the edge is large, showing a characteristic of an approximate quadratic curve. The least square fitting method is used for this The curve fitting calculation result of the measurement results is the estimated value of the coefficient of the curve, and the estimated coefficient of the curve obtained by the least square method minimizes the sum of the squares of the residual error.

[0049] In the example, quadratic fitting is used, and high-order curve fitting can be performed as needed ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More