Chip failure positioning method and clamp

A failure location, chip technology, applied in the direction of electronic circuit testing, measuring devices, instruments, etc., can solve the problems of increasing position deviation, failing to power on the chip, destroying the chip structure layer, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

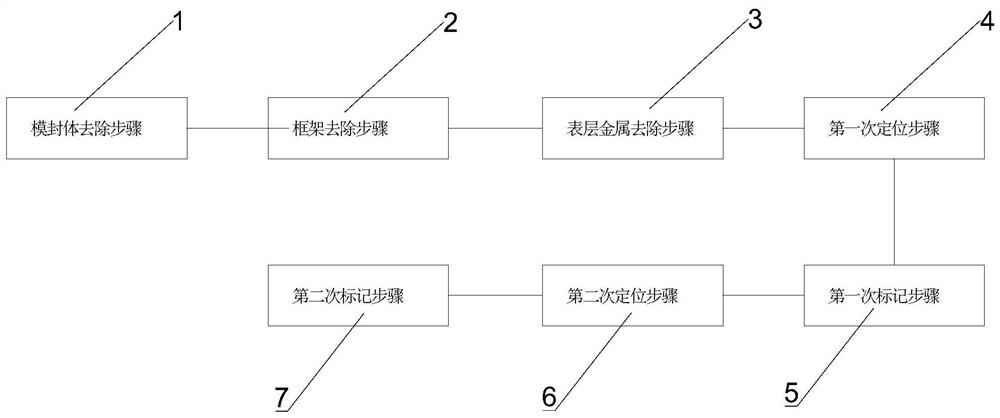

[0066] Such as figure 1 , Figure 8 and Figure 10 As shown, in the transfer step, the side of the chip body 10 facing the lens of the low-light microscope is the front side 101, and the front side 101 of the chip is marked by the imaging marking device, that is, the method for marking the front side 101 of the chip. The specific steps are as follows:

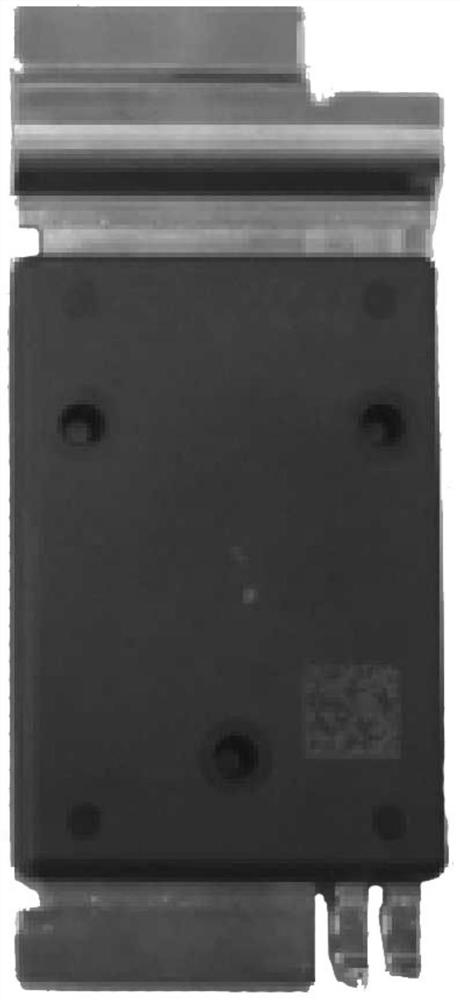

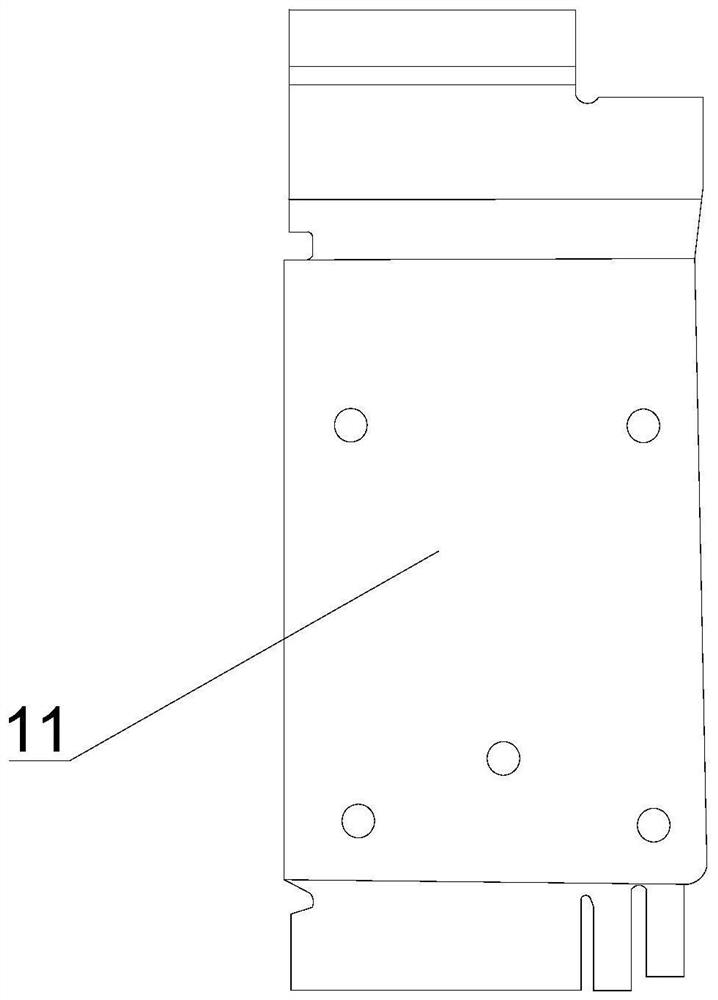

[0067] The removal step includes the mold seal body removal step 1 and the metal layer removal step. In the mold seal body removal step 1, a mixed solution of concentrated nitric acid and concentrated sulfuric acid is used to remove the mold seal body 11 on the surface of the chip body 10. After the mold seal body is removed, the product is as follows: Figure 4 and Figure 5 shown. In the above-mentioned steps, the concentration of concentrated nitric acid is 98%, the concentration of concentrated sulfuric acid is 95%, and the mixing ratio of concentrated nitric acid and concentrated sulfuric acid is 5:1, certainly, the con...

Embodiment 2

[0076] Such as figure 1 , Figure 9 and Figure 10 As shown, in this solution, the side of the chip body 10 facing the lens of the low-light microscope is the back side 102, and the back side 102 of the chip is marked by the imaging marking device, that is, the method for marking the back side 102 of the chip. The specific steps are as follows:

[0077] Removal step: remove the protective layer on the surface of the semiconductor device, such as metal layer, molded body and ceramic layer, etc., the removal method is selected according to the different materials to be removed, such as grinding, chemical corrosion or laser unsealing, etc., which are not included in this application There is no limit, just thin the back of the chip to 150-200um. The processed chip will be transported to the imaging marking device for imaging marking processing, the specific steps are as follows:

[0078] The first positioning step 4: power on the chip body 10 under the low-magnification lens o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More