Adaptive SGPIO decoder achieved through logic chip and program

A logic chip and self-adaptive technology, applied in the field of signal decoding, can solve the problem of consuming logic resources and achieve the effect of simplifying PCB lines and reducing occupation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

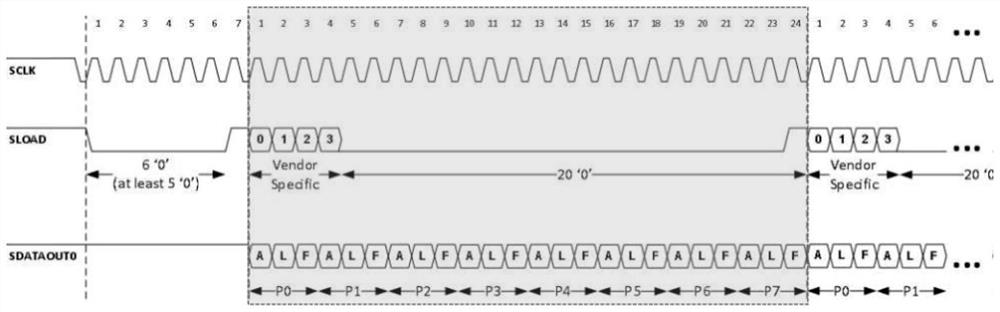

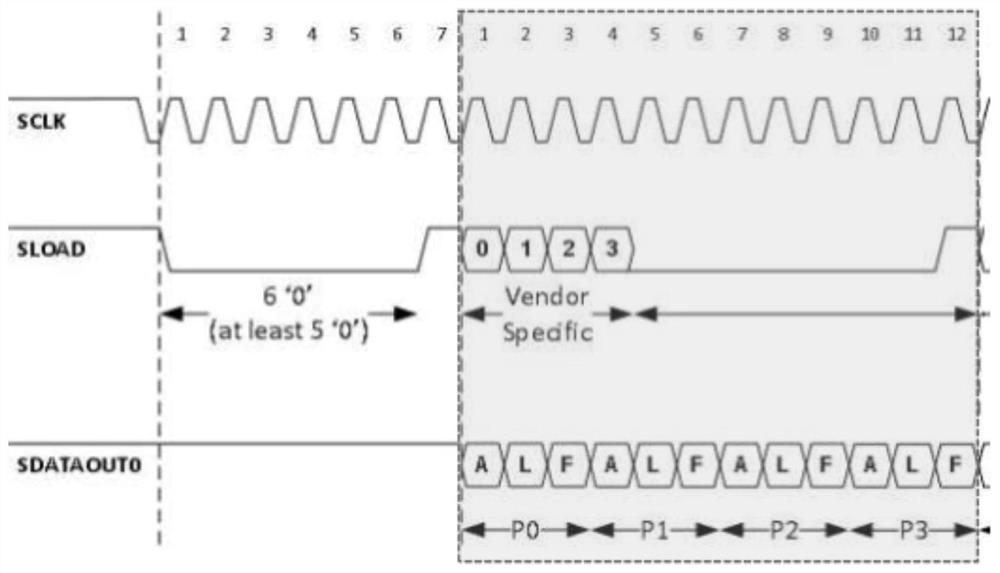

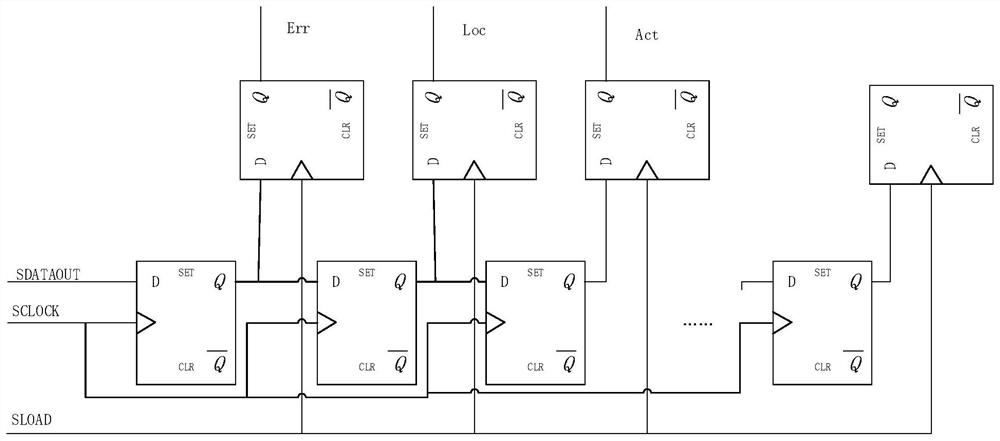

[0036] The present invention is described below in conjunction with accompanying drawing, wherein, figure 1 It is a schematic diagram of the SGPIO signal transmitted by the South Bridge chip; figure 2 It is a schematic diagram of the SGPIO signal transmitted by the RAID card; image 3 It is a schematic diagram of the SGPIO decoding circuit; Figure 4 It is a schematic diagram of an adaptive SGPIO decoder implemented by a logic chip in an embodiment of the present invention; Figure 5 is a schematic diagram of the architecture of the logic chip in the embodiment of the present invention; Image 6 It is a schematic diagram of the position of the detection mark detected by the detection and counting module in the SGPIO signal in the embodiment of the present invention; Figure 7 It is a flowchart of counting and ana...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More