Delay line structure and delay jitter correction method thereof

A technology of delay jitter and delay line, which is applied in the direction of automatic power control, logic circuit with logic function, receiver monitoring, etc., to achieve the effect of reducing delay jitter

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

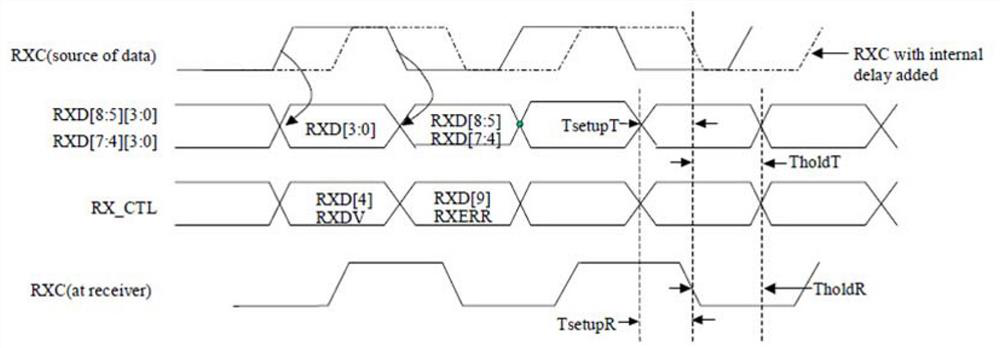

Problems solved by technology

Method used

Image

Examples

Embodiment

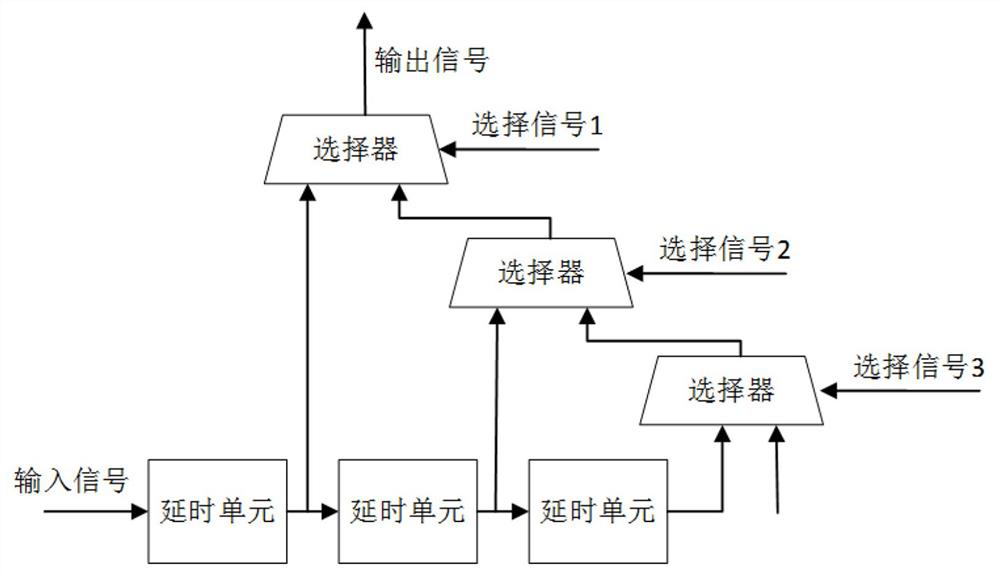

[0029] see figure 2 As shown, the present invention relates to a delay line structure, which is implemented based on a selector, specifically, includes N delay units and N selectors, wherein the output of the N-1th delay unit The terminals are respectively connected to the first input end of the N-1th selector and the input end of the Nth delay unit, the N-1th selector inputs the N-1th selection signal, and the Nth delay unit The output end is connected to the first input end of the Nth selector, the output end of the Nth selector is connected to the second input end of the N-1th selector, and the Nth selector inputs the Nth selection signal, The delay units and the selectors are stacked forward according to the above rules, until the input end of the first delay unit is connected to the input signal and the output end of the first selector is connected to the output signal.

[0030] Assuming that the delay of the combination of a delay unit and the selector in the above del...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More