Semiconductor structure and forming method thereof

A semiconductor and isolation structure technology, applied in the field of semiconductor structure and its formation, can solve the problems of difficult channel and poor channel control ability of the gate structure, and achieve high uniformity, high consistency, optimized The effect of electrical properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] Currently formed devices still suffer from poor performance. The reasons for the poor performance of the device are analyzed in conjunction with a method of forming a semiconductor structure.

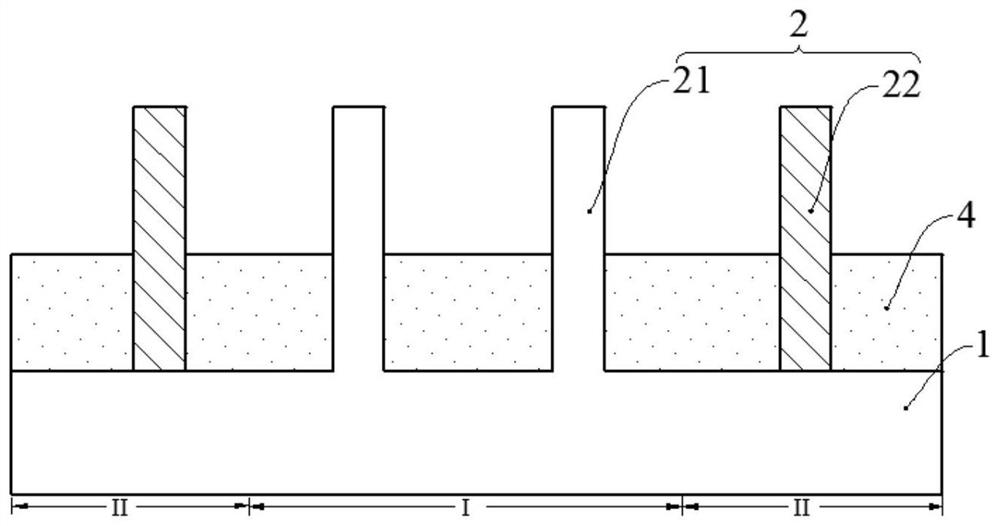

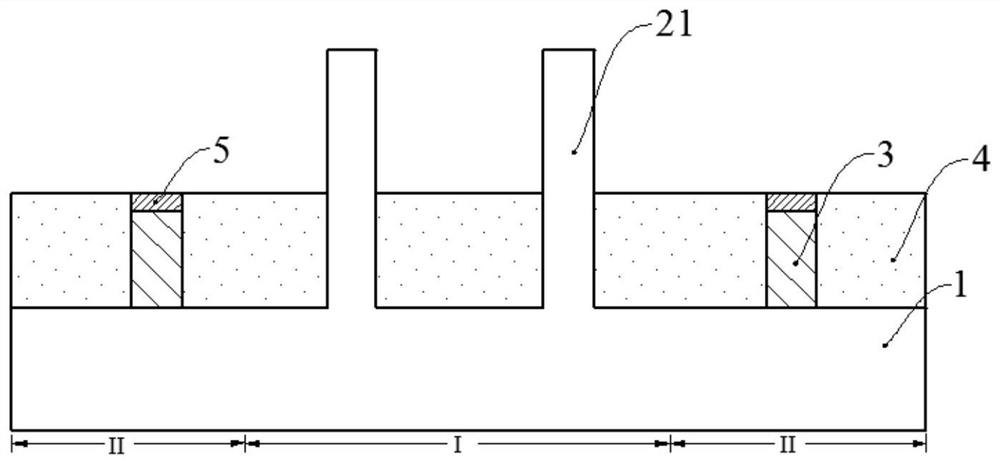

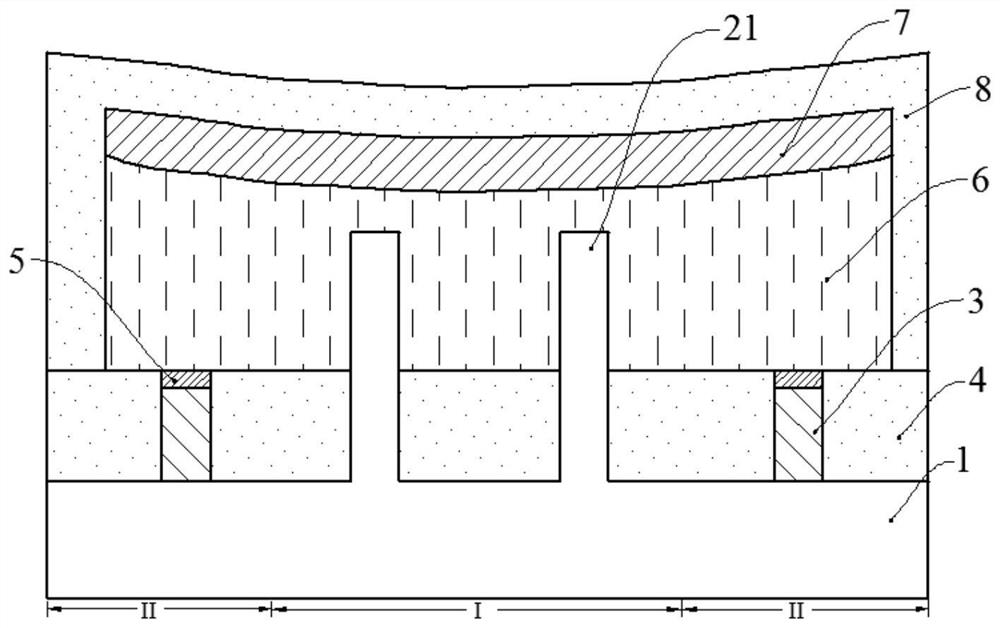

[0013] Figure 1 to Figure 5 It is a structural schematic diagram corresponding to each step in a method for forming a semiconductor structure.

[0014] Such as figure 1 As shown, a base is provided, the base includes a substrate 1 and fins 2 located on the substrate 1; the base includes an isolation region II and a device region I, and the fins located in the device region I 2 is a device fin 21 , and the fin 2 located in the isolation region II is a dummy fin 22 ; an isolation layer 4 is formed on the fin 2 exposing the substrate 1 .

[0015] Such as figure 2 As shown, the dummy fin portion 22 on the isolation region 1 is etched to form the remaining dummy fin portion 3, the top of the remaining dummy fin portion 3 is lower than the top surface of the isolation layer 4, an...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More