Formation method of semiconductor structure

A technology of semiconductor and gate structure, applied in the field of semiconductor structure formation, can solve the problems of poor isolation performance, affecting the performance of semiconductor structure, etc., to achieve the effect of improving performance, avoiding short circuit of gate structure, and flattening the interface

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] As described in the background art, the isolation performance of the dielectric layer formed in the prior art deteriorates, thereby affecting the performance of the semiconductor structure. The following will be described in detail with reference to the accompanying drawings.

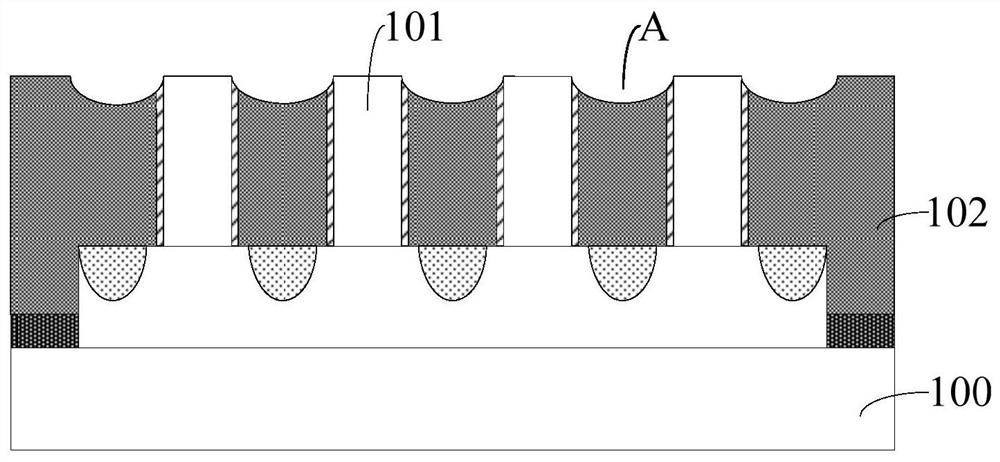

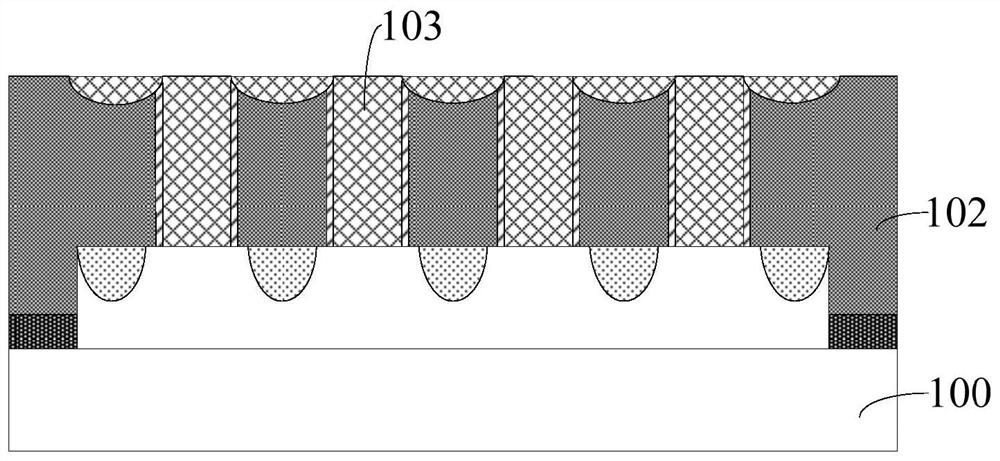

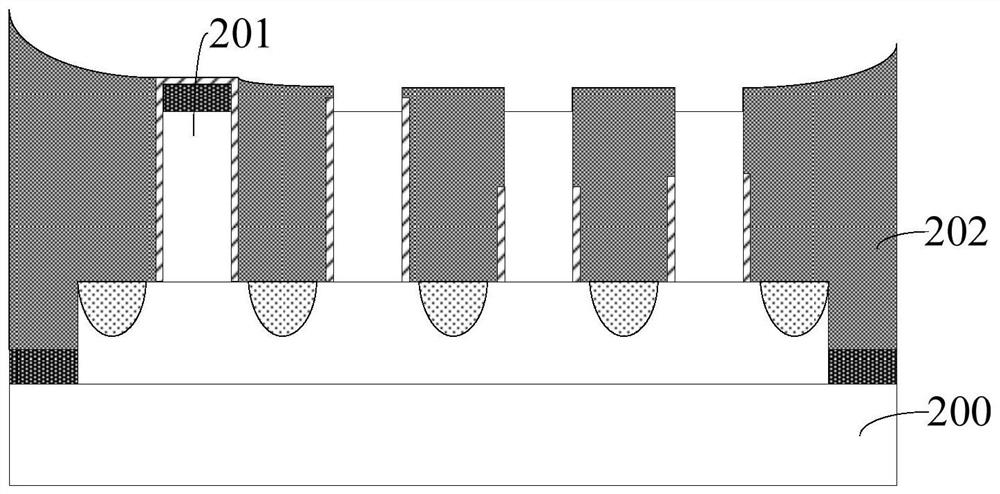

[0032] Figure 1 to Figure 2 It is a schematic structural diagram of each step of a method for forming a semiconductor structure.

[0033] Please refer to figure 1 , a substrate 100 is provided, the substrate 100 has a plurality of mutually discrete dummy gate structures 101, the dummy gate structures 101 include a dummy gate layer, a mask layer located on the dummy gate layer, and a mask layer located on the dummy gate layer. film layer and spacers (not shown) on the sidewalls of the dummy gate layer; forming an initial dielectric layer (not shown) on the substrate 100 and the dummy gate structure 101; planarizing the initial dielectric layer , until the top surface of the dummy gate layer is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More