Method for assisting waveform debug in chip verification and application

An auxiliary waveform and chip technology, applied in the field of chip development, can solve problems such as difficult verification personnel, time consumption of verification personnel, and reduced debugging efficiency, so as to achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

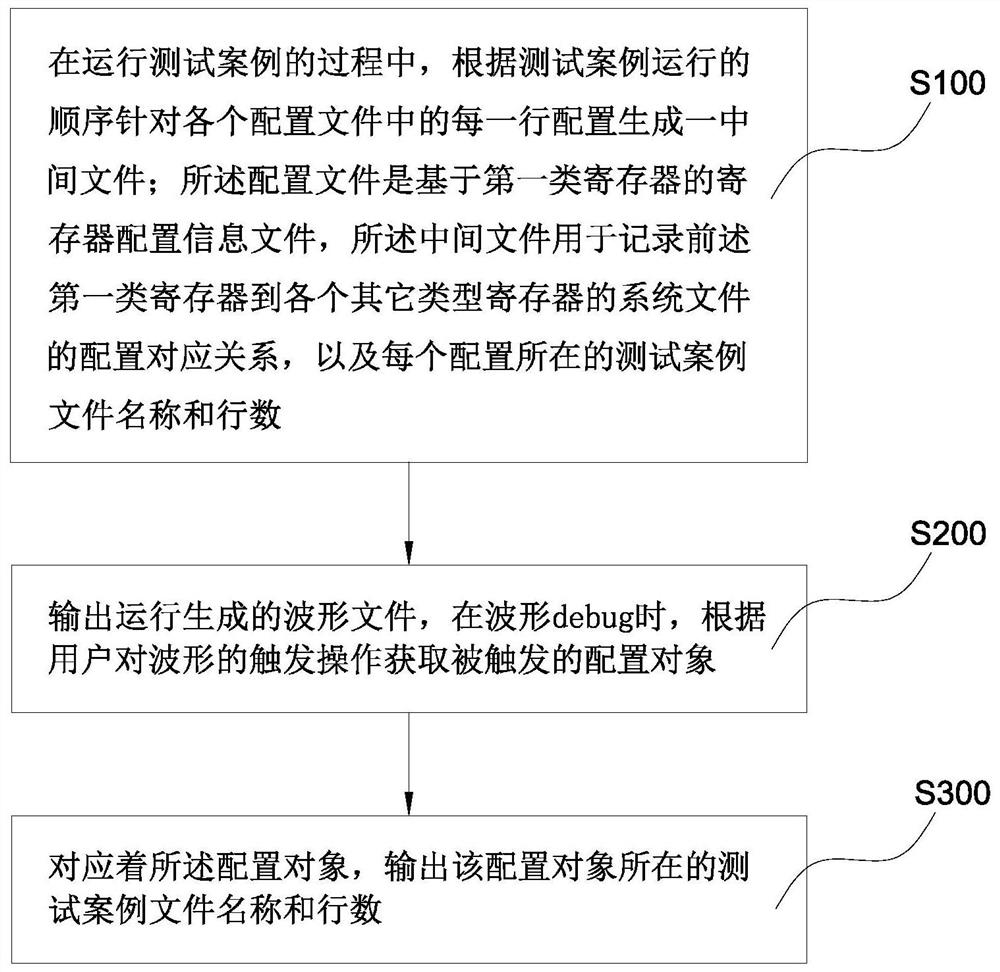

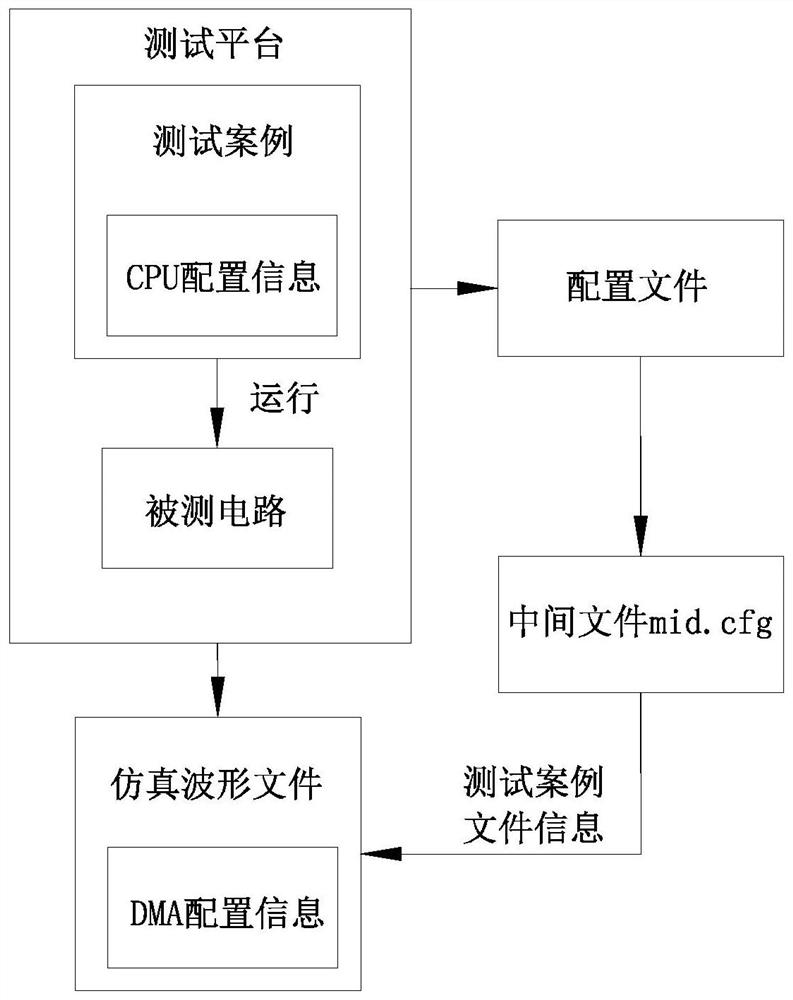

[0038] see figure 1 and figure 2 As shown, a method for auxiliary waveform debugging (error detection, or error debugging) in a chip verification provided by the present invention, the method includes the following steps:

[0039]S100, in the process of running the test case, generate an intermediate file for each line configuration in each configuration file according to the order of test case (case test) operation; the configuration file is a register configuration information file based on the first type of register, The intermediate file is used to record the configuration correspondence between the aforementioned first-type registers and system files of other types of registers, as well as the test case file name and line number where each configuration is located.

[0040] see figure 2 As shown, in the test platform, a test case (case test) is run through the circuit under test for simulation, and a simulation waveform file is generated. During the running of the te...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More