I2C link management system and method

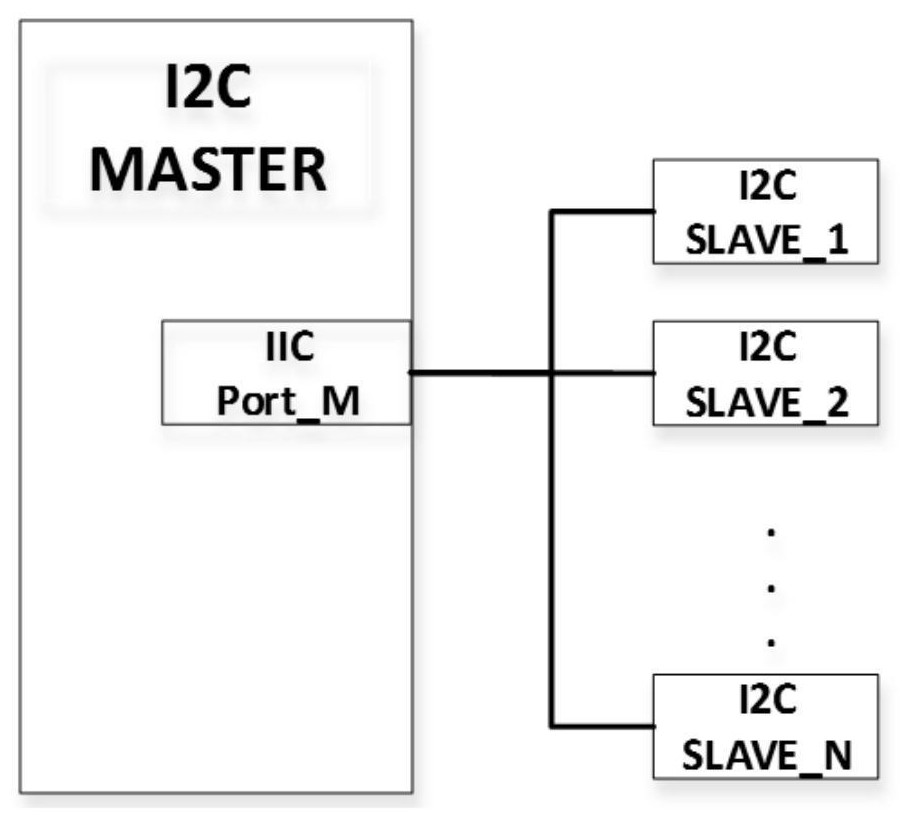

A link management and link technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of low I2C management efficiency and poor stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

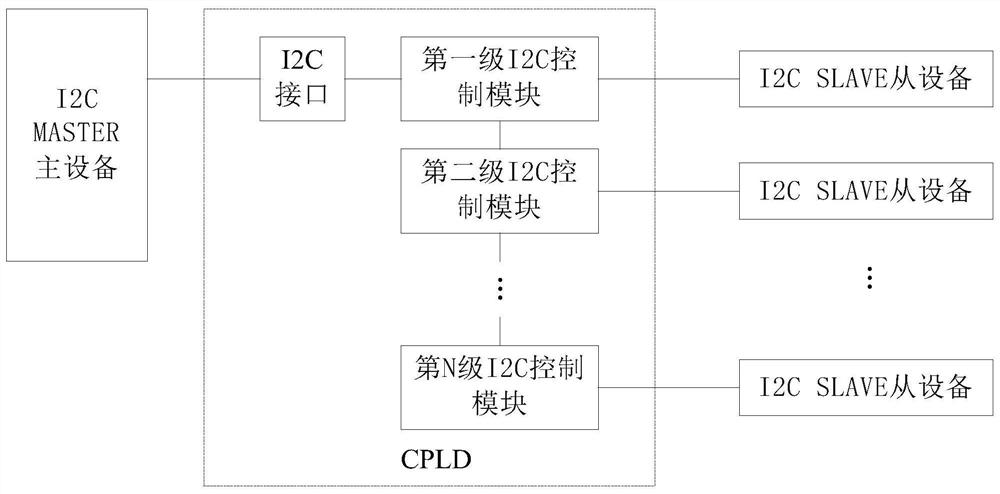

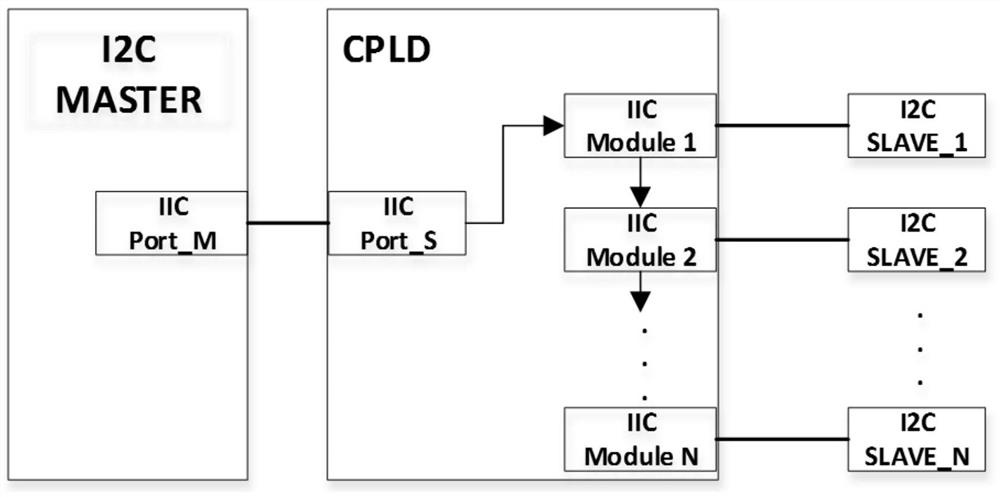

[0056] see figure 2 , figure 2 It is a schematic structural diagram of an I2C link management system provided by the embodiment of the present application. Depend on figure 2 It can be seen that the I2C link management system in this embodiment mainly includes: one I2C MASTER master device, multiple I2C SLAVE slave devices, and a CPLD is set between the I2C MASTER master device and the multiple I2C SLAVE slave devices. The CPLD of this embodiment includes: an I2C interface and a plurality of I2C control modules, which are sequentially connected in series, and any I2C control module is connected to an I2C SLAVE slave device, and one end of the I2C interface is connected to the I2C MASTER master device The control end of the I2C interface is connected to the first-level I2C control module among the plurality of I2C control modules. That is, in multiple I2C control modules, except for the first-level I2C control module, the output terminal of the previous I2C control module...

Embodiment 2

[0070] exist Figure 2-Figure 5 On the basis of the illustrated embodiment see Figure 6 , Figure 6 It is a schematic flowchart of an I2C link management method provided by the embodiment of the present application. The I2C link management method in this embodiment is mainly applied to the above-mentioned I2C link management system. Depend on Figure 6 It can be seen that the I2C link management method in this embodiment mainly includes the following processes:

[0071] S1: Continuously collect the I2C_SDA_IN signal of any I2C control module. Among them, the I2C_SDA_IN signal is the input data signal.

[0072] S2: Determine whether the I2C_SDA_IN signal is low level.

[0073] If the I2C_SDA_IN signal is low, the Figure 6 It can be seen that step S3 is further executed: judging whether the time for which the I2C_SDA_IN signal remains at a low level is ≥ a set time.

[0074] If the time for which the I2C_SDA_IN signal remains at a low level ≥ the set time, execute step...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More