Multi-thread comprehensive method and device

A synthesis method and multi-thread technology, applied in the FPGA field, can solve problems such as long running time and affecting the execution efficiency of FPGA synthesis tools

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

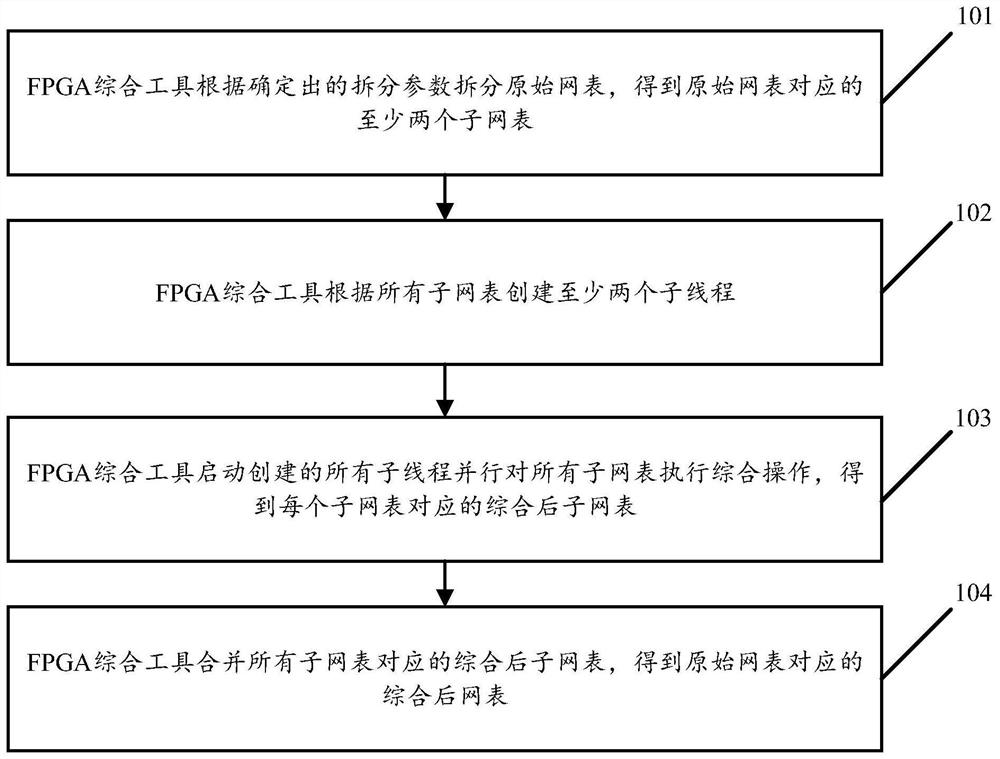

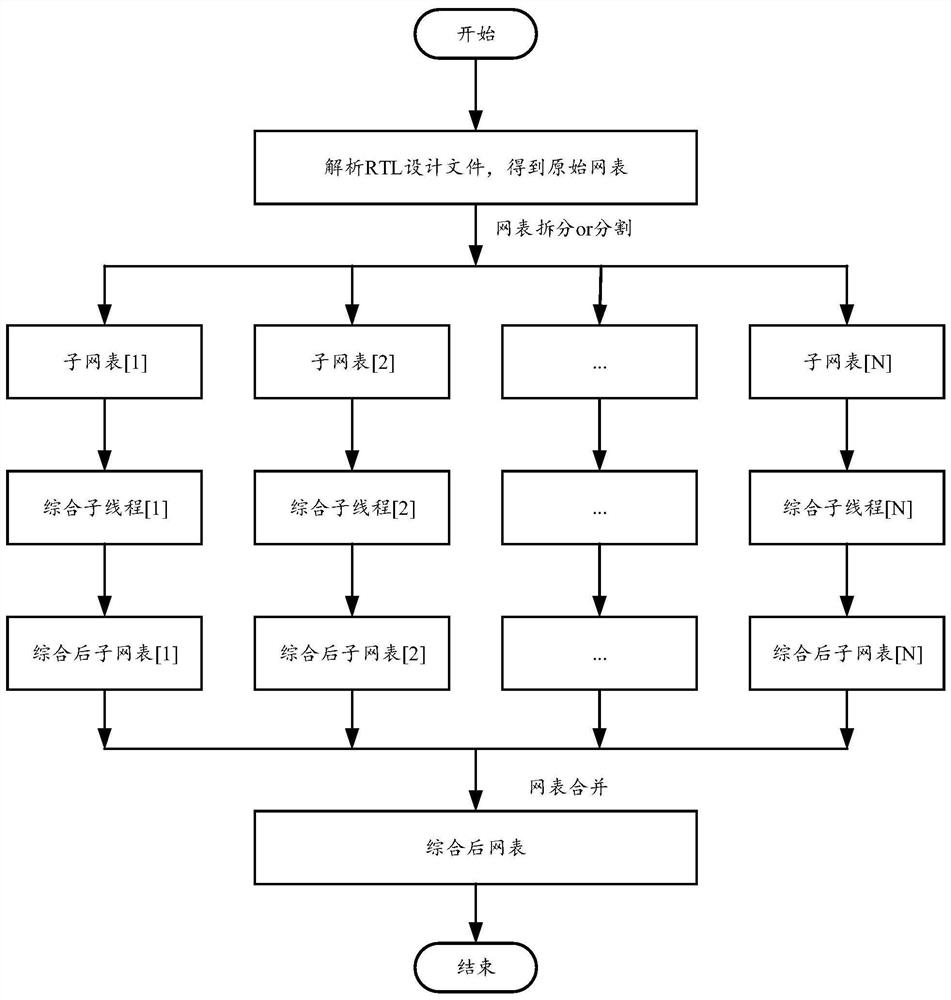

[0097] see figure 1 , figure 1 It is a schematic flowchart of a multi-thread synthesis method disclosed in an embodiment of the present invention. in, figure 1 The described method can be applied to an FPGA synthesis tool, which is not limited in the embodiment of the present invention. Such as figure 1 As shown, the method may include the following operations:

[0098] 101. The FPGA synthesis tool splits the original netlist according to the determined split parameters to obtain at least two subnetlists corresponding to the original netlist.

[0099] In the embodiment of the present invention, the original netlist is obtained by parsing the RTL design file, wherein the original netlist is a circuit-level netlist. Optionally, the split parameter is used to realize the split control of the original netlist, which may include the total number N of subnetlists obtained by splitting, that is, the FPGA synthesis tool splits the original netlist to obtain N subnets In the tabl...

Embodiment 2

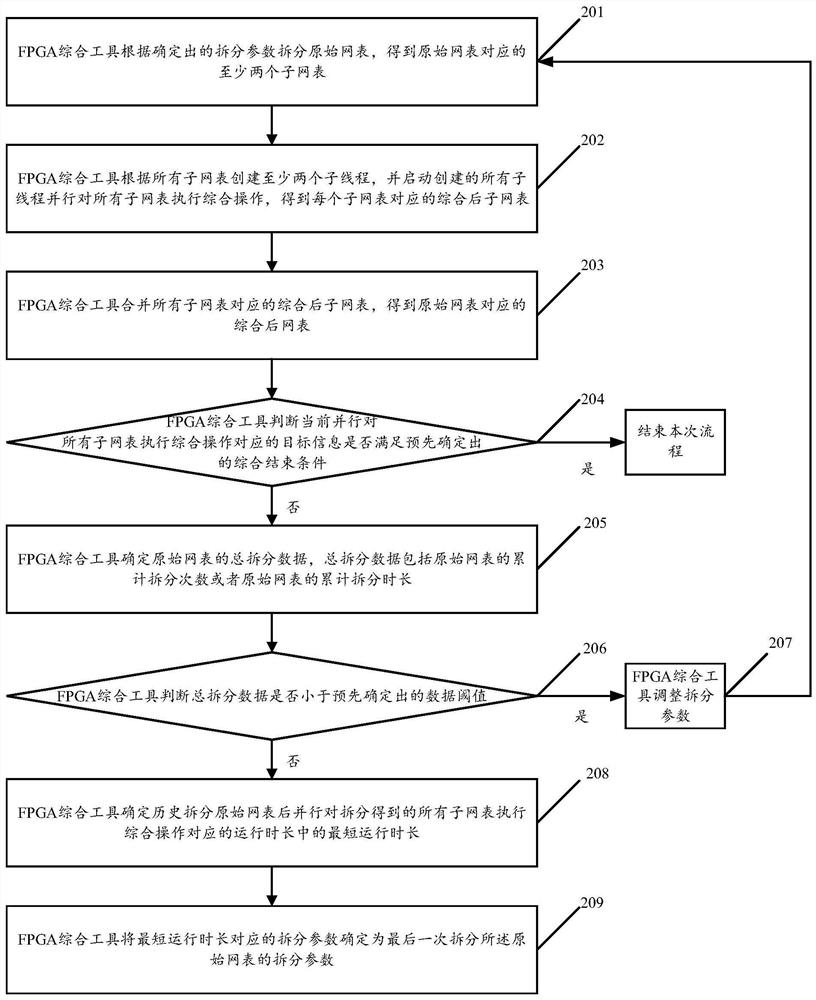

[0131] see image 3 , image 3 It is a schematic flowchart of another multi-thread synthesis method disclosed in the embodiment of the present invention. in, image 3 The described method can be applied to an FPGA synthesis tool, which is not limited in the embodiment of the present invention. Such as image 3 As shown, the method may include the following operations:

[0132] 201. The FPGA synthesis tool splits the original netlist according to the determined split parameters to obtain at least two subnetlists corresponding to the original netlist.

[0133] 202. The FPGA synthesis tool creates at least two sub-threads according to all sub-netlists, and starts all created sub-threads to perform synthesis operations on all sub-netlists in parallel to obtain a synthesized sub-netlist corresponding to each sub-netlist.

[0134] 203. The FPGA synthesis tool merges the synthesized subnetlists corresponding to all the subnetlists to obtain the synthesized netlist corresponding ...

Embodiment 3

[0168] see Figure 4 , Figure 4 It is a schematic structural diagram of a multi-thread synthesis device disclosed in an embodiment of the present invention. in, Figure 4 The described multi-thread synthesis device can be applied to an FPGA synthesis tool, which is not limited in the embodiment of the present invention. Such as Figure 4 As shown, the multi-thread synthesis device may include:

[0169] The splitting module 301 is configured to split the original netlist according to the determined splitting parameters to obtain at least two subnetlists corresponding to the original netlist.

[0170] The creating module 302 is configured to create at least two sub-threads according to all subnet lists.

[0171] The parallel synthesis module 303 is configured to start all the created sub-threads to perform synthesis operations on all subnets in parallel to obtain the synthesized subnet corresponding to each subnet.

[0172] The merging module 304 is configured to merge th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More