Memory Array And Method for Forming A Memory Array Comprising Strings Of Memory Cells

A technology of memory cells and memory arrays, which is applied in the field of memory arrays and can solve the problems of charge consumption and disadvantages

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

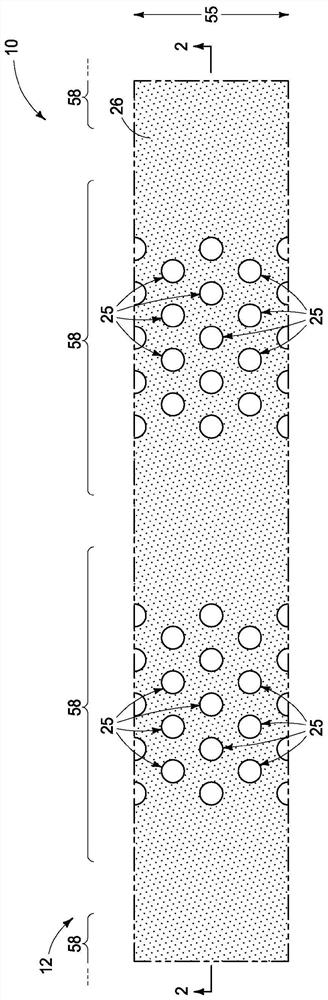

[0017] Embodiments of the invention encompass methods for forming memory arrays including strings of memory cells, such as NAND arrays or arrays of other memory cells with under-array peripheral control circuitry (eg, under-array CMOS). Embodiments of the invention encompass so-called "gate-last" or "replacement gate" processing, so-called "gate-first" processing, and other processes, whether existing or developed in the future, that are independent of the formation time of transistor gates. Embodiments of the invention also cover memory arrays (eg, NAND architectures) that are independent of fabrication methods. See what can be considered as "rear gate" or "replacement gate" treatment Figures 1 to 19 To describe the first example method embodiment.

[0018] figure 1 and 2 A construction 10 is shown having an array or array region 12 in which vertically extending strings of transistors and / or memory cells are to be formed. Construction 10 includes a base substrate 11 havi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com