System and method for transparent transmission of as6802 synchronization frame in tte switch

An AS6802, transparent transmission technology, which is applied in the field of AS6802 synchronous frame transparent transmission system, can solve the problems of increased delay, inability to synchronize, and increased delay of synchronous frame transmission, so as to reduce transmission delay, avoid data loss, and reduce retention time Reduced effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0131] The purpose of the present invention is to provide a device and method for transparent transmission of AS6802 synchronization frames in a TTE switch, aiming at the deficiencies of the prior art.

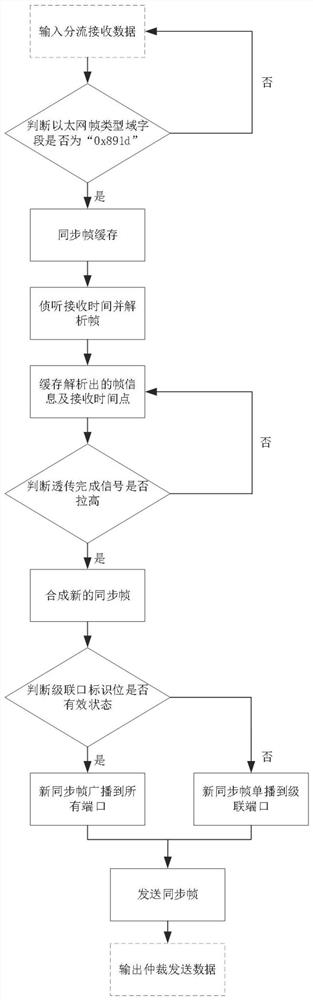

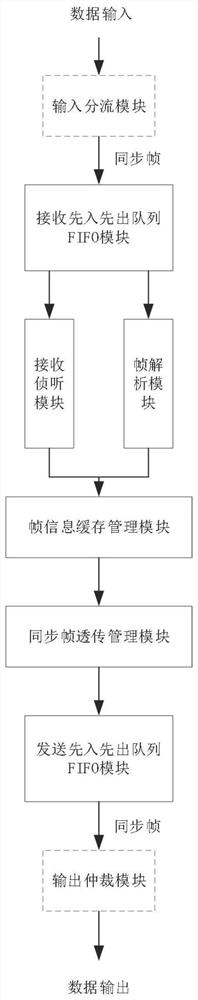

[0132] In order to achieve the above purpose, the idea of the present invention is: the programmable logic chip FPGA implements a multi-port time-triggered Ethernet switch, and the device is mainly used for transparent transmission of AS6802 synchronization frames in the TTE network. Listen to the synchronization frames passing through each port of the switch to obtain the receiving time point, and perform frame analysis on the received synchronization frames to obtain all frame information of the synchronization frames, including: destination address, source address, integration period, member vector, Sync priority, sync domain, frame type, and transparent clock value, store all frame information in registers. Then identify the identification bit of the cascade port, synthe...

Embodiment 2

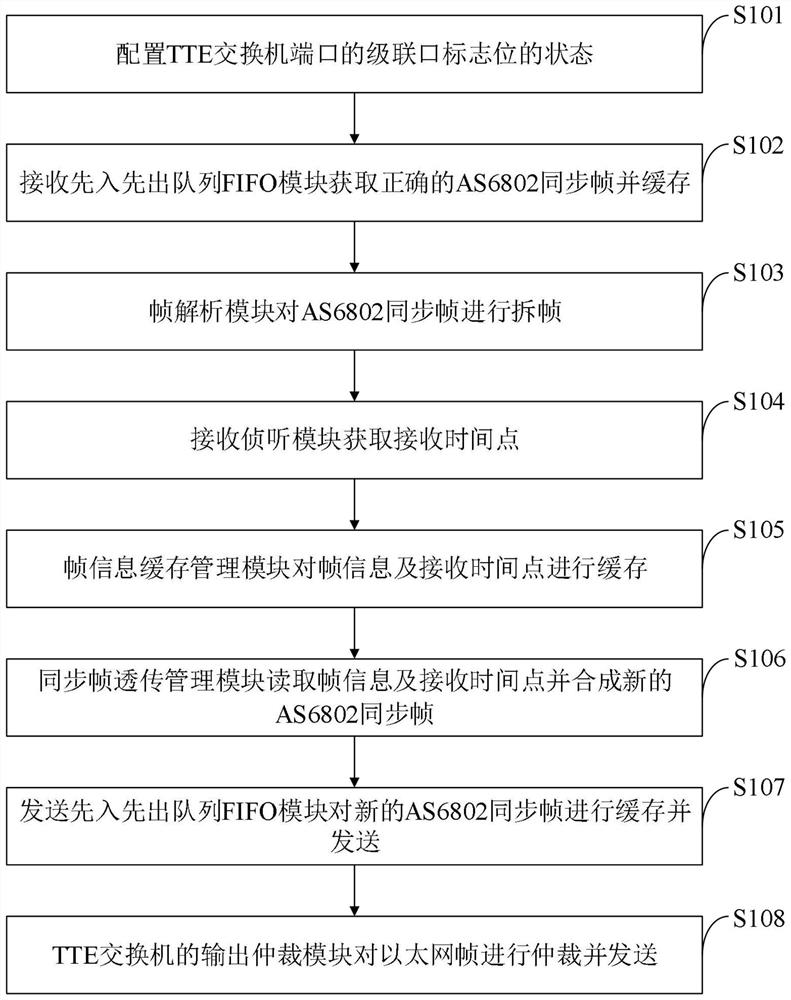

[0164] The transparent transmission method of the AS6802 synchronization frame in the TTE switch provided by the embodiment of the present invention includes the following steps:

[0165] (1) Configure the status of the cascade port flag bit of the TTE switch port:

[0166] Suppose the TTE switch includes P ports, one of which is a cascading port, and the remaining P-1 ports are non-cascading ports. The flags of the cascading ports are valid, and the flags of the non-cascading ports are invalid. P≥2;

[0167] (2) Receive the first-in-first-out queue FIFO module to obtain the correct AS6802 synchronization frame and buffer it:

[0168] (2a) The synchronization frame receiving module receives N consecutive AS6802 synchronization frames A output by the input distribution module of the TTE switch, A={A i }, where A i Indicates the i-th AS6802 synchronization frame, i∈[1,N], N≥2;

[0169] (2b) Cyclic redundancy check module for each A received by the synchronization frame recei...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More