Gate voltage modulation dynamic source region socket tunneling field effect transistor and preparation method thereof

A technology of tunneling field effect and source region, which is applied in the direction of diodes, semiconductor/solid-state device manufacturing, semiconductor devices, etc., and can solve the problems of carbon nanotube-based graphene-based difficulties, small tunneling probability, and weakening

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

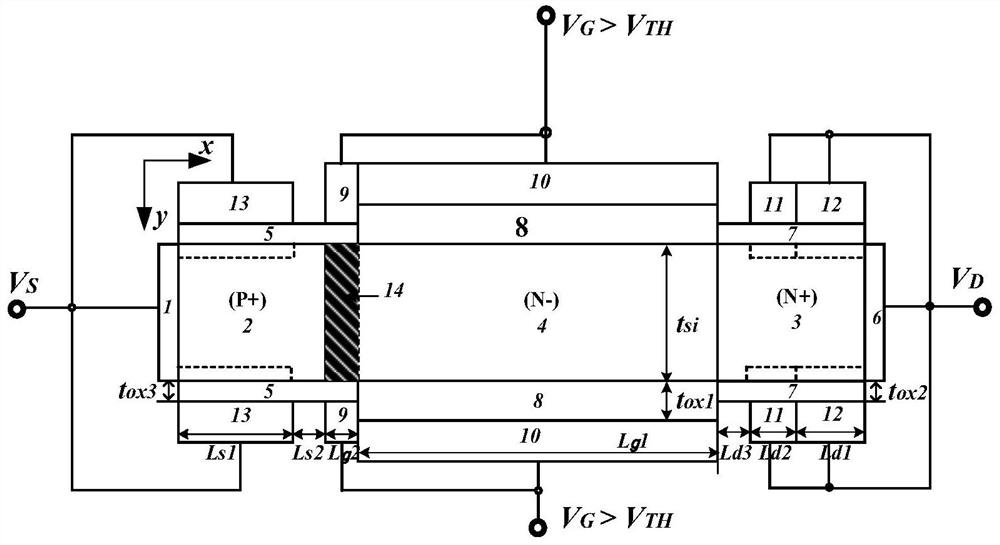

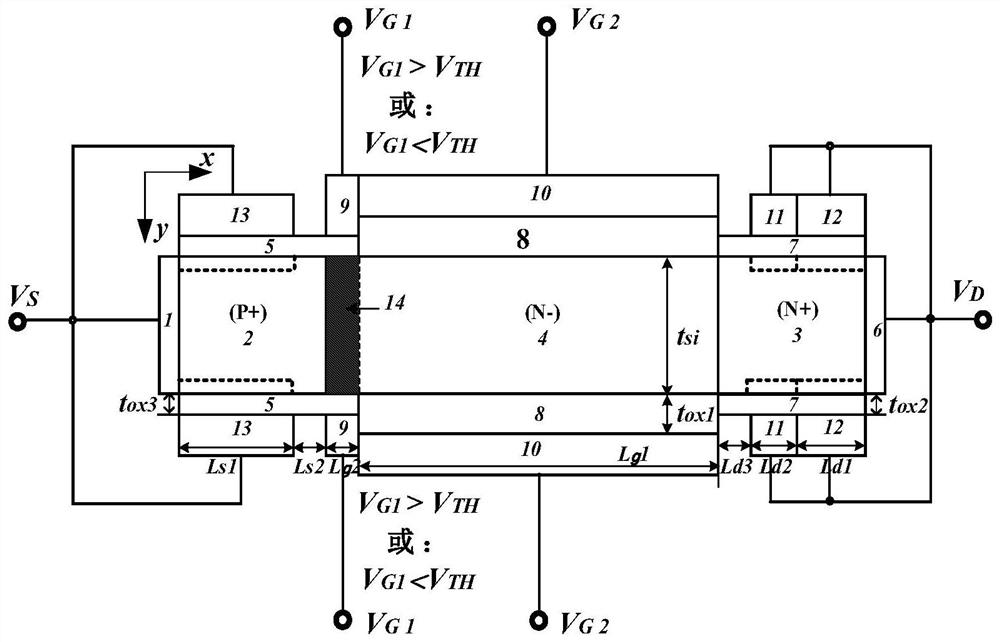

[0056] The invention discloses a tunneling field effect transistor with gate voltage modulation dynamic source region pocket structure and its preparation method. The field effect transistor uses transverse tunneling as the main tunneling mechanism, and the whole is based on longitudinal double-gate ultra-thin body lightly doped tunneling Field effect tube structure (DG-TFET).

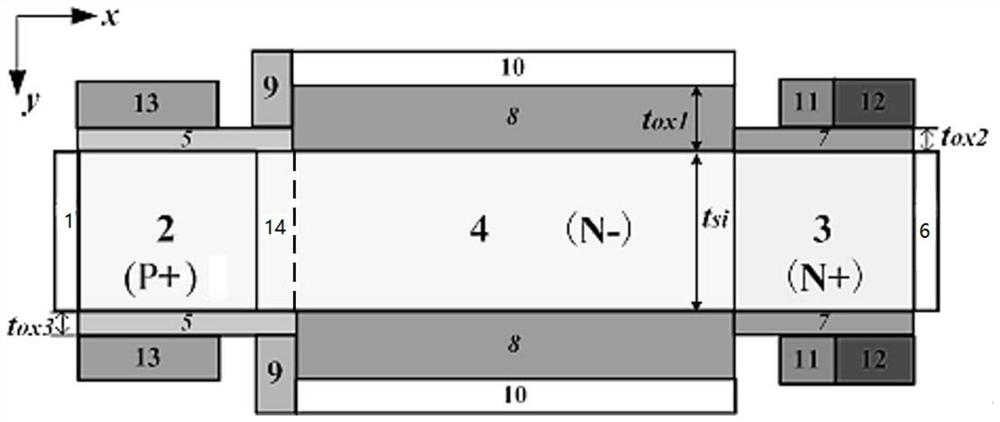

[0057] Such as figure 1 As shown, it includes a source region 2, a body region 4 and a drain region 3 arranged in sequence along the lateral direction, and a source region pocket region 14 is formed in the body region 4 close to the interface region of the source region 2; the upper and lower surfaces of the body region 4 are respectively arranged The body region oxide layer 8, the upper and lower surfaces of the bod...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More